Dinamik frekansa dayalı en uygun çip alanı güç tüketimi tasarımı

Tüketici elektroniğinin, ağ ürünlerinin ve diğer pazarların hızla gelişmesiyle birlikte, düşük maliyetli, yüksek hızlı, düşük güçlü ve çok işlevli gömülü sistemlere olan talep, daha karmaşık işlevler elde etmek için entegre devre tasarımı endüstrisine daha büyük zorluklar getirdi. Şirketin tek yongalarının entegrasyonu gitgide artıyor ve tek yongaların güç tüketimi ve maliyeti de artıyor. Şu anda, çipin alanı ve güç tüketimi, çip performansının daha da iyileştirilmesini kısıtlamaktadır.Alan optimizasyonu ve düşük güç tasarımı, modern çip tasarımında giderek daha önemli hale gelmektedir.Frekans, güç tüketimi ve alan (PPA) göstergeleri zaten entegre devre tasarımının önemli göstergelerinden biridir. Birincisi, tasarımcılar genellikle EDA araçlarını bant çıkarmadan önce yonganın alanını ve güç tüketimini doğru bir şekilde tahmin etmek için kullanırlar.Çipin alanı ve güç tüketimi, tasarım gereksinimlerinin karşılanıp karşılanmayacağını değerlendirmek için önemli parametrelerden biridir.

Entegre devre tasarımı, tasarım soyutlama seviyesine göre sistem algoritma seviyesi, kayıt transfer seviyesi, mantık devre seviyesi ve transistör seviyesi olarak ayrılabilir. Ultra-derin mikron altı teknoloji altında entegre devrelerin tasarımında, alan optimizasyonu ve düşük güç tasarımı için transistör seviyesinden sistem algoritma seviyesine kadar her seviyede ilgili araştırmalar vardır.Soyutlama seviyesi ne kadar yüksekse, optimizasyon etkisi o kadar belirgin olur. Literatür, dijital entegre devreler, yazmaç seviyesi, transistör seviyesi ve diğer seviyeler için mevcut ana akım düşük güç tasarım yöntemlerini ayrıntılı olarak açıklamaktadır. Bunların arasında, sistem algoritması seviyesi, sistem düzeyinde güç tüketimini azaltmak için temel olarak yazılım ve donanım ortak tasarımını, güç yönetimini ve diğer yöntemleri benimser. Kayıt aktarım aşaması, sinyal geçişlerinin sayısını azaltmak için temel olarak kodlama tekniklerini, geçitli saatleri ve diğer teknolojileri kullanır. Mantık devre seviyesi ve transistör seviyesi, temel olarak mantıksal ifade tasarımına, gelişmiş üretim teknolojisine ve düşük güç tasarımı elde etmek için diğer yöntemlere dayanmaktadır. Şu anda, çip alanının azaltılması, hedefe ulaşmak için esas olarak yeni teknolojiyi ve mantık devresi tasarımını benimser Literatür, taşıma seçici mantık devre tasarımından gelen çip alanını azaltır. Bu makale, alanı ve düşük güç tasarımını optimize etmek için sistem seviyesinden başarılı bir şekilde bantlanmış bir SoC çip projesine dayanmaktadır.

1 Güç tüketimi ve alan analizi

Çipin güç tüketimi temel olarak statik güç tüketimini ve dinamik güç tüketimini içerir.Geçit seviyesinde SoC güç tüketiminin hesaplanması formül (1) olarak tahmin edilir:

Statik güç tüketimi (Hücre Kaçak Gücü) esas olarak kaçak akım güç tüketimi ve CMOS devre yapısının neden olduğu yan devrenin güç tüketimidir. Kaçak akım güç tüketimi proses kütüphanesinden bulunabilir Proje tasarlandıktan sonra, statik güç tüketimi PLeakageTotal temel olarak hesaplanabilir. Dinamik güç tüketimi ile karşılaştırıldığında, statik güç tüketiminin entegre devre tasarımı üzerinde çok az etkisi vardır ve göz ardı edilebilir.Genel olarak, düşük güç tüketimi tasarımları temelde dinamik güç tüketimini hedef alır.

Dinamik güç tüketimi, temel olarak kısa devre akımı (Hücre Dahili Gücü) ve anahtarlamalı kapasitörden (Net Anahtarlama Gücü) oluşur. PSwitching, birim geçit cihazının i çıkış terminalindeki yük kapasitansını şarj etme ve boşaltma güç tüketimidir, TR (i), i hattının sinyal geçiş hızıdır, yani sinyal birim zaman başına düşükten yükseğe ve yüksekten düşüğe doğru değişir. Yassı geçiş sayısı; CLyük (i), kapı cihazının çıkış terminali i'nin hat yüklü kapasitansıdır.

PInternal, ünite kapı cihazı kondansatörünün şarjı ve deşarjı ile kapama ve açma işlemi sırasında P transistörünün ve N transistörünün kısa devresinin oluşturduğu güç tüketimidir. TR (z), cihazın çıkışındaki sinyal geçiş oranını temsil eder. Denklem (3) ve (4) den dinamik güç tüketiminin doğrudan sinyal sıçramaları ve kapasitanslarla ilişkili olduğu ve çalışma frekansının doğrudan sinyal sıçramalarını ve kondansatör şarj ve deşarjını etkilediği görülmektedir.Çalışma frekansının doğrudan PS anahtarlama ile ilgili olduğu görülebilir, PInternal güçlü bir korelasyondur.

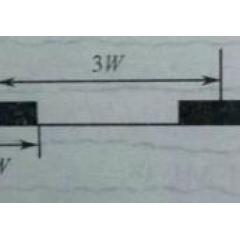

Çip alanı, bir kombinasyonel mantık alanı (Birleşik Alan), bir tampon ve çevirici alanı (Buf / Inv Alanı) ve bir kombinasyon olmayan mantık alanı (Kombinasyonel Olmayan Alan) içerir. Ultra-derin mikron altı işlem koşullarında, mantık kombinasyon devresi, mantık işlemlerini uygulamak için yarı iletken anahtarlama elemanlarının açma ve kapama çalışma özelliklerini kullanır. Kapı devresinin farklı frekanslarda anahtarlama prensibini kullanarak, mantık yolunun farklı zaman gecikmelerini optimize etmek gibi alanı azaltmak için saat sinyalini ayarlayın ve alan optimizasyonu elde etmek için farklı tetikleme cihazlarının farklı gecikmelerini rasyonel olarak planlayın.

Alanın boyutu çipin maliyeti ile, güç tüketimi seviyesi ise çipin performansı ile ilgilidir. Fonksiyonel tasarım gereksinimlerinin karşılanması durumunda, alan ne kadar küçükse, maliyet o kadar düşük, güç tüketimi o kadar düşük ve performans o kadar istikrarlı. Alan ve güç tüketiminin ölçülmesi yaygın bir yöntemdir Bu makale, tamamlanmış tasarım projesini hedefler, performansını değiştirmez, alanı daha kapsamlı bir şekilde nasıl optimize edeceğinize ve dinamik frekans yoluyla güç tüketimini nasıl azaltacağınıza odaklanır.

2 Dinamik frekans kapalı döngü tasarımı

Sistem düzeyinde yonga tasarımı için, sistem tasarımının belirli işlevsel gereksinimlerine göre, genellikle yonganın sürecini, çalışma sıklığını ve diğer parametre gereksinimlerini onaylayın; ikinci olarak, proje tasarım gereksinimlerine dayalı kısıtlamaları tasarlayın ve kısıtlamalara dayalı olarak EDA araçlarında simülasyon doğrulaması gerçekleştirin; Son olarak doğru güç tüketimi ve alan tahmini ile tasarım tamamlanmış olup, tasarım süreci Şekil 1'de gösterilmiştir. Bunlar arasında mühendis, tasarım değerine yalnızca belirli bir yanıt vermiş ve birden fazla simülasyon sonucu ile çalışma frekansını dinamik olarak ayarlamamıştır.Tasarımın çoğu mühendisin deneyimine dayanmaktadır.Yaklaşık çalışma frekansı deneyim değerine göre verilir ve EDA Şekil 1'deki tasarım sürecine göre geçirilir. Bir kez daha, araç doğru simülasyon gerçekleştirir ve tasarımı uygular. Şekil 1'de gösterilen tasarım akış şeması, bir açık döngü tasarımı olarak kabul edilebilir. Bu tasarımın avantajı, iş akışının basit olması, ancak optimum frekans seçim doğruluğunun yüksek olmaması ve sapmaları otomatik olarak düzeltme yeteneğinin zayıf olmasıdır Deneyimsiz mühendisler için, yüksek güç tüketimi ve alan riski vardır.

Formül (1) 'den, her bir düğümün sinyal atlama hızının çipin güç tüketimini belirlediği ve sinyal atlama hızının saat kaynağı tarafından belirlendiği görülmektedir.Yukarıdaki analize göre, çip alanı doğrudan çalışma frekansı ile ilişkilidir. Bu makale orijinal proje tasarımını değiştirmez.Orijinal açık döngü tasarım sürecinde (Şekil 1), geri bildirim ve eğitim kanalları oluşturulur ve dinamik frekans, dinamik frekans kapalı döngü tasarımını gerçekleştirmek için ayar parametresidir (Şekil 2'de gösterildiği gibi). Dinamik frekans kapalı döngü tasarımı, çalışma frekanslarında karşılık gelen güç tüketimi ve alan verilerinin birden çok seti aracılığıyla geri bildirim ve eğitim sağlar, çalışma frekansı, güç tüketimi ve alanın matematiksel bir modelini oluşturur ve optimum olanı hesaplamak için alan ve güç tüketiminin iki önemli göstergesini kapsamlı bir şekilde ele alır. Çalışma frekansı, alanı optimize etmek ve güç tüketimini azaltmak için tasarlanmıştır.

Dinamik frekans kapalı döngü tasarım süreci Şekil 3'te gösterilmektedir. Ana adımlar aşağıdaki gibidir:

(1) Proje tasarım gereksinimleri. Projenin işlevsel tasarım gereksinimlerine göre, zamanlama gibi kısıtlamaları derleyin ve hedef frekansın etkili aralığını onaylayın.

(2) Deneysel simülasyon. Bir komut dosyası yazın, frekansın başlangıç değerini ayarlayın, sentezlemek için EDA aracını kullanın ve Zamanlama, Alan ve Güç raporlarını verin.

(3) Veri kaydı. Çip alanı ve güç tüketimi gibi ilgili parametreleri, farklı çalışma frekanslarının birden çok grubu altında kaydedin.

(4) Veri görüntüleme. İşlevi değiştirmeden tutun ve kısıtlamaları karşılayan yonga alanı ve yonga güç tüketiminin tüm belirli parametrelerini filtreleyin.

(5) Bir model oluşturun. Kaydedilen verilere göre sırasıyla alan ve frekans, güç tüketimi ve frekansın matematiksel modelleri oluşturulmuştur.

(6) En uygun çözümü arayın. İki takım matematiksel modeli entegre edin ve çalışma frekansı için en uygun çözümü bulun.

Dinamik frekans kapalı döngü tasarımına dayanan, açık döngü tasarımına kıyasla, dinamik güç kapalı döngü tasarımı yüksek hassasiyete sahiptir, alan optimizasyonunu sağlamak ve güç tüketimini azaltmak için en uygun çalışma frekansını seçer; ikincisi, son derece uyarlanabilir ve kapalı döngü tasarımı, sahip olmak zorunda kalmadan farklı projelere uyarlanabilir Deneyimli mühendisler, proje deneme yanılma maliyetlerini etkili bir şekilde azaltabilir ve proje tasarım verimliliğini artırabilir. Bu makale, başarılı bir şekilde bantlanmış 0.11 m işlemli bir SoC çipine dayanmaktadır.Proje tasarımının çalışma frekansı 50 MHz'dir ve gerçek işlevsel gereksinim, 36 MHz'lik en düşük güç tüketimidir.Bu yöntem, alanı daha da optimize etmek ve bu çip üzerindeki gücü azaltmak için kullanılır. Tüketim tasarımı.

3 Deneysel simülasyon

Dinamik güç tüketiminin kapalı döngü tasarımına göre, kısıtlama koşullarını geçen yonga alanı ve yonga güç tüketimi verileri taranır ve alan saat döngüsü ve güç tüketimi saat döngüsünün matematiksel modelleri, Şekil 4 ve Şekil 5'te gösterildiği gibi eğri uydurma yoluyla oluşturulur.

Bunlar arasında, Şekil 4'te oluşturulan çip alanı ve saat döngüsünün matematiksel modeli formül (5) 'de gösterilmektedir:

Saat periyodu t = 22 ms ve çalışma frekansı f = 1 / t = 45 MHz'nin bu tasarım için optimal çözümler olduğu hesaplama yoluyla bilinebilir. Tablo 1 ve Tablo 2 sırasıyla 45 MHz ve 50 MHz çalışma frekansında simülasyon testi ile kaydedilen çip alanı ve çip güç tüketimi verileridir.

Tablo 1 ve Tablo 2'ye göre, 45 MHz çalışma frekansı altındaki toplam yonga alanının, 50 MHz'lik orijinal çalışma frekansına kıyasla yaklaşık% 0,59 azaldığı, birleşik mantığın alanı% 1,17 azaldığı, tampon ve eviricinin alanı azaldığı görülmektedir. % 1.36 küçült. Çipin güç tüketimi, alan optimizasyonundan daha belirgindir. 45 MHz'lik bir çalışma frekansında çipin toplam güç tüketimi, 50 MHz'lik orijinal çalışma frekansına göre% 9,01 daha azdır. Kısa devre akımı güç tüketimi ve anahtar kapasitör güç tüketimi sırasıyla % 9.09 ve% 9.10 azalma.

4. Sonuç

Orijinal tasarımı değiştirmeden bu makale, alanı ve güç tüketimini daha da azaltmak için sistem düzeyinde dinamik güç kapalı döngü tasarımına dayanmaktadır.Veri toplama ve simülasyon analizi, bu makalede önerilen optimizasyon yöntemi tasarımının daha iyi optimize edilmiş alan ve güç tüketimi sağlayabileceğini göstermektedir. Gerçek mühendislikte belli bir referans değerine sahiptir.

Referanslar

ROY K, PRASAD S. Düşük güçlü CMOS VLSI devre tasarımı, Wiley, 2000.

Wang Guanjun, Zhou Yong, Zhao Ying, ve diğerleri VLSI devrelerinin düşük güç tasarımında araştırma ilerlemesi. Mikroelektronik, 2011, 41 (2): 279-284.

CHOURASIA A. Güç kısıtlı ortamlarda taşıma seçimi mantığını kullanan alan için optimize edilmiş toplayıcı tasarımı International Journal of Engineering Innovation and Research, 2017, 6 (1): 48-50.

MACII E, ZAFALON R.Düşük güç EDA teknolojileri: en son teknoloji ve ötesi.2006 Gelişmiş Sinyal İşleme, İletişim için Devre ve Sistem Tasarım Teknikleri IEEE, 2006: 3-43.

Chang Xiaotao, Zhang Zhimin, Wang Xin. Saat ağacı gücü ön ekstraksiyonuna dayalı SoC güç tüketimi tahmin yöntemi Bilgisayar Mühendisliği, 2006, 32 (1): 234-236.

NEVES J L, FRIEDMAN E G. Proses varyasyonlarına toleranslı optimum saat çarpıklığı programlaması. 33rd Design Automation Conference Proceedings, 1996.

yazar bilgileri:

Zhan İsveç 1, 2, Yang Jiachang 1, 2

(1. Foshan Xinzhu Microelectronics Co., Ltd., Foshan 528225, Guangdong; 2. Otomasyon Okulu, Guangdong Teknoloji Üniversitesi, Guangzhou 510006, Guangdong)

-

- Ali "Cat Mall" adlı bir alışveriş merkezi açmak istiyor; Çin'in 4000 km / s azami hız ile süper hızlı tren planı | Lei Feng Morning Post

-

- Gece okuma Hırsızın ayakları çok kokmuştu, ancak hırsızlık yerinde yakalanamadı Odada çömelmiş 70 pişmiş toprak savaşçı ve at vardı ve adam sabahın üçünde uyumaya cesaret edemedi

-

- "The Lightning Rod for Movie Watch", sevimli büyük boğa sırada ve ilk animasyon filmi onu yılın başında kilitleyecek

-

- Bu arabanın askeri bir geçmişi var ve mal çekip mal satabiliyor. Sadece 90.000'e satılıyor. Çinlilerle Harvard'dan daha gurur duyuyor