"Akademik makale" Bir hibrit yüksek dinamik aralık AGC algoritması ve FPGA uygulaması

Özet:

Alıcının uygulamasına bağlı olarak, bir hibrit yüksek dinamik aralık AGC algoritması önerilmektedir. Algoritma, radyo frekansı ileri besleme ve orta frekans geri besleme algoritmalarından oluşur ve sahada programlanabilir kapı dizisi yardımıyla gerçekleştirilir. Bu algoritmanın kontrolü altında, çekirdek bileşenler olarak radyo frekansı anahtarları, sayısal kontrollü zayıflatıcılar, dedektörler ve değişken kazanç yükselteçleri kullanılarak 110 dB giriş dinamik aralığı, -100 dBm hassasiyet ve -19 dBm çıkış gücü ile otomatik kazanç gerçekleştirilmektedir. Kontrol döngüsü.

Çince alıntı biçimi: Zhao Xiaoteng, Yin Junjian, Zhang Jintao, et al. Hibrit yüksek dinamik aralık AGC algoritması ve FPGA uygulaması Elektronik Teknoloji Uygulaması, 2017, 43 (12): 76-80.

İngilizce alıntı biçimi: Zhao Xiaoteng, Yin Junjian, Zhang Jintao, vd.Yüksek dinamik aralık ve FPGA'da uygulama için bir hibrit AGC algoritması.Elektronik Tekniğin Uygulanması, 2017, 43 (12): 76-80.

0 Önsöz

Çoklu yol zayıflaması gibi faktörlere bağlı olarak, alıcının anten ucundaki sinyal gücü 60 dB'den fazla dalgalanabilir. Ara frekans ADC'nin sabit dinamik aralığının bu tür büyük dinamik sinyalleri doğru bir şekilde örneklemesi zordur Temel bandın doğru şekilde demodüle edilmesini ve kodunun çözülmesini sağlamak için, alıcının kazancını giriş sinyalinin gücüne göre otomatik olarak ayarlaması ve böylece sonraki aşama için nispeten sabit bir çıktı sağlaması gerekir. Bu işlev, otomatik kazanç kontrolü (Otomatik Kazanç Kontrolü, AGC) döngüsü tarafından gerçekleştirilir.

Yaygın olarak kullanılan AGC döngüleri üç türe ayrılır: ileri beslemeli AGC, geri beslemeli AGC ve hibrit AGC. İleri beslemeli AGC, açık döngü kontrolü ile temsil edilir, giriş sinyal gücü algılanır ve kazanç ayarı için işlenir; geri besleme AGC kapalı döngü kontrolüdür, çıkış gücü bir referans değer ile karşılaştırılır ve güç hatası elde edilir. Kazancın boyutunu kontrol edin. Literatür çalışmaları, ileri beslemeli AGC'nin daha hızlı yanıt hızına sahip olduğunu ve algoritmasının nispeten basit olduğunu ve daha az kaynak kapladığını, bu nedenle yaygın olarak kullanıldığını göstermiştir. Bununla birlikte, hassas yanıt karakteristikleri nedeniyle, ileri beslemeli AGC, devre parametrelerinin dalgalanması nedeniyle yanlış ayarlamaya eğilimlidir. Geri bildirim AGC daha kararlı kontrol gerçekleştirebilir, ancak kapalı döngü yapısı nedeniyle döngü parametrelerinin dikkatlice onaylanması gerekir ve bu da tasarıma bazı zorluklar getirir. Hybrid AGC, ileri besleme ve geri bildirimin bir kombinasyonudur ve her ikisinin özelliklerine sahiptir.

1 Hibrit AGC döngüsü

Alıcıda kullanılan hibrit AGC döngüsü, bir radyo frekansı ileri beslemeli AGC devresinden ve bir ara frekans geri besleme AGC devresinden oluşur. Şekil 1'de gösterildiği gibi, antenin aldığı sinyal belirli bir kuplaj katsayısı ile radyo frekansı dedektörüne beslenir.Dedektörün çıkış voltajı ADC ile dijital bir miktara dönüştürülür ve daha sonra FPGA tarafından işlenerek sinyal yolu üzerindeki tek kutuplu çift atışlı anahtar ve sayısal kontrol kontrol edilir. Radyo frekansı bölümünün kazancını kontrol etmek için zayıflatıcı. Bunlar arasında, Düşük Gürültülü Amplifikatör (LNA) 22 dB'lik bir kazanıma ve zayıflatma ağının -10 dB'lik bir kazancı vardır. RF sinyali, ara frekans giriş sinyali IFIN'i elde etmek için yerel osilatör ile karıştırılır.IFIN, aynı iki aşamalı değişken kazanç amplifikatörü (Değişken Kazanç Amplifikatörü, VGA) ile güçlendirildikten sonra, uygun seviye, tespit etmek için kuplör aracılığıyla ara frekans detektörüne beslenir. Dönüştürücünün çıkış voltajı VIFDET'i ADC tarafından dijital bir miktara dönüştürülür ve daha sonra veriler FPGA tarafından işlenir İşlemin sonucu DAC'ın çıkış voltajını belirler ve böylece VGA'nın kazancını kontrol eder. Bunların arasında, IFOUT, ara frekans çıkış sinyalini temsil eder ve VG, VGA'nın kontrol voltajıdır.

2 AGC algoritması

AGC algoritmasını tanıtmadan önce, ilk olarak döngünün tasarım indeksini açıklayın. Girişte belirtildiği gibi, tasarlanan AGC algoritmasının iki farklı giriş sinyalinin gereksinimlerini karşılaması gerekir. Sabit zarf sinyalleri için, AGC tek kontrol süresi 50 s'den azdır, giriş dinamik aralığı -95 dBm ~ 5 dBm'den az değildir ve çıkış gücü -19 dBm'dir; sabit olmayan zarf sinyalleri için, çıkış sinyali zarfı bozulmaz.

AGC döngü indeksine göre, Şekil 2'de gösterilen genel algoritma, bu sistemde giriş sinyalinin zarf özelliklerinin dışarıdan öğrenilebileceğine dikkat edilerek tasarlanmıştır. Döngü başlatıldığında, önce giriş sinyalinin sabit bir zarf sinyali olup olmadığına karar verilir, eğer öyleyse, hızlı AGC algoritması yürütülür, aksi takdirde yavaş AGC algoritması çalıştırılır ve sıra, önce radyo frekansı ve ardından ara frekanstır. Ara frekans AGC algoritması yürütüldükten sonra, belirli bir zaman aralığından sonra tekrar radyo frekansı AGC'ye geri döner ve bu böyle devam eder.

RF ileri beslemeli AGC algoritması Şekil 3'te gösterilmektedir. İlk olarak, ADC'nin RF kanal örneklemesi yapılandırılır ve örnekleme frekansı, giriş sinyalinin zarf özelliklerine göre belirlenir. Bağlayıcının ve radyo frekansı detektörünün (formül (1)) özelliklerine göre, ortalama seviye karşılık gelen giriş gücüne dönüştürülür. LNA ve dijital zayıflatıcının uygun durumunu belirlemek için algılanan giriş gücü üzerinde koşullu yargıda bulunun. Bu süre belirlenen durum mevcut devre durumu ile tutarlıysa, konfigürasyon fazını atlayarak radyo frekansı AGC'yi sonlandırın, aksi takdirde devre belirlenen duruma göre yapılandırılır ve sona erer.

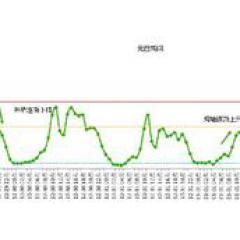

Radyo frekansı AGC algoritmasının simülasyon sonucu Şekil 4'te gösterilmektedir. Radyo frekansı giriş gücü -95 dBm'den 5 dBm'ye değiştiğinde, radyo frekansı çıkış gücü, giriş sinyalinin dalgalanma aralığını 100 dB'den 64.8 dB'ye düşürme aralığında değişir.

Radyo frekansı ayarlamasına dayalı olarak, IF geri besleme tipi AGC kazancın sürekli ve hassas kontrolünü gerçekleştirir Algoritma Şekil 5'te gösterilmiştir. İlk olarak VGA'nın kontrol voltajı VGint'e bir başlangıç değeri atanır ve ardından giriş sinyalinin zarf özelliklerine göre IF kanalının örnekleme süreleri belirlenir. Ve sabit olmayan zarf girdisi altında ortalama VIFDET değerini hesaplayın, iki örnek arasında T1 saniyelik bir zaman aralığı vardır. IF AGC döngüsündeki VGA kazancı ve kontrol voltajı VG, normal çalışma koşullarında denklem (2) 'de gösterilen doğrusal ilişkiye uygundur, burada kazanç birimi dB ve kontrol voltajı birimi V'dir.

Kullanılan VGA cihazının özelliklerine göre, formül (2) 'de k 50, b -5 alır. IF detektör çıkış voltajı VIFDET ve IF çıkış gücü PIFOUT, voltaj biriminin V olduğu ve tespit edilen gücün biriminin dBm olduğu normal çalışma alanındaki denklem (3) 'ün doğrusal ilişkisine uygundur. Dedektör ve kuplörün özelliklerine göre:

Formül (3) 'te k10,05, b1 ise 2,575 olarak alınmıştır.

IF AGC döngüsünde, eğer PIFIN IF giriş gücünü temsil etmek için kullanılırsa ve PIFOUT IF çıkış gücü ise, tasarlanan döngü hedefi: PMIN olduğunda < PIFIN < PMAX'ta, PIFOUT hedef güç PAIM'de kalır. Belirli bir andaki çıkış gücünün PNOW, VGA kontrol voltajının VG1 ve ara frekans dedektörünün çıkış voltajının VIFDET olduğu varsayılırsa, bir ayar yapıldıktan sonra VGA kontrol voltajı VG2 olarak değiştirilmeli ve çıkış gücü PAIM'e ulaşmalıdır. (2) formülüne göre, Denklem (3) ve kontrol hedefi, denklem (4) 'ün kontrol algoritmasını alabilir; burada NSTAGE, VGA'nın aşama sayısını temsil eder, bu makalede 2'dir ve PAIM -19 dBm'dir.

Kontrol hedefi ve formül (4) 'te gösterilen ilişkiye dayalı olarak, Şekil 5'teki değerlendirme koşulu ve kontrol voltajı VG'nin hesaplama formülü verilir; burada VGint, VGA'nın mevcut kontrol voltajıdır, Max maksimum değer çalışmasını temsil eder ve Min, minimum değeri temsil eder. Operasyon. Dedektör, yalnızca belirli bir aralıkta denklem (3) ilişkisini karşıladığından, güvenilir bir algılama voltaj aralığı belirlemek gerekir: Bu aralıkta, tespit voltajı VIFDET'in gerçek çıkış gücünü temsil ettiği kabul edilir.Bu anda AGC kontrolü, denklem (4) 'de açıklanan yönteme göre gerçekleştirilir; VIFDET < 0.375 V'de çıkış gücünün küçük olduğu kabul edilir ve kazancı artırmak için VGA'nın kontrol voltajının artırılması gerekir, böylece VIFDET güven aralığı içinde olur ve ardından değerlendirme tekrar yapılır; VIFDET > 2,75 V'ta, önce kazancı azaltmak için VGA'nın kontrol voltajını düşürmek ve ardından tekrar yargılamak gerekir.

Ara frekans AGC algoritmasının simülasyon sonucu Şekil 6'da gösterilmektedir. Apsis, AGC yürütme sayısıdır. IF giriş sinyalinin güç aralığı -100 dBm ila -10 dBm'dir. Giriş sinyali gücü dBm cinsinden olduğunda, VGA kontrol voltajı VG giriş gücünün değişmesiyle değişebilir, çıkış gücü -19 dBm'de kalır ve VIFDET ve PIFOUT eşzamanlı olarak değişerek döngünün güç kontrol hedefine ulaşır.

3 Algoritma uygulaması ve testi

Bölüm 2'ye göre, hibrit AGC algoritması Xilinx Spartan 3E serisi FGPA üzerinde uygulanmaktadır. Algoritma tarafından kontrol edilen ana bileşenler arasında ADC, RF anahtarı, dijital zayıflatıcı ve DAC bulunur. Bunlar arasında, radyo frekansı ve ara frekans bölümü 10 bitlik, 4 kanallı analogdan dijitale dönüştürücü ADS7954'ü paylaşır; tek kutuplu çift konumlu anahtarın durumu, FPGA'nın tek bitli yüksek ve düşük seviyeli çıkışı tarafından kontrol edilir; dijital olarak kontrol edilen zayıflatıcı, 6 bit ve 0,5 dB adımlarla RFSA2644'tür. yonga. IF VGA'nın kontrol voltajı 12 bit DAC tarafından sağlanır. ADC kanallarının anahtarlanması ve örneklenmesi, sayısal olarak kontrol edilen zayıflatıcı zayıflatma değeri ve DAC'nin çıkış voltajının tümü, Seri Çevresel Arayüz (SPI) veriyolu aracılığıyla FPGA tarafından kontrol edilir. Dijital parçanın işlenmesini kolaylaştırmak için, önerilen algoritmadaki örnekleme zamanları N1, N2, N3 ve N4'ün tümü ikinin gücüne alınmıştır.

Modelsim'in farklı giriş uyarma koşulları altındaki fonksiyonel simülasyon sonuçları Şekil 7'de gösterilmektedir. Giriş sabit bir zarf sinyali olduğunda (Şekil 7 (a)), önce ADC RF kanalını yapılandırın, 4 RF kanal örneklemesi gerçekleştirin ve hesaplamadan sonra bir dijital zayıflatıcı yapılandırın. Yüksek giriş gücü nedeniyle, LNA her zaman kapanır ve ardından VGA kazancı önceden ayarlanır. Ardından, ADC'yi ara frekans kanalına geçecek, 16 ardışık örnekleme gerçekleştirecek ve son olarak DAC'yi uygun bir VGA kontrol voltajı verecek şekilde yapılandırın. Sabit zarf giriş sinyali altındaki tek AGC işlemi 41,73 s alır.

Giriş sabit olmayan bir zarf sinyali olduğunda (Şekil 7 (b)), RF AGC örneklemesi 64 kat olur ve orta frekans AGC hala 16 kez örnek alır, ancak örnekler arasına 6,68 s zaman aralığı eklenir ve toplam kontrol süresi 230,53 s'dir. . Bir osiloskop ile ölçülen zaman alanlı giriş ve çıkış dalga formları Şekil 8'de gösterilmektedir. Kanal 1 giriş sinüzoidal zarf sinyali, zarf periyodu 128 s ve kanal 2 ara frekans çıkış sinyalidir.Çıkış sinyal zarfının sağlam ve ortalama kaldığı gözlemlenebilir. Güç sabittir.

Giriş sabit bir zarf sinyali olduğunda, RF giriş gücünün değişmesiyle hibrit AGC döngüsündeki anahtar parametrelerin eğrisi Şekil 9'da gösterilmektedir. Şekil 9 (a) 'daki formül (1)' e göre takılan eğri, ölçülen eğri ile iyi bir uyum içindedir, Şekil 9 (b) 'deki VGA kontrol voltajı, radyo frekansı AGC algoritmasında tasarlanan 4 durum yargısı ile tutarlı olan üç sıçramayı gösterir; Şekil 9 (c) ve Şekil 9 (d), giriş sinyal gücü -100 dBm ~ 10 dBm olduğunda, tasarlanan AGC sisteminin çıktısının 110 dB dinamik aralıkla -19 dBm'de sürekli kontrol edilebildiğini göstermektedir. Son yıllarda önerilen AGC sisteminin dinamik aralık karşılaştırması Şekil 10'da gösterilmektedir. Karşılaştırma, bu çalışmada elde edilen dinamik aralığın belirli bir öncü olduğunu göstermektedir.

4. Sonuç

Giriş sinyalinin farklı zarf özelliklerine dayalı, ileri besleme ve geri besleme AGC'nin özelliklerini birleştiren ve alıcının donanım mimarisine dayanan bu makale, FPGA donanım platformunda uygulanan bir hibrit yüksek dinamik aralıklı AGC algoritması önermektedir. . Bu algoritmanın kontrolü altında, çekirdek bileşenler olarak radyo frekansı anahtarları, sayısal kontrollü zayıflatıcılar, dedektörler ve değişken kazanç yükselteçleri kullanılarak 110 dB giriş dinamik aralığı, -100 dBm hassasiyet ve -19 dBm çıkış gücü ile otomatik kazanç gerçekleştirilmektedir. Kontrol döngüsü. Sabit zarf ve sabit olmayan zarf girişi altında, algoritma yürütme süresi sırasıyla 41,73 s ve 230,53 s'dir ve sinyal zarfı bozulmadan kalır. Karşılaştırma, önerilen AGC algoritmasının mükemmel dinamik aralık özelliklerine ulaştığını göstermektedir.

Referanslar

XIA G, ZHANG Q, YANG Z. Patlamalı iletişim sistemleri için verimli ve geniş dinamik aralıklı hibrit dijital AGC'nin tasarımı ve uygulaması. 2012 IEEE 11. Uluslararası Sinyal İşleme Konferansı, 2012: 1373-1377.

FUJII M, KAWAGUCHI N, NAKAMURA M, ve diğerleri Hızlı solma kanalları için ileri besleme ve geri besleme AGC. Electronics Letters, 1995, 31 (13): 1029-1030.

SOBAIHI K, HAMMOUDEH A, SCAMMELL D.Yazılım tanımlı telsizler için FPGA üzerinde otomatik kazanç kontrolü Kablosuz Telekomünikasyon Sempozyumu, 2012: 1-4.

Shen Tongping, Gu Zongyun, Fang Fang, vb. FPGA optimizasyonu geri bildirim dijital AGC'nin gerçekleştirilmesi Journal of Anqing Normal University (Natural Science Edition), 2015 (3): 68-70.

Ma Zhangang, Zhang Yuping, Sun Yi, vb. Alıcıda Geniş Dinamik Aralıklı AGC Devresinin Uygulanması Yarı İletken Teknolojisi, 2010, 35 (2): 191-193.

Zhu Huizhu, Yuan Bin, Zhang Zhigang. 90 dB Geniş Dinamik Aralık Ayarlanabilir AGC Sisteminin Tasarımı. 2009 Ulusal Mikrodalga ve Milimetre Dalga Konferansı, 2009.

Chen Lize, Chen Xing, Wang Chao.Geniş bant ve büyük dinamik orta frekans AGC sisteminin uygulanması.Elektronik ölçüm teknolojisi, 2010, 33 (11): 46-48, 73.

Li Biao, Liu Chunqun, Huang Zhongkuai. AGC sistem devresinin FPGA RF alıcı ön ucuna dayalı tasarımı. Radyo İletişim Teknolojisi, 2016, 42 (3): 82-84.

Zheng Longhao, Peng Yanyun. IF AGC devre tasarımı FPGA'ya dayalı Elektronik Tasarım Mühendisliği, 2014 (14): 113-116.

Jing Bing, Xue Yuankun, Ye Fan ve diğerleri.UWB sisteminde yüksek hızlı ve çift kapalı döngü ile otomatik kazanç kontrol algoritması.2013 IEEE 10. Uluslararası ASIC Konferansı, 2013: 1-4.

Geng Yunhui, Feng Xi'an, Zhang Lu, ve diğerleri.Büyük dinamik aralıklı AGC devresinin tasarımı ve uygulaması Mikroişlemci, 2012 (3): 20-23, 28.

RAY S, HELLA M M.A 0.13 um CMOS'ta 40 db doğrusal değişken kazanç kontrollü 10 Gb / s indüktörsüz AGC amplifikatörü.IEEE Journal of Solid-State Circuits, 2016, 51 (2): 440-456.

TISSERAND E, BERVILLER Y. Yeni bir dijital otomatik kazanç kontrolünün tasarımı ve uygulaması. Elektronik Mektupları, 2016, 52 (22): 1847-1849.

Luo Youliang, Wei Liankui, Liu Jie. VCA810'a dayalı geniş dinamik aralıklı AGC devre tasarımı.Elektronik Tasarım Mühendisliği, 2016 (4): 105-107, 110.

Li Huailiang, Tuo Xianguo, Zhu Lili, et al.Orta ve düşük frekanslı ve geniş dinamik aralıklı AGC amplifikatörlerinin tasarımı.Elektrik Ölçümü ve Enstrümantasyon, 2013, 50 (2): 96-99.

He Xin. Geniş bant ve büyük dinamik AGC devre tasarımı Elektronik Tasarım Mühendisliği, 2012 (8): 167-170.

yazar bilgileri:

Zhao Xiaoteng 1, 2, Yin Junjian 1, Zhang Jintao 1, 2, Li Zhongmao 1, Leng Yongqing 1

(1. Mikroelektronik Enstitüsü, Çin Bilimler Akademisi, Pekin 100029; 2. Çin Bilimler Akademisi Üniversitesi, Pekin 100049)

-

- Pek çok güzel avatar ile Tencent Cloud Security, hangisinin yalancı olduğunu söylemek için büyük verileri kullanır

-

- Jia Zhangke'nin "Nehirlerin ve Göllerin Çocukları", Zhang Zhang'ın işbirliği öncesinde Dong Zijian'ın "Dağların ve Nehirlerin Yaşlı Adamları" çevirisini ekliyor.

-

- Xiaomi başkanı yaşlı ayının ihtişamını övdü, ancak başkan yardımcısı bilim istedi ve Qi Yu da "işin içinde" miydi?

-

- Jia Nailiang alyansını çıkardı, Tianxin'i okula gönderdi ve gözyaşlarını gizlice sildi ve güçlü bir gülümseme için Bahar Şenliği Gala provasına gitti.

-

- Yani merhaba! Feng Timo, Guo Congming, Kardeş Guo Guo ... Yeni Yılı karşılamak için sizi Chongqing Mutlu Vadi'ye davet edin