Medya ağ geçidi sisteminde geliştirilmiş ana / bağımlı anahtar tasarımı

Li Chunyu

(Zhejiang Mekanik ve Elektrik Teknolojisi Enstitüsü, Hangzhou, Zhejiang 310053)

: MTCA spesifikasyonuna dayalı medya ağ geçidi sisteminde, iki ana kontrol paneli sıcak yedekleme gerektirir.Bir ana kontrol panosu arızalandığında, diğer ana kontrol kartının arızalı kartı değiştirmek için otomatik olarak yükseltilmesi gerekir. Mevcut ana yedek anahtarlama şeması analiz edildi ve mevcut şema iyileştirildi Şema, yüksek ve düşük sıcaklık yaşlandırma testini geçti ve güvenilir bir şekilde çalıştı.

Medya ağ geçidi; CPLD; etkin / beklemede geçiş; çalışırken değiştirilebilir; ana kontrol kartı; arka panel;

: TN79 belge tanımlama kodu: ADII: 10.19358 / j.issn.1674-7720.2016.24.012

Alıntı biçimi Li Chunyu. Medya ağ geçidi sistemindeki ana / bekleme anahtarının tasarım geliştirme planı J. Mikrobilgisayar ve Uygulama, 2016,35 (24): 40-41,49.

0 Önsöz

Ana kontrol panosu, medya ağ geçidindeki beyindir.Sistemdeki diğer tekli kartları yönetir ve bakımını yapar.Üst bilgisayarla iletişim kurar ve sinyal bilgilerini iletir.Yıl boyunca sorunsuz çalışma gerektirir.Ana yedek anahtarlama teknolojisi, iletişim ekipmanının güvenilirliğini artırmak için önemli bir çözümdür. Çözümlerden [1] biri, bu nedenle ortam ağ geçidindeki ana kontrol panosunun sıcak yedeklemeye ihtiyacı vardır.Bir kart arızalandığında, diğer bekleme kartı anında ana devre olur ve sorunsuz bir şekilde geçiş yapar. Bu makale, küçük ortam ağ geçidindeki ana kontrol panosu anahtarlamasına odaklanmaktadır.

1 Ana kontrol panosunun donanım tasarımı

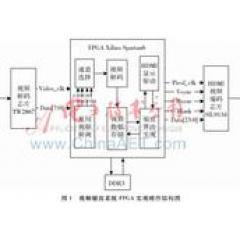

Ortam ağ geçidindeki ana kontrol panosu, diğer iş panolarını yönetir, diğer iş kartlarını yükler, saatleri dağıtır ve fan kartları ile güç kartlarının durumunu izler. Ana kontrol panosunun blok şeması Şekil 1'de gösterilmektedir.

İşlemci, RMI Company'nin XLS408'ini benimser ve programlanabilir mantık cihazları aracılığıyla üç çevre birimini birbirine bağlar: (1) FPGA: Temelde 32 yollu akıllı yönetim veriyolunu gerçekleştirir, iş kartlarını yönetir, izler ve yükler. (2) SA8000: Bu çip, yüksek hassasiyetli 38.88 MHz saat üreten bir saat çipidir. (3) SA586: Bu çip, bir E1 sinyal alıcı-verici çipidir.

Ana kontrol panosunun önemli konumu göz önüne alındığında, yıl boyunca sorunsuz çalışmayı gerektirir ve ana ve yedek kartların sıcak yedeklemesini desteklemesi gerekir. Sıcak yedekleme denen şey, ortam ağ geçidi kasası çalıştırıldığında, tamamen aynı devre yapısına sahip iki ana kontrol panosu olduğu anlamına gelir Ana kart ve bekleme kartı, yuvanın tek veya çift yuva olmasına göre ayırt edilir. Hepsi ana kart üzerinde çalışır ve bekleme kartı iş kontrolüne katılmaz, ancak ana kart kayıtlı bilgilerini bekleme kartıyla senkronize eder Bu işleme sıcak yedekleme [2] denir.

2 Mevcut aktif / yedek anahtarlama şeması

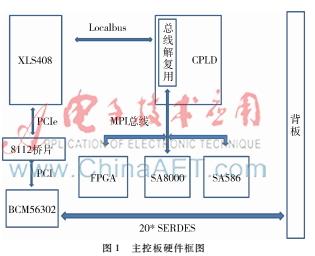

Şema 1: FPGA tabanlı ana / yedek anahtarlama şeması [3], bu şemanın uygulama blok şeması Şekil 2'de gösterilmektedir.

Şekil 2 FPGA tabanlı aktif bekleme anahtarlama şeması Bu şema ana yedek anahtarlama mantığını gerçekleştirmek için FPGA'ya dayanmaktadır.Şekil 2'de gösterilen 6 sinyal kart ile yedek ana kontrol kartı arasında arka panel üzerinden iletilir ve anahtarlama CPU'nun kontrolü altında gerçekleştirilir. Kararlılık iyidir, ancak dezavantajı, FPGA'nın RAM yapısına dayanmasıdır. FPGA kodu her açıldığında, FPGA kodu harici bir depolama cihazından dahili RAM'e yüklenmelidir [4] Sistem açıldığında, kontrolör yapılandırma verilerini okur ve FPGA'ya iletir. Yapılandırın [5]. Bu yapılandırma süreci ve yapılandırma verilerinin boyutu, yapılandırma sırasında yükleme saati ile büyük bir ilişkiye sahiptir ve genellikle birkaç saniye veya birkaç dakika sürer, bu da anahtarlama süresini uzatır.

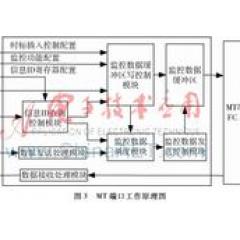

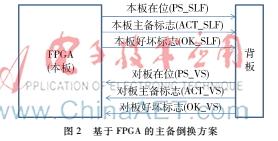

Şema 2: CPLD tabanlı ana / yedek anahtarlama şeması [6], bu şemanın gerçekleştirilmesi Şekil 3'te gösterilmektedir.

Bu çözüm, FPGA'nın yavaş yüklenmesi sorununu çözebilen FPGA yerine CPLD'yi kullanır.CPLD'nin dahili kod depolaması Flash mekanizmasını kullanır ve dışarıdan yüklenmesi gerekmez. Başlatma süresi 1 ms'dir, bu nedenle CPLD'nin anahtarlama hızı büyük ölçüde iyileştirilecektir.

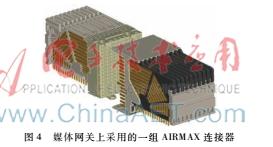

Bununla birlikte, gerçek anormal test ve titreşim testinde, çözümün çift ana arızaya sahip olduğu, yani iki ana kontrol kartının aynı anda etkili ana kart olarak çalışarak çıkış sinyali çakışmalarına neden olduğu bulunmuştur. Analizden sonra, medya ağ geçidindeki çok sayıda kart ve sinyal nedeniyle, yüksek yoğunluklu ara bağlantı arka paneli genellikle Huawei UAP6600'ün ana kontrol kartında kullanılan arka panel konektöründe kullanılan FCI'nın AIRMAX konektörü gibi özel konektörler kullanır. Şekil 4 [7] 'de gösterilen 7 grup konektörü kullanmak için, genellikle ürünün titreşim testinde çift ana fenomenin meydana geldiği bulunmuştur. Bu nedenle, yukarıda bahsedilen CPLD bazlı aktif / yedek anahtarlama şemasında da sorunlar vardır.

3 Geliştirilmiş ana bekleme anahtarlama şeması

3.1 Donanım iyileştirme önlemleri

Anormal test ve güvenilirlik testi sonuçlarına dayanarak, aşağıdaki senaryo 2'deki dual-master'ın nedenini analiz eder.

Ortam ağ geçidinde arka panele takılı birden fazla kart var Ana kontrol kartının ve arka yüzün konektörleri Şekil 4'te gösterilen şemayı kullanır. Yedi adet 54 pimli AIRMAX konektörü arka panele kıvrımlıdır. Şekil 5 sağda Ana kartın konumu ve konektör üzerindeki bekleme gösterge sinyali (ACT_VS sinyali).

Sıkma işlemi nedeniyle, düzensiz konektörler, AIRMAX konektöründe kısa pim olmaması ve kartın fişi çekildiğinde eklenti sinyalinin bağlantısı kesilmemesi gibi olaylar vardır, ancak ACT_VS ayrılmıştır; kart takıldığında, eklenti sinyali de görünebilir Temas edildi ve ACT_VS henüz bağlı değil, bu nedenle ACT_VS algılanamıyor, bu da panonun karşı panonun düştüğünü düşünmesine neden oluyor, bu nedenle kart master'a yükseliyor ve dual master fenomeni ortaya çıkıyor.

İyileştirme planı, Şekil 6'da gösterildiği gibi, bir yardımcı karşı-kart ana / bekleme gösterge sinyali, kenarın yakınında bir konektör ve eklenti sinyaline yakın yardımcı karşı-kart ana / yedek gösterge sinyali eklemektir.

3.2 Mantık kodu iyileştirme önlemleri

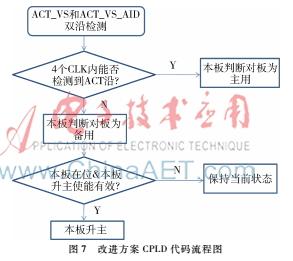

Kasa açıldıktan sonra, iki ana kart aynı anda ana karttır, ancak çift yuvalı ana kontrol panosu 18 CPLD çalışma saatinden sonra ana durumdan çıkar ve tek yuvalı ana kontrol kartı her zaman ana karttır. CPLD'deki kod Verilog [8] dil programlamasıyla gerçekleştirilir, program akış şeması Şekil 7'de gösterildiği gibidir.

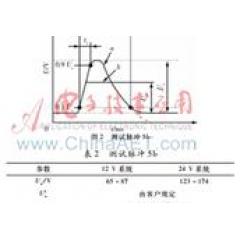

3.3 İyileştirilmiş şemanın anahtarlama süresinin hesaplanması

Kasa açıldıktan sonra, 18 CPLD saat döngüsünden sonra, çift yuva 8'deki ana kontrol panosu ana işlevden çekilir ve 31 saat döngüsünden sonra, tek yuva 7'deki ana kontrol kartı ana işlevden çekilir, bu nedenle normal durum 7'dir. Yuvadaki kart aktif durumda. Çalıştıktan sonra, Şekil 7'den görülebileceği gibi, karttan gönderilen ACT_VS ve ACT_VS_AID sinyalleri, 8. yuvadaki kartın 4 saat döngüsünde algılanmazsa, kartın master'a yükseltileceği, CPLD çalışma saati 15 ns ise, geçiş yap Zaman 4 × CPLD CLK = 4 × 15 ns = 60 ns'dir.

4. Sonuç

Ortam ağ geçidi üzerindeki arka panel ve ana kontrol panosu çok sayıda bağlantı sinyaline sahiptir 350'den fazla çeşit sinyal vardır.Yüksek yoğunluklu arka planlara uygun konektörler kullanılmalıdır.Ancak kıvırma işlemi nedeniyle ana kart ACT_VS sinyalini alamaz. Yukarıda bahsedilen çözüm durumunda, birden fazla anormal test ve titreşim testi gerçekleştirildi ve hiçbir sorun oluşmadı.

Referanslar

1 Li Jie, Huang Tingxi, Pan Taotao. Yüksek güvenilirlikli iletişim ekipmanı için ana / yedek anahtarlama yazılımının uygulama yöntemi J. Television Technology, 2013, 37 (11): 170172.

2 Zhang Yufeng, Sun Zhixin. Üst düzey yönlendiricilerde etkin yedeklemeye dayalı ana bekleme anahtarlama uygulaması J. Bilgisayar Teknolojisi ve Geliştirme, 2010, 20 (3): 172175,179.

3 Tan Yu, Yao Yafeng, Chen Deng, ve diğerleri FPGA ana bekleme anahtarlamasına dayalı devre tasarımı ve uygulaması J. Television Technology, 2014, 38 (11): 8285, 102.

4 Li Chunyu, Zhang Lixia. FPGA yükleme hızını iyileştirmek için CPLD'yi kullanma J. Elektronik Cihazlar, 2013, 36 (4): 550553.

[5] Li Chunyu. FPGA köle ve CPLD J. ZTE Technology, 2014, 20 (4): 5759'a dayalı hızlı yükleme şeması.

[6] Shi Shihua, Gao Xiquan, Jin Songjie, ve diğerleri Yüksek güvenilirlikli iletişim ekipmanı için ana ve yedek anahtarlama tasarımı J Elektronik Teknolojisi, 2007 (7): 4750.

7 Fleck Research.AirMax VS Connector System EB / OL. 200909xx 20160719

[8] Wang Jingxia, FPGA / CPLD uygulama teknolojisi (Verilog dil versiyonu) [M]. Pekin: Elektronik Endüstrisi Yayınevi, 2011.

-

- Yalnızca "God of War" senkronizasyon stratejisine sahip değil, aynı zamanda senkronize bir Çince ayarımız da var