Çok Fazlı Enterpolasyona Dayalı Video Ölçekleme Sisteminin FPGA Uygulaması

Wang Zhongbo, Zhou Yuan, Huang Lu

(Bilgi Bilimi ve Teknolojisi Okulu, Çin Bilim ve Teknoloji Üniversitesi, Hefei, Anhui 230026)

: Geleneksel enterpolasyon algoritması, özellikle yüksek çözünürlüklü video görüntülerini çıkarırken video görüntülerini ölçeklendirirken ayrıntıları işlemede zayıf performansa sahiptir. Çok fazlı enterpolasyon algoritması, temel olarak algoritmanın ilkesini ve algoritmanın donanım yapısını açıklamak için video görüntü ölçeklendirmesini sağlamak için kullanılır. Bunların arasında, donanım devresi kontrol kısmı Xilinx'in Spartan6 serisi FPGA yongasını kullanır, sistem dört kamera tarafından toplanan video sinyalinin herhangi bir kanaldan 1920x1080 @ 60 Hz çözünürlüğe yükseltilebileceğini fark edebilir.Sonuç, çıkış video görüntüsünün gerçek zamanlı olduğunu ve Detaylar iyi tutulur.

: Video yakınlaştırma; çok fazlı; FPGA; gerçek zamanlı

: TN911.73 Belge tanımlama kodu: ADoi: 10.19358 / j.issn.1674-7720.2016.24.014

Alıntı biçimi : Wang Zhongbo, Zhou Yuan, Huang Lu.Çok fazlı enterpolasyona dayalı video ölçekleme sisteminin FPGA uygulaması J. Mikrobilgisayar ve Uygulama, 2016,35 (24): 46-49.

0 Önsöz

Video görüntü ölçekleme, video görüntü çözünürlüğü dönüştürme, video görüntü yeniden örnekleme, video görüntü ölçek dönüştürme, vb. Olarak da adlandırılabilir. Video görüntüsünün çıktı kalitesini ve vizyonunu doğrudan etkileyen dijital video görüntü işleme teknolojisindeki temel teknolojilerden biridir. Deneyim. Şu anda, video görüntü ölçekleme teknolojisi tıbbi görüntüleme, mühendislik, multimedya, video konferans ve diğer alanlarda yaygın olarak kullanılmaktadır [1].

Geleneksel video görüntü ölçekleme ve enterpolasyon algoritmaları arasında en yakın komşu enterpolasyonu, çift doğrusal enterpolasyon, çift kübik enterpolasyon vb. Yer alır. Diğer enterpolasyon algoritmaları arasında kenar enterpolasyonu, B-spline enterpolasyonu, uyarlamalı enterpolasyon vb. [2-3], doğrusal modellere dayanır. Algoritma görüntü işlemeye uygulandığında, yüksek frekanslı sinyaller, düşük frekanslı sinyal alanı üzerine bindirilerek, özellikle video görüntü çıkış çözünürlüğü yüksek ayrıntılı işleme gerektirdiğinde, zayıf bir görsel deneyim getirecek çıktı video görüntüsünün örtüşmesine neden olacaktır. etki. Çok fazlı enterpolasyon algoritması da yaygın olarak kullanılan bir video görüntü ölçekleme metodudur.Geleneksel enterpolasyon algoritması ile karşılaştırıldığında, detay tutmada daha iyi performansa sahiptir ve ayrıca endüstride yaygın olarak kullanılmaktadır.

1 algoritma prensibi

Video görüntü ölçeklemenin temel ilkesi, (M, N) çözünürlüklü orijinal görüntüyü (X, Y) çözünürlüklü hedef görüntüye dönüştürmektir. Matematiksel tanımla şu şekilde tanımlanabilir: Verilen (M, N) piksel, Pixelin (i, j) (i = 1,2,, M; j = 1,2,, N), burada i, j Orijinal görüntünün piksel koordinatlarıdır ve Pixelin (i, j), orijinal görüntünün piksel değeridir. Şimdi, bilinen pikselleri kullanarak çıktı piksellerini bulmak için matematiksel bir ilişkisel eşleme kullanmayı umuyorum, Pixelout (x, y) (x = 1,2, ..., X; y = 1,2, ..., Y), burada x, y hedef görüntünün piksel koordinatlarıdır ve Pixelout (x, y) hedef görüntünün piksel değeridir. Daha sonra girdi ve çıktı görüntüsünün piksel değerine karşılık gelen fonksiyon ilişkisi şu şekilde ifade edilebilir: Pixelout (x, y) = f (i, j, Pixelin (i, j)), çok fazlı enterpolasyonun özü, hedef görüntüyü fonksiyonun eşleme ilişkisine göre çözmektir. Piksel değerleri.

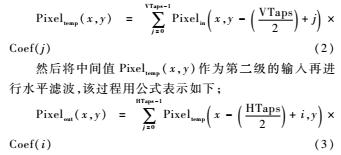

Yukarıdaki analize göre hedef görüntünün piksel değeri doğrudan orijinal görüntüden elde edilemez ancak orijinal görüntü ile ilgili konum koordinatlarından ve piksel değerlerinden hesaplanması gerekir. Görüntü içeriğinin yerel korelasyonundan dolayı, çıktı hedef görüntüsünün piksel değeri, karşılık gelen uzamsal konuma bitişik giriş orijinal görüntünün piksel değeri ile daha büyük bir korelasyona sahiptir ve uzak uzamsal konumun piksel değeri ile korelasyon daha azdır. Genel video görüntüsü ölçekleme işlemi, aşağıdaki gibi formül [4] ile ifade edilebilen tipik bir iki boyutlu filtreleme işlemidir:

Pixelout (x, y) =

HTaps 1i = 0VTaps 1j = 0Pixelinx HTaps2 + i, y VTaps2 + j ×

Coef (i, j) (1)

HTap'ler ve VTap'ler, yatay ve dikey yönlerde iki iki boyutlu filtrenin dokunma sayısıdır ve Katsayı (i, j), karşılık gelen filtrenin katsayısıdır. Bu katsayı, çıktı piksel değerine karşı operasyonda yer alan girdi piksel değerini temsil eder Ağırlığın boyutu. Değeri, karşılık gelen konumdaki girdi piksel değerinin çıktı piksel değeri üzerindeki etkisini belirler ve doğrudan ölçeklendirmenin etkisini belirler.Katsayının belirlenmesi, alçak geçiren filtre ve örtüşme önleme gereksinimlerine bağlıdır.

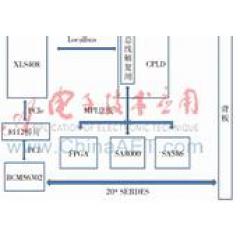

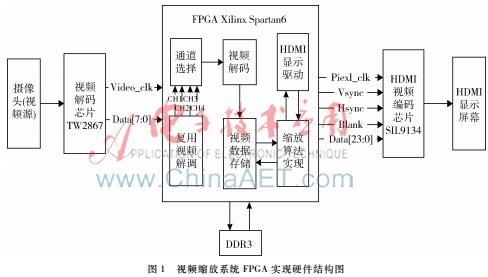

Şekil 1 Video ölçekleme sisteminin FPGA uygulamasının donanım yapısı diyagramı.İki boyutlu yapı, veri işlemlerinde daha karmaşıktır.İşlemi basitleştirmek için, iki boyutlu filtre genellikle bölünür ve iki boyutlu özellikleri, yani yatay olanı elde etmek için iki tek boyutlu filtre kademelendirilir. Filtre ve dikey filtre. İlk olarak, ilk aşama, Pixeltemp (x, y) ara değerini çıkarmak için dikey filtreleme gerçekleştirir. İşlem şu şekilde ifade edilir:

Yukarıdaki analiz sayesinde, basitleştirilmiş işlemden önce ve sonra gerekli çarpan sayısının (VTaps × HTap) 'dan (VTaps + HTaps)' a indirildiği ve hesaplama miktarının büyük ölçüde azaldığı görülebilir.Bu yöntem, gerçek zamanlı gereksinimleri yüksek bir donanım sisteminin gerçekleştirilmesi için oldukça elverişlidir. Aynı zamanda, bu fikir aynı zamanda çeşitli video görüntü ölçekleme algoritmalarının donanım uygulamasının temel modelidir, yani ölçekleme sırasıyla yatay ve dikey yönlerde gerçekleştirilir, böylece sorun, tek boyutlu sinyalin örnekleme oranının değişiminin analizi ve işleme süreci haline gelir.

2 Sistem donanım yapısı

Sistemin donanım yapısı Şekil 1'de gösterilmektedir. Xilinx'in Spartan6 serisi FPGA yongası, çok fazlı enterpolasyon ölçekleme algoritmasını doğrulamak için kullanılır. Sistem, giriş kaynağı olarak video sinyallerini toplamak için dört analog kamera kullanır TW2867 çok kanallı video kod çözücü yongası, analog video sinyallerini dijital video sinyallerine dönüştürür ve veri işleme için FPGA yongasına gönderir FPGA ilk olarak giriş veri sinyallerini ön işler. Yakalanan görüntü ve çıktı ekranı görüntü yenileme hızı tutarsız olduğundan, veri işleme sırasında okuma ve yazma hızlarının eşleşmesini sağlamak için görüntü verilerini DDR3'e yazmak ve ardından verileri ölçekleme ve sonra çıktı almak için okumak gerekir.Çıkış sinyalinin HDMI standart zamanlamasına uyması gerekir. Son olarak, çıktı veri sinyali SIL9134 video kodlama çipi aracılığıyla bir video akışına kodlanır ve görüntülenmesi ve çıkış efektinin kontrol edilmesi için ekrana iletilir.

2.1 İlgili çiplere giriş

2.1.1 Video kod çözme çipi

TW2867, Techwell Semiconductor Company tarafından üretilen bir çiptir.Ana işlevi, analog kompozit video sinyallerini, ekran, depolama ve iletim gibi dijital video bilgi işlemleri için uygun olan dijital video sinyallerine dönüştürmektir. Çip, bir video kod çözücü ve bir ses kodlayıcı içerir Video kod çözücünün her kanalı, giriş analog video sinyalini sayısallaştıran bir ADC (analogdan dijitale dönüştürücü) içerir. TW2867 yongasının I2C sinyal hattı pini, STM32 yongasının I2C sinyal hattı pinine bağlanır TW2867 yonga yazmacının parametreleri STM32 yongası aracılığıyla yapılandırılır.

2.1.2 Video kodlama çipi

SIL9134, SILicon Image Semiconductor Corporation tarafından üretilen bir çiptir. HDMI1.3 arayüz özelliklerini destekler ve zamanlama standartlarıyla uyumlu veri sinyallerini HDMI video akışlarına kodlayabilir. Ayrıca yüksek tanımlı ses ve video sinyallerini iletebilir ve 1080P @ 60 Hz çözünürlüklü video çıkışını destekler. SIL9134 yongasının I2C sinyal hattı pini, STM32 yongasının I2C sinyal hattı pinine bağlanır ve SIL9134 yonga yazmacının parametreleri STM32 yongası aracılığıyla yapılandırılır.

2.2 Ana modüllere giriş

Yukarıdaki sistem donanım yapısının tanıtımına göre FPGA giriş kısmı kamera tarafından toplanan analog video kaynağıdır ve 720 × 576 @ 25 Hz çözünürlükte dört kanallı çoklamalı BT656 formatlı video sinyalidir. Çıkış kısmının video çözünürlüğü 1920 × 1080 @ 60 Hz'dir ve video sinyalinin formatı HDMI'dır. İşleme sürecinde, video verilerinin formatındaki değişiklikler nedeniyle, önce çoklanmış dört kanallı video sinyalini demodüle edin ve ardından kodu çözmek için herhangi bir video sinyalini seçin; kodu çözülmüş video sinyalini veri depolama modülüne yazın ve ardından videoyu okuyun Sinyal ölçeklenir ve son olarak işlenen veriler entegre edilir ve karşılık gelen çözünürlüğün zamanlama sinyali ile çıkarılır.

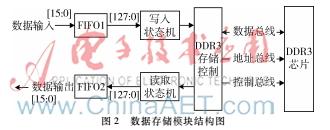

2.2.1 Video veri depolama modülü

Video veri depolama modülünün gerçekleştirme fikri Şekil 2'de gösterilmektedir. Giriş verisi bit genişliği 16 bittir.DDR3'e yazılan veri de 16 bit ise verimlilik çok düşüktür DDR3 arayüzü 128 bite kadar destekleyen çift yönlü bir porttur, bu nedenle veri işleme hızını artırmak için maksimum bit genişliği seçilir. Oran dönüşümünü gerçekleştirmek için FIFO kullanın. Video verilerinin işlenmesi çerçeve birimine dayanır ve her çerçevenin işlenmesi davranış birimine bağlıdır.Ping-pong işleme yöntemi her veri satırı için benimsenir FIFO verileri yarım satıra ulaştığında, giriş verileri aynı anda DDR3'e yazılır. Kalan yarım hat için giriş verilerini almaya devam edin. DDR3 depolama adresi de yukarıda belirtilen fikirlere göre hesaplanır.

2.2.2 Ölçekleme algoritması uygulama modülü

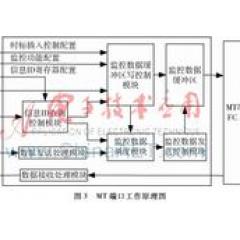

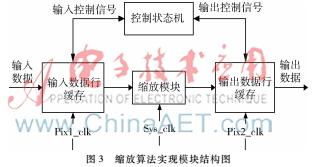

Ölçeklendirme algoritması uygulama modülünün yapı diyagramı Şekil 3'te gösterilmektedir. Video verileri, soldan sağa, yukarıdan aşağıya satır satır, piksel piksel tarama sırasında görüntülenir ve ölçekleme hesaplaması da bu sırada gerçekleştirilir. Yakınlaştırma modülüne giren veriler ilk olarak girilir ve ara belleğe alınır ve ardından veri, yakınlaştırma işleminden sonra çıkarılır ve ara belleğe alınır ve ardından veri, belirli bir zaman sırasına göre ara bellek alanından okunur ve çıkarılır. Genel olarak konuşursak, ölçekleme modülünün giriş ve çıkış veri saati ve saati tutarlı değildir Birincinin saati, giriş ve çıkış videosunun çözünürlüğü ile belirlenir ve ikincisi, farklı örnekleme oranı dönüşümlerinin ölçeklendirme gereksinimlerine uyum sağlamak için ayrı bir saat kullanır.

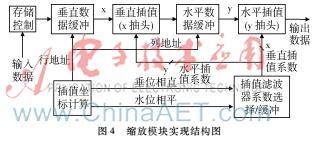

Şekil 4 Yakınlaştırma modülü uygulamasının yapı şeması Şekil 3'te gösterilmektedir. Veri önbelleği, çift portlu RAM asenkron depolama mekanizması kullanılarak gerçekleştirilir.Farklı modüller arasındaki veri çağırma, parametre hesaplama, mod seçimi ve çıktı formatı, durum makinesi tarafından kontrol edilir. nın-nin. Yakınlaştırma modülünün gerçekleştirme fikri Şekil 4'te gösterilmektedir. Önceki teorik analize dayalı olarak, iki boyutlu görüntünün enterpolasyonu, tek boyutlu yatay enterpolasyon ve dikey enterpolasyon olarak basitleştirilmiştir. Donanım uygulamasında, filtreye ne kadar çok dokunulursa, çıktı görüntüsünün performansı o kadar iyi ve daha fazla kaynak tüketir. Fiili hesaplamalarda, dikey yönde çok sayıda veri satırının önceden önbelleğe alınması gerekir ki bu kaçınılmaz olarak çok büyük miktarda hesaplama getirecektir.Dikey yöndeki filtre musluklarının sayısı çok fazla ise, veri depolama baskısına neden olur ve donanım uygulama maliyetini artırır. Bu nedenle tasarım dikeydir. Yön, sistemdeki [5] hat tamponlarının sayısını azaltarak daha az filtre kılavuzu kullanır. Hat tamponu, sabit dikey filtre 5Taps ve yatay filtre 7Taps devre yapısı minimum gereksinimine göre performans ve kaynakların kapsamlı bir şekilde değerlendirilmesi benimsenmiştir.

2.2.3 Çarpanın boru hattı gerçekleştirilmesi

Algoritma gerçekleştirme sürecinde, hesaplama miktarı ve kaynak ek yükü esas olarak çarpan üzerinde yoğunlaşır, bu nedenle devre performansını iyileştirmek için çarpanın dönüştürülmesi gerekir. Çarpma ilkesinin analizi yoluyla, çarpmayı elde etmek için çarpanlar yerine toplayıcıların ve seçicilerin kullanılması [6] ve veri işleme hızını iyileştirmek için boru hattı yapısının kullanılması.

Örneğin, iki K-bit verisi A ve B'nin çarpma işleminin dönüştürme işlemi, donanım dili ile tanımlandığında seçiciler ve toplayıcılar ile ifade edilebilen formül (4) ~ (6) 'da gösterilmektedir.

Boru hattı yapısını gerçekleştirmek için D flip-flopları ekleyerek her bir veri işlem sırasını hizalamak için, buradaki boru hattı aşamalarının sayısı çok fazla olmamalıdır, aksi takdirde güç tüketimi artacaktır. Bu yazıda işlenen veriler RGB formatındadır ve üç kanallı veriler ayrılır ve eşzamanlı olarak çalıştırılır ve daha sonra esas olarak K = 8 devresi biçiminde birleştirilir.

3 deneysel sonuç

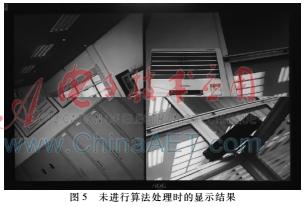

Sistem algoritma işleme yapmadığında, dört kanal tarafından toplanan video verilerini doğrudan azaltır ve Şekil 5'te gösterildiği gibi aynı anda aynı monitör ekranına çıkarır. Sistem algoritma işlemeyi gerçekleştirirken herhangi bir kanal tarafından toplanan video verilerini büyütebilir ve görüntü ekranına çıkarabilir Çözünürlük bilgisi 1920x1080 @ 60 Hz'dir. Şekil 6'da gösterildiği gibi, ilk kanal tarafından yakalanan video varsayılan olarak büyütülür ve herhangi bir kanal tarafından yakalanan video, düğmeye basılarak gerçek zamanlı olarak değiştirilir.

4. Sonuç

Bu makale, video görüntü ölçeklendirmesini sağlamak için çok fazlı enterpolasyon algoritmasını kullanır ve FPGA donanım platformunda doğrulanır, büyütülmüş video görüntü bilgisi geçişleri sorunsuz, ayrıntılar iyi korunur, herhangi bir kanalın video görüntü sinyali değiştirilir ve büyütülür ve video görüntü sinyali hızlı bir şekilde görüntülenir ve toplanan video görüntü bilgilerinin içeriği değişir. Gerçek zamanlı değişiklikleri senkronize edin. Çok fazlı enterpolasyon algoritması, güçlendirilmiş video görüntüsünün içerik bilgilerini daha iyi tutar, ancak kenar parçasını işlemek için iyi bir iş çıkaramaz.Bu, herhangi bir etki yaratmasa da, güçlendirilmiş video görüntüsünün performansını daha da iyileştirmek için, gelecekteki araştırmalar Çok fazlı enterpolasyon ve kenar enterpolasyonundan oluşan iki algoritmanın birleşmesi gibi iyi performansa ve tamamlayıcıya sahip çeşitli enterpolasyon algoritmaları düşünülebilir, böylece ölçeklemeden sonra çıktı video görüntüsünün performansı daha mükemmel olacaktır.

Referanslar

[1] Wang Yangang, Peng Silong. Video ölçekleme için yeniden yapılandırılabilir düşük maliyetli, bellek açısından verimli VLSI mimarisi J. Yüksek Teknoloji Mektupları, 2013 (1) .137144. 2 Hu Xiaolong, Feng Bin. FPGA tabanlı Yüksek çözünürlüklü gerçek zamanlı izleme görüntüsü yakınlaştırma tasarımı J. LCD ve Ekran, 2009, 24 (6): 882885.

3 Shi Zaifeng, Yao Suying, Zhao Yingchun Morfolojik kenar enterpolasyonuna dayalı yeni bir video görüntü ölçekleme algoritması C. 2008 Sinir Ağları ve Sinyal İşleme Uluslararası Konferansı, 2008: 388391.

[4] Xilinx Şirketi. LogiCORE IP Video Scaler v.7.00.a [EB / OL]. (201207) [20160724]

[5] Guo Ruoshan. Paralel çok fazlı görüntü enterpolasyon cihazı ve yöntemi P. Çin: 104935831A, 20150923.

6 LIN MB. VLSI Sistemlerine Giriş: Mantık, Devre ve Sistem Tasarımı M. Liu Yanyan, vb., Tercüme edildi. Beijing: Electronic Industry Press, 2015.

-

- Çift modlu oyun deneyimi, HyperX Cloud Mix Skyline Bluetooth oyun kulaklığı değerlendirmesi Titanium Geek