FPGA'ya Dayalı PCIe Veri Yolu Arayüzünün DMA Denetleyicisinin Tasarımı

Wang Zhiguang, HD şans

(Tianjin Temel Optoelektronik İnce Film Cihazları ve Teknolojisi Laboratuvarı, Elektronik Bilgi ve Optik Mühendisliği Okulu, Nankai Üniversitesi, Tianjin 300350)

Altera'nın FPGA'sı tarafından sağlanan PCIePHYIP ve Synopsys tarafından sağlanan PCIe Core IP kullanılarak, PCIe veriyolu arabirimine sahip bir DMA denetleyicisinin uygulanması için bir yöntem önerildi ve 4 kanallı bir PCIe iletim sistemi oluşturuldu. Sistem Synopsys VIP doğrulama ortamı kullanılarak simüle edildi ve doğrulandı ve gerçek iletim doğrulaması, veri okuma ve yazmanın doğruluğunu doğrulamak için bir platform oluşturmak için Altera Stratix V EX serisi FPGA kullanılarak gerçekleştirildi Veri yolu bant genişliği zirvelerine DMA okuma ve yazma işlemleri sırasında ulaşıldı. Çoğu pratik uygulamada veri aktarım hızı gereksinimlerini karşılayabilen 1547 MB / sn ve 1607 MB / sn.

Çin Kütüphanesi Sınıflandırma Numarası: TP274

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.172445

Çince alıntı biçimi: Wang Zhiguang, HD Yun. FPGA tabanlı PCIe veriyolu arabirimine dayalı DMA denetleyici tasarımı.Elektronik Teknoloji Uygulaması, 2018, 44 (1): 9-12,

İngilizce alıntı biçimi: Wang Zhiguang, Gao Qingyun.PCIe veriyolu arabiriminin FPGA tabanlı DMA denetleyicisinin tasarımı.Elektronik Tekniğin Uygulanması, 2018, 44 (1): 9-12,

0 Önsöz

İletişim teknolojisinin sürekli gelişmesiyle birlikte, veri aktarım sistemlerinin hızı ve veri aktarımının kalitesi için gereksinimler de artmaktadır. Intel tarafından 2001 yılında önerilen üçüncü nesil I / O veri yolu teknolojisi-PCI Express veri yolu teknolojisi, yüksek hızlı diferansiyel seri veri iletimi kullanır.Yüksek bant genişliği, yüksek güvenilirlik ve yüksek ölçeklenebilirlik avantajlarına sahiptir. PCI ve PCI-X veri yollarının eksikliğini telafi edin.

PCIe 2.0 protokolüne dayanan bu makale, bir DMA denetleyicisi önermek ve FPGA ile PC arasında yüksek hızlı bir veri aktarım sistemi oluşturmak için Altera Transceiver PHY IP, Synopsys PCIe Core IP ve AXI veri yolunu kullanır. Kayıt okuma ve yazma işlemlerini (tek sözcük okuma ve yazma) ve DMA okuma ve yazma işlemlerini gerçekleştirin ve veri okuma ve yazmanın doğruluğunu gözlemlemek ve doğrulamak için Synopsys VIP ortamında sistem simülasyonunu ve ana bilgisayar yazılımını kullanın.

1 Tasarım planı

1.1 Temel modül

1.1.1 Altera Stratix V GX serisi FPGA ve PCIe PHY IP

Bu tasarım, PCIe PHY IP sabit çekirdek modülünü entegre eden Stratix V GX serisi altındaki 5SGXEA7K2F40C2N FPGA yongasını kullanır. PCIe PHY IP sabit çekirdeği, Şekil 1'de gösterildiği gibi üç parça içerir. PCI Express için PHY IP Çekirdeği (PIPE), PCIe veri yolunun fiziksel katmanını bütünleştirir. Alıcı-Verici Yeniden Yapılandırma Denetleyicisi IP Çekirdeği, simülasyon parametrelerini dinamik olarak yeniden yapılandırabilir. Alıcı-Verici PHY Sıfırlama Denetleyicisi IP Çekirdeği, PCIe bağlantısının başlatılmasını sağlamak için alıcı-vericinin sıfırlama modülü olarak işlev görür.

1.1.2 Synopsys IP ve VIP

VIP, adından da anlaşılacağı gibi, bazı standart arayüzler için standart bir veri yolu davranış modeli sağlayan Doğrulama IP'sidir (Doğrulama IP'si). Synopsys, PCIe veri yolu veri bağlantı katmanının ve işlem katmanının işlevlerini uygulayan ve yerleşik DMA'ya sahip olan PCIe veri yolunun Denetleyici IP'sini sağlar.Ayrıca, PCIe veri yolu için standart bir veri yolu davranış modeli sağlayan PCIe veri yolu için bir VIP sağlar. Ana bilgisayarın işlevi simüle edilmiştir.

1.1.3 AXI veri yolu

AXI (Advanced eXtensible Interface) veriyolu, yüksek performanslı, yüksek bant genişliğine sahip ve düşük gecikmeli bir veri yolu protokolüdür.Önemli bir özelliğe sahiptir.Adres / kontrol ve veri kanalları ayrılmıştır.Adres kanalı okunan 5 tek yönlü kanal vardır. , Adres kanalını yazın, veri kanalını okuyun, veri kanalını yazın, yanıt kanalını yazın, gecikmeyi azaltın ve DMA'nın verimliliğini artırın.

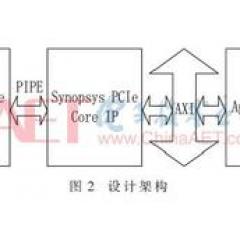

1.2 Genel şema tasarımı

Bu tasarımda kullanılan genel mimari, Altera PHY IP + Synopsys PCIe Core IP + AXI veri yolu + Uygulaması olan Şekil 2'de gösterilmektedir.

Synopsys'in PCIe VIP ortamını kullanmak için Synopsys PCIe Core IP kullanılır. AXI veri yolu arabirimi, PCIe işlem katmanı ile uygulama tarafı arasında benimsenmiştir ve bu, gelecekteki tasarımlarda kolayca genişletilebilir ve değiştirilebilir. Uygulama tarafı tasarımı, PCIe DMA denetleyicisinin işlevini gerçekleştirir ve yazmaç tarafından okunan ve yazılan verileri saklamak için kullanılan biri 128 DW boyutunda iki RAM'i entegre eder; diğeri ise DMA tarafından okunan ve yazılan verileri depolamak için kullanılan 512 DW boyutunda.

2 DMA kontrolörünün tasarımı ve gerçekleştirilmesi

2.1 Uygulama tarafı DMA işlem akışı

Uygulama tarafı tarafından başlatılan DMA işlem akışı Şekil 3'te gösterilmektedir. DMA okuma işleminin nihai sonucu, ana bilgisayar tarafındaki verileri DMA tarzında uygulama tarafının belleğine yazmaktır. DMA yazma işleminin sonucu, uygulama tarafındaki verileri DMA tarzında ana bilgisayar tarafındaki belleğe yazmaktır. Şekil 3, uygulama tarafından başlatılan DMA işleminin spesifik akışını göstermektedir.

(1) Ana bilgisayar tarafı, DMA okuma ve yazma bayrağını, DMA uzunluğunu, DMA kaynağını ve hedef bellek adreslerini, yazmaç yazma yoluyla uygulama tarafındaki yazmacıya yazar;

(2) Uygulama tarafındaki Slave modülü bu komutları Ana modüle gönderir;

(3) Ana modül, bu komutları Synopsys PCIe Core IP tarafından özelleştirilmiş Dbi veriyolu moduna göre PCIe Core IP'nin dahili kayıtlarına iletir;

(4) PCIe Core IP, DMA okuma ve yazma talimatlarını alır ve sonraki işlemleri gerçekleştirmek için Ana arayüzü çalıştırmaya devam eder;

(5) DMA için okurken, PCIe Core IP'nin yerleşik DMA'sı hedef verileri ana bilgisayar tarafındaki "kaynak bellek adresinden" okur; DMA için yazarken, PCIe Core IP Ana arabirimi AXI veri yolu üzerinden okur Hedef verileri "kaynak bellek adresinden" okuyun;

(6) DMA için okurken, PCIe Core IP Master, DMA tarafından okunan hedef veriyi alır ve bunu AXI veri yolu üzerinden uygulama tarafının "hedef bellek adresine" yazarak yazar; DMA için yazarken, Ana birim hedef verileri aldıktan sonra, yerleşik DMA verileri ana bilgisayar tarafındaki "hedef bellek adresine" gönderir;

(7) DMA işlemi tamamlandığında, PCIe Core IP, uygulama tarafındaki kesme modülünü bilgilendirecektir;

(8) Uygulama tarafındaki kesme modülü, ana bilgisayar tarafına bir kesme gönderecektir.

2.2 Uygulama tarafı DMA kontrol durum makinesi

Uygulama tarafının yalnızca DMA okuma ve yazma bayrağını, DMA uzunluğunu, DMA kaynağını ve hedef bellek adresini ve ana bilgisayar tarafı tarafından PCIe Core IP'deki dahili yazmacıya yazılan DMA başlatma sinyalini yazması ve DMA işleminin tamamlanmasını beklemesi ve bir kesme sinyali vermesi gerekir. .

Aşağıda, uygulama tarafındaki ayrıntılı DMA kontrol durumu makinesi verilmiştir: Şekil 4'te gösterildiği gibi, durum makinesi, DMA okuma işlemlerini ve DMA yazma işlemlerini entegre ederek kod miktarını azaltır.

(1) IDLEPHASE: boşta durumu. Başlatma sinyali start_flag geçerli olduğunda, ENGINE_ENABLE durumuna atlayın;

(2) ENGINE_ENABLE: wr_rdn_flg 0 olduğunda DMA okuma ve yazma tipi sinyalini değerlendirin, bu DMA okuma anlamına gelir (PC'den FPGA'ya), DMA okuma motorunu etkinleştirin; wr_rdn_flg 1 olduğunda, DMA yazma (FPGA'dan PC'ye) anlamına gelir , DMA yazma motorunu etkinleştirin;

(3) DMA_TRANS_SIZE: DMA veri aktarım uzunluğunu ayarlayın, en fazla 512 DW bir kez iletilebilir ve en az 1 DW bir kez iletilebilir;

(4) DMA_SAR: DMA işlem kaynak adresini ayarlayın (DMA okunduğunda, kaynak adresi ana bilgisayar adresidir; DMA yazıldığında, kaynak adresi uygulama adresidir);

(5) DMA_DAR: DMA işlem hedef adresini ayarlayın (DMA okunduğunda, hedef adresi uygulama tarafı adresidir; DMA yazma olduğunda, hedef adresi ana bilgisayar tarafı adresidir);

(6) DMA_DOORBELL: DMA işlemini etkinleştirin kapı zili sinyali dma_strt, DMA işlemini başlat;

(7) DMA_WAIT_INT: DMA işleminin tamamlanmasını bekleyin;

(8) DMA_INT_STATUS: DMA işlem kesme kaydının durumunu okuyun DMA işlemi tamamlama sinyali dma_done geçerli olduğunda, bir tamamlama kesmesi üretilir ve DMA_CLEAR_INT durumu atlanır;

(9) DMA_CLEAR_INT: Kesmeyi temizleyin, IDLEPHASE durumuna dönün ve bir sonraki DMA aktarımı için hazırlanın.

3 DMA denetleyici işlev doğrulaması

3.1 Simülasyon doğrulama

Kodu yazdıktan sonra, VIP ortamında bir simülasyon platformu oluşturun ve esas olarak doğrulama modülünün kayıt okuma ve yazma ile DMA okuma ve yazmaya doğru şekilde yanıt verip veremeyeceğini test etmek için, işlevsel testler gerçekleştirmek için Synopsys'in simülasyon doğrulama aracı VCS'yi kullanın.

Şekil 5 ve Şekil 6'dan, yazma adresi ofsetinin 0x40 ve yazma verilerinin 32h87654321; okuma adresi ofsetinin 0x40 ve okunan verilerin 32h87654321 olduğu görülebilir, bu nedenle kaydın doğru okunduğu ve yazıldığı yargılanabilir.

Şekil 7'de gösterildiği gibi, dma_strt ve dma_done sinyalleri iki DMA transferi olarak görülebilir. Dma_wr_rdn'den, ilk zamanın bir DMA okuma işlemi (RC ucundan APP tarafına) ve ikinci zamanın bir DMA yazma işlemi olduğu (uygulama tarafı RC tarafına) Mevcut DMA işlem uzunluğunun 500 DW olan 2000 Bayt olduğu dma_bc_len'den görülebilir. Slv_rdata ve slv_wdata'nın daha yoğun kısımları sırasıyla 2 DMA işleminin verileridir.Bu iki veriyi karşılaştırdığımızda DMA işleminin doğru olduğunu biliyoruz. .

Sonuçları daha rahat karşılaştırmak için otomatik bir dosya karşılaştırma yöntemi benimsenir, yani kayıt defteri veya DMA tarafından yazılan veriler bir dosyada saklanır ve sicil veya DMA tarafından geri okunan veriler başka bir dosyada saklanır.İki dosyayı karşılaştırarak, Kaydı yargılayın ve DMA aktarımı doğru.

3.2 FPGA test doğrulaması

Simülasyon doğrulaması tamamlandıktan sonra, FPGA test doğrulaması gerçekleştirin Donanım parçasını kartın FPGA yongasına yazdıktan sonra, kartın PCIe altın parmağıyla bilgisayarın ana kartına takın.PC yeniden başlatıldıktan sonra, PCIe donanımı algılanır. Ardından ilgili PCIe sürücü yazılımını yükleyebilir ve test etmek için ana bilgisayarı kullanabilirsiniz.

Kayıt okuma ve yazma (Hedef işlem) ve DMA okuma ve yazma (Ana işlem) test modülleri dahil olmak üzere üst bilgisayar yazılımı arayüzü Şekil 8'de gösterilmektedir.

"Hedef" işleminin "ikili" modunu seçin ve kayıt uzunluğunu 118'e ayarlayın. İlk 10 kayıt DMA işlemleriyle ilgili olduğundan ve DMA işlemlerini tetikleyebileceğinden, yazılımda atlamayı seçin. "Testi Başlat" ı tıklayın, veriler ilk olarak ana bilgisayar tarafından FPGA'ya yazılacak ve ardından FPGA'dan ana bilgisayar tarafına okunacaktır.Kayıt işleminin doğruluğunu belirlemek için iki yazmaç işleminin verilerini karşılaştırın.

Şekil 9'da gösterildiği gibi, "Master" işleminin "dual" modunu seçin, "memory" ye tıklayın, yani verileri depolamak için PC tarafında bir bellek açın ve ardından "testi başlat" a tıklayın, veri ilk olarak bilgisayardan FPGA'nın RAM'ine yazılır. Daha sonra FPGA'dan PC'ye geri dönün, PC belleğinde depolanan verileri ve FPGA'dan PC'ye geri yazılan verileri DMA okuma ve yazma işlemlerinin doğruluğunu belirlemek için karşılaştırın.

DMA'nın sabit boyutlu verileri transfer etme süresine göre, DMA okuma ve yazma hızı hesaplanabilir.Birçok testten sonra, DMA okuma ve yazma hızları sırasıyla 1547 MB / s ve 1607 MB / s'dir. Bu tasarım PCIe Gen2, × 4 kanalları kullanır ve teorik maksimum aktarım hızı 2.000 MB / sn'dir. Kodun analizi, uygulamanın PCIe Core IP'ye veri yazmasının ve okumasının biraz zaman alabileceğini göstermektedir.Ayrıca, sürücünün parametreleri DMA kaydına yazması veya okuması da biraz zaman alır, bu da hızı etkileyecektir.

4. Sonuç

Bu belgede uygulanan FPGA tabanlı PCIe veriyolu arabirimi DMA denetleyicisi, Altera PHY IP ve Synopsys Core IP temelinde uygulanmaktadır. İşlev simülasyon doğrulaması, Synopsys VIP doğrulama ortamı kullanılarak gerçekleştirilir ve sistem, nispeten yüksek bir elde etmek için FPGA aracılığıyla test edilir. Yüksek aktarım hızı Gen2 ve × 4 modlarında, DMA okuma ve yazma işlemlerinin bant genişliği sırasıyla 1547 MB / sn ve 1607 MB / sn'dir ve beklenen tasarım hedefine ulaşılır.

Referanslar

Chen Gang, Zhang Jing, Tang Jian. FPGA tabanlı bir PCIe veri yolu ve DMA tasarım yöntemi Ordnance Industry Automation, 2014, 33 (5): 75-77.

Zhang Biao, Song Hongjun, Liu Lin ve diğerleri.PCIE arayüzüne dayalı yüksek hızlı veri aktarım sisteminin tasarımı.Elektronik ölçüm teknolojisi, 2015, 38 (10): 113-117.

NAMBIAR S O S, ABHYANKAR Y, CHANDRABADU S. FPGA tabanlı PCI Express Gen1 tasarımını Gen2.2010 Uluslararası Bilgisayar ve İletişim Teknolojisi Konferansı'na (ICCCT) geçirme. 2010.

Altera Corporation.Stratix V GX FPGA geliştirme kartı referans kılavuzu. Www.altera.com, 2014.

Altera Corporation. Altera Alıcı-Verici PHY IP Core Kullanıcı Kılavuzu. Www.altera.com, 2016.

Altera Corporation IP Compiler for PCI Express Kullanıcı Kılavuzu. Www.altera.com, 2014.

Chen Jing. ARM tabanlı USB2.0-AHB veri yolu köprüsü IP'sinin doğrulama yöntemi ve tasarım uygulaması üzerine araştırma Chengdu: Çin Elektronik Bilim ve Teknoloji Üniversitesi, 2007.

Synopsys.DesignWare PCI Express VIP Kullanıcı Kılavuzu. Www.synopsys.com/products/designware/docs, 2010.

AMBA AXI ve ACE Protokol Spesifikasyonu. Www.arm.com, 2011.

-

- Tam GSM downlink frekans bandında giyilebilir cihazlar için verimli bir radyo frekansı enerji toplama teknolojisi

-

- Akım Tipi Çift Darbe Döngüler Arası Modülasyonlu Buck Konvertörü Üzerine "Akademik Rapor" Araştırması