Çok Kanallı Çift Frekanslı Yüksek Frekanslı Radar Alıcısının Analog Ön Uç Tasarımı

Özet: Gökyüzü-yer dalgası ağ oluşturma sisteminin radar alıcı indeksi gereksinimlerini hedefleyerek, yazılım radyo fikrine dayalı bir çift frekanslı çok kanallı dijital radar alıcısının analog ön ucunun bir tasarımı önerilmiş ve gerçekleştirilmiştir. Tasarım, 8 kanallı eşzamanlı çift frekanslı alıcı sinyalin amplifikasyonunu ve örneklemesini gerçekleştirmek için çekirdek olarak bir analogdan dijitale dönüştürme çipi kullanır, her kanalın kazanç kontrolünün tutarlılığını sağlar, devreyi basitleştirir ve daha fazla esnekliğe sahiptir. Son olarak, alıcının sistem simülasyonu ve saha testi tasarımın doğruluğunu kanıtladı ve gerçek uygulama gereksinimlerini karşıladı.

TN957

Bir

10.16157 / j.issn.0258-7998.173145

Çince alıntı biçimi: Li Shijie, Chen Zhangyou, Zhang Lan, vb. Çok kanallı çift frekanslı yüksek frekanslı bir radar alıcısının analog ön ucunun tasarımı Elektronik Teknoloji Uygulaması, 2018, 44 (2): 31-35.

İngilizce alıntı biçimi: Li Shijie, Chen Zhangyou, Zhang Lan, ve diğerleri.Çok kanallı çift bantlı yüksek frekanslı radar alıcısı için analog ön uç tasarımı.Elektronik Tekniğin Uygulanması, 2018, 44 (2): 31-35.

0 Önsöz

Gök-yer dalgası ağına bağlı yüksek frekanslı yer dalgası radarı, kapsama alanı ile okyanus yüzeyinin dinamik parametrelerini (okyanus yüzey akış alanı, rüzgar alanı vb.) İzlemek için gökyüzü dalgası fırlatma, yer dalgası alımı, yer dalgası fırlatma ve yer dalgası alımı biçimini benimser. Geniş ve yankı, zengin bilgi ve diğer özellikleri içerir. Gökyüzü dalgası gönderen ve yer dalgası alan radarlar, algılama aralığı ve algılama doğruluğu açısından birbirlerini tamamlayabilir.Gök dalgası mesafeyi aydınlatır ve düşük doğruluğa sahiptir; yer dalgası radarı, dalga formu sistemi ve diğer nedenlerle sınırlıdır, bu nedenle algılama aralığı sınırlıdır, ancak yüksek elde edilebilir Bu nedenle doğru veriler, yalnızca algılama aralığının genişletilmesine yardımcı olmakla kalmaz, aynı zamanda yer dalgası algılama alanının ince gözleminin uygulanmasına da elverişlidir.

Gökyüzünden yere dalga ağ bağlantılı radar sisteminin algılama gereksinimlerini dikkate alarak, geniş bir doğrusal dinamik aralık, güçlü anti-parazit yeteneği, orta düzeyde hassasiyet ve çok kanallı alım sağlamanın yanı sıra, alıcının analog ön ucu da değiştirmenin kolay olmasını sağlamalıdır. Parametreler, güçlü çok yönlülük ve yüksek kararlılık. Mevcut yüksek frekanslı yer dalgası radarlarının analog ön uçları çoğunlukla sabit kazançlı analog ön uçlardır ve her frekansın yankı sinyali kazancı ayrı ayrı kontrol edilemez, bu da gökyüzü-yer dalgası ağ modu radar sistemine uygulanması zordur. Gökten yere dalga ağ sisteminin gereksinimlerini karşılamak için, yazılım radyo fikrine dayalı birçok analog ön uç tasarlanmıştır. Literatür, analog sinyallerin örneklemesini tamamlamak üzere sırasıyla 8 alıcı kanalı kontrol etmek için 8 analogdan dijitale dönüştürücü (Analogdan Dijitale Dönüştürücü, ADC) yongası kullanır. Literatür, 4 kanallı yankı sinyali örneklemesini tamamlamak için iki ADC yongası kullanır. Literatür, 8 örnekleme kanalı ve 4 ADC arayüz modülü tasarlamıştır, her ADC arayüz modülü 2 kanallı sinyal işlemeyi tamamlayabilir. Literatür, 6 sensör sinyalinin alınmasını gerçekleştirmek için 6 ADC çipi kullanır. Literatür, zaman paylaşımında 4 kanallı sinyali örneklemek için bir ADC çipi kullanır.

Gökyüzü-yer dalgası ağlı radar sisteminin ihtiyaçlarına dayanarak, bu makale, alıcının orijinal dijital ara frekans alıcısına dayalı olarak tam dijitalleştirilmesini gerçekleştirmektedir.Alıcı, radar istasyonu tarafından alınan radar yankı sinyalini daha karmaşık hale getiren çift frekans modunda çalışmaktadır. Farklı frekanslardaki radyo dalgası sinyallerinin zayıflatma özellikleri mesafeye göre farklıdır ve farklı frekanslardaki eko sinyallerinin dinamik aralığı da farklıdır. Analog sinyalin daha önce dijital bir sinyal haline gelmesini sağlayan ve nihayet çift frekanslı çok kanallı tam dijital yüksek frekanslı radar analog ön ucunun tasarımını tamamlayan, anten ile ADC arasında yalnızca bir ön seçim filtresi vardır. Tasarım, 8 kanallı eşzamanlı çift frekanslı alınan sinyallerin amplifikasyonunu ve örneklemesini gerçekleştirmek için çekirdek olarak bir ADC yongası alır. Alınan sinyallerin 8 kanalı aynı ADC çipine girerek 8 kanalın tutarlılığını sağlar, alınan sinyal üzerinde kanal tutarsızlığının etkisini önler, aynı örnekleme işlemini gerçekleştirir ve alınan sinyallerin 8 kanalının kontrolünü kazanır ve devreyi basitleştirir Daha fazla esneklik kazandı.

1 Çift frekanslı çok kanallı yüksek frekanslı dijital radar alıcısının genel şema tasarımı

Bu makalede araştırılan ve tasarlanan tamamen dijital alıcı, gökyüzü ve yer dalgalarının entegre algılama modunda çalışır ve alıcı-verici ortak sahasının gereksinimlerini karşılamak için Frekans Modülasyonlu Kesintisiz Dalga (FMICW) sistemini kullanır; çalışma frekansı, alımı geliştirmek için çift frekanstır. Makine parazit önleme yeteneği ve kendini düzeltme yeteneği. Alıcı temel olarak GPS senkronizasyonu, sistem saati, yerel osilatör ve iletim sinyali sentezi, veri toplama, dijital aşağı dönüştürme, USB iletimi ve diğer modülleri içerir. Alıcı sistemin genel yapısı Şekil 1'de gösterilmektedir.

2 Alıcının analog ön ucunun tasarımı

Analog ön ucun işlevi, 8 kanal tarafından alınan yankı sinyallerini filtrelemek, yükseltmek ve örneklemek ve ardından verilerin seri-paralel dönüşümünü ve dijital aşağı dönüşümünü (DDC) tamamlamak için dijital sinyalleri FPGA'ya göndermektir. Bu analog ön uç tasarımı, aynı anda 8 kanal alınan sinyalin kontrolünü örneklemek ve kazanmak için bir ADC yongası kullanır ve 8 kanallık yüksek derecede tutarlılık sağlar. Alıcının çalışma frekansı aralığı 3 MHz ~ 20 MHz'dir; tarama süresi ve tarama bant genişliği isteğe bağlıdır; örnekleme frekansı Nyquist örnekleme teoremini karşılamalıdır. Alıcının analog ön ucunun kanallarından birinin sistem tasarımı Şekil 2'de gösterilmektedir.

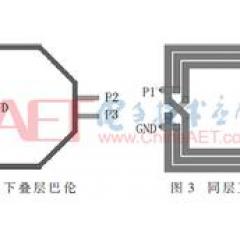

Radar yankı sinyali önce sınır koruması için sınırlayıcıdan geçer, alıcı-verici izolasyon anahtarından geçer (SA630: bu anahtar darbe ile kontrol edilir) ve daha sonra güç bölücü tarafından iki kanala, yani frekans bandı 1 kanalı ve frekans bandı 2 kanalı ve frekans bandı 1 kanalı olarak ayrılır. Filtrenin frekans bandı 3 MHz ~ 11 MHz, frekans bandı 2 filtresinin frekans bandı 12 MHz ~ 20 MHz'dir ve daha sonra birleştirici iki sinyali bir araya getirir ve bunları kazanç kontrolü ve AD örneklemesi için ADC'ye gönderir.

2.1 Amplifikasyon ve örnekleme çipi

Veri toplamanın göstergelerini, özelliklerini ve gereksinimlerini göz önünde bulunduran bu tasarım, yankı sinyalini yükseltmek ve örneklemek için TI'nin AFE5808A yongasını seçer. Çip, küçük boyutlu, yüksek performanslı radar sistemleri için çok uygun olan amplifikasyon, otomatik kazanç kontrolü ve önceki alıcı ön ucunun veri örneklemesi gibi işlevleri entegre ederek son derece entegre edilmiştir. 8 kanallı radar alıcılarının tasarım gereksinimlerini tam olarak karşılayan toplam 8 kanala sahiptir.

2.2 Amplifikasyon ve örnekleme süreci

Veri toplama için AFE5808A kullanılırken, esas olarak 3 aşamaya ayrılır.

Aşama 1 (durum0): ADC'yi başlatın. Tam çip sıfırlama, saat başlatma, güç başlatma vb.

Aşama 2 (durum1): Yapılandırma kaydı. FPGA yongası, ADC kayıt setini, voltaj kontrol amplifikatörünü (VCA), vb. Seri çevresel arabirim (Seri Çevre Birimi Arabirimi, SPI) aracılığıyla yapılandırır.

Aşama 3 (durum2): Verileri okuyun. Yukarıdaki iki aşama tamamlandıktan sonra, AFE5808A çalışmaya başlar ve AFE5808A'daki her eko sinyalinin işlenmesi Şekil 3'te gösterilir.

Sinyal kazancı, bir düşük gürültü amplifikatörü (Düşük Gürültülü Amplifikatör, LNA), voltaj kontrollü zayıflatıcı (VCAT) ve programlanabilir bir kazanç amplifikatörü (Programlanabilir Kazanç Amplifikatörü, PGA) aracılığıyla ayarlanabilir. ADC, analog sinyalleri dijital sinyallere dönüştürür. Amplifiye edilip örneklendikten sonra, 9 dijital sinyal (8 veri ve 1 çerçeve saati), paralel-seri dönüşümden sonra düşük voltaj diferansiyel sinyal (LVDS) şeklinde FPGA'ya dönüştürülür.

2.3 Çip yapılandırması

Bu tasarımda, AFE5808A'nın yazmaçları, sinyal kazanım kontrolü ve örneklemeden sonra dijital sinyalin bit genişliği dahil olmak üzere SPI veriyolu aracılığıyla FPGA tarafından yapılandırılır. Örnekleme oranı, AFE5808A'ya saat frekansı girişi tarafından belirlenir, burada saat çipi tarafından üretilen 48 MHz'e (Nyquist örnekleme teoremine göre) ayarlanır. Uygun ADC doğruluğu, sistemin performansını ve güç tüketimini optimize edebilir.Tespit hedefleri ve gereksinimleriyle birlikte, daha iyi diferansiyel doğrusallığı ve 14 bitte eksik kod olmaması dikkate alındığında, bu sistemin analogdan dijitale dönüşüm doğruluğu 14 bit olarak yapılandırılır. Kayıt değerini değiştirerek, yerleşik LNA'nın kazancı ve VCAT'ın zayıflaması, alıcının dinamik aralığını iyileştirmek için değiştirilebilir.

2.4 Seri - paralel dönüştürme

2.4.1 Veri biçimi

AFE5808A'nın çalışma frekansı 48 MHz'e ayarlanmıştır, yani örnekleme ile 48 MS / s veri hızına ve 14 bit bit genişliğine sahip 8 kanal dijital sinyal üretilir ve paralel seri dönüşümden sonra 672 Mb / s veri hızıyla 8 kanal seri sinyale dönüştürülür. 8 seri sinyal ve 1 çerçeve saati FPGA'ya gönderilir ve diferansiyelden tek uçlu dönüştürme FPGA'daki giriş arabelleğinde tamamlanır.Bundan sonra, Quartus II yazılımındaki ALTLVDS_RX IP çekirdeği kullanılarak seri verilerin serileştirilmesi gerekir Sonraki veri işlemeyi kolaylaştırmak için örneklenen verilerin seriden paralele dönüştürülmesini tamamlayın.

2.4.2 ALTLVDS_RX IP çekirdeğinin konfigürasyonu

ALTLVDS_RX IP çekirdek kanal numarasını, seriyi kaldırma faktörünü, giriş saatini, veri hızını, dinamik faz hizalamasını (Dinamik Faz Hizalama, DPA) etkinleştirme ve diğer parametreleri yapılandırın. AFE5808A, toplam 8 veri kanalı çıkarır ve ayrıca bir çerçeve saati kanalı çıkarır.Bu çerçeve saati, yanlış hizalanmış verilerin sonraki düzeltilmesi için bir referans olarak kullanılır.Bu nedenle, kanal sayısı 9'a ayarlanmıştır. AFE5808A'yı yapılandırırken, analogdan dijitale dönüştürme doğruluğu 14 bit olarak ayarlanır ve ALTLVDS_RX IP çekirdeğinin serileştirme faktörünün maksimum değeri 10'dur. Burada serileştirme faktörü 7'ye ayarlanır, bu nedenle bir veri parçasının iki kez serileştirilmesinin kaldırılması gerekir. Giriş veri hızı 672 Mb / sn'lik seri veri hızına ayarlanır ve IP çekirdeği içindeki faz kilitli döngünün giriş saati, AFE5808A tarafından veri saati Dclk = 336 MHz çıkışına ayarlanır. Sinyal iletim yolunun tutarsızlığından dolayı, eşlik eden saat sinyali ve ADC tarafından seri veri sinyali çıkışı, FPGA içinde seriden paralele dönüşüm için senkronizasyon ünitesine ulaşmadan önce değişen derecelerde gecikme yaşar, böylece senkronizasyon ünitesinin kurulum süresi korunabilir. Zaman tatmin edilemeyebilir, rekabet ve risk oluşabilir. Bu amaçla DPA işlevinin etkinleştirilmesi gerekir, böylece DPA devresi, eşzamanlı saat ile alınan seri veriler arasındaki sapmayı telafi etmek için en iyi fazı otomatik olarak seçer.

3 Alıcı sistemin simülasyonu ve fonksiyonel testi

Sistemin işlevinin ilgili tasarım gereksinimlerini karşılayıp karşılamadığını doğrulamak için, alıcı ön ucunun modülleri üzerinde işlevsel simülasyon ve test yapmak gerekir.

3.1 Alıcı kanal seçicilik testi

Örnekleme için AFE5808A'ya girmeden önce, sinyalin önceden seçilmesi ve filtrelenmesi gerekir ve önceden seçilmiş filtreleme için kanal seçicilik testi gerçekleştirilir.Yüksek frekanslı yolun ve düşük frekanslı yolun test sonuçları sırasıyla Şekil 4 ve Şekil 5'te gösterilmektedir.

Şekil 4'ten kanal 1'in geçiş bandının 3.56 MHz ~ 10.24 MHz, merkez frekansının 6.9 MHz ve bant genişliğinin yaklaşık 6.68 MHz olduğu görülebilmektedir. Şekil 5'den görülebileceği gibi, kanal 2'nin geçiş bandı 12.1 MHz ila 18.4 MHz'dir, merkez frekansı 15.8 MHz'dir ve bant genişliği yaklaşık 6.3 MHz'dir.

3.2 AFE5808 Yapılandırma Kayıt Okuma ve Yazma Fonksiyonunun Doğrulanması

Testte, Quartus II yazılımındaki yerleşik mantık analizörü (SignalTap II), yazma işlemi ve geri okuma işlemi sırasında verileri yakalamak için kullanılır.Konfigürasyon işlem süresi çok kısa olduğu için ilk yakalama, açılış tetikleyicisi olarak ayarlanır. . AFE5808A'nın kayıt okuma fonksiyonunu etkinleştirin.Burada, örnek olarak 8'h04 adresli kaydı alın. Şekil 6'dan, kayıt adresi 8'h04 olan kayıt değerinin 16'h0010 olduğunu görebilirsiniz. Geri okunacak verileri yazmak için SPI veriyolunu kullanın Veri adresi 8'h04 ila AFE5808A, çip, SDOUT portunda bu adreste depolanan verileri seri olarak çıkaracaktır. Yazma işlemi ve geri okuma işlemi verilerini yakalamak için SignalTap II'yi kullanın. Şekil 6'dan, adresi 8'h04 olan kayıt için, hem yazılı değerinin hem de yeniden tekrar değerinin 16'h0010 olduğu görülebilir. AFE5808A kaydının SPI kullanılarak doğru şekilde yapılandırılabileceği doğrulanabilir.

3.3 Seri-paralel dönüşüm simülasyonu

Programın seriden paralele dönüştürme ve yanlış hizalanmış verilerin düzeltilmesi işlevlerini gerçekleştirip gerçekleştiremediğini doğrulamak için tasarlanan seriden paralele dönüştürme programını simüle etmek için ModelSim yazılımını kullanın. 672 Mb / sn hızında 8 kanal için ALTLVDS_RXIP çekirdeğine "11111110000000" döngüsel seri verilerini girmek için test dosyasını kullanın. Şekil 7'de gösterilen simülasyon sonuçlarından, ALTLVDS_RX IP çekirdeğinin, paralel verilerin yanlış hizalandığını gösteren fclk_data = 7b1111000 çerçeve verisini çıkardığı görülebilir. Bununla birlikte, program, verilerin yanlış hizalanmasını otomatik olarak tanır ve karşılık gelen düzeltmeleri yapar ve son olarak 8 kanalın, 14'b1111111000-0000'ün paralel verilerini doğru şekilde çıkarmasını sağlar.

3.4 Seri-paralel dönüşümün işlevsel testi

Analog ön ucun 8 kanalın veri örnekleme işlevini tamamlayıp tamamlayamadığını doğrulamak için, önce AFE5808A yongasının kendi kendini test modunu etkinleştirin ve yonganın SignalTap II'yi kullanarak "11111110000000" sinyal değerine sahip 8 sabit 14 bitlik sinyal çıktısını alın Seri-paralel dönüştürme ve kaydırma işleminden sonraki veriler yakalanır ve yakalama sonucu Şekil 8'de gösterilir.

Şekil 8'den, seriden paralele dönüştürme ve kaydırma işlemlerinden sonra elde edilen 8 kanallı verilerin tamamının 14'h3f80 (11111110000000) olduğu ve FPGA'nın AFE5808A'dan seri sinyali doğru şekilde alabildiğini gösterdiği görülebilir. Bu, yonganın, SPI kullanarak AFE5808A'nın ilgili yazmaçlarını yapılandırdıktan sonra normal çalışabileceğini kanıtlar ve ALTLVDS_RX IP çekirdeği, doğru paralel verileri elde etmek için normal olarak seri-paralel dönüştürme gerçekleştirebilir, böylece tasarım ve yapılandırma doğrudur.

3.5 Tek kanallı örnekleme testi

Tüm analog ön uç tasarımının doğruluğunu daha da doğrulamak için, ADC dönüşümünden sonra dijital sinyalin doğruluğunu onaylamak için çipin girişi olarak bir sinyal kaynağı kullanılır. Giriş sinyali, 7.5 MHz ve 12.5 MHz frekanslı sinüzoidal bir sinyaldir. Ölçümü kolaylaştırmak için kanallardan yalnızca biri test edilir.

(1) Bant 1 örnekleme testi

Sinyal oluşturucunun çıkış frekansını 7,5 MHz'de 800 mV tepeden tepeye değere sahip bir sinüs dalgasına ayarlayın ve sinyalin frekans spektrumunu ölçmek için bir spektrum analizörü kullanın.

Örneklenen dijital sinyali yakalamak için SignalTap II'yi kullanın, yakalama frekansı 48 MHz'e ayarlanmıştır ve dijital sinyal Şekil 10'da gösterilmektedir.

Data_out_ch0 verilerini MATLAB'a aktarın ve üzerinde FFT dönüşümü yapın ve frekans spektrumu Şekil 11'de gösterilmektedir.

(2) Band 2 örnekleme testi

Sinyal oluşturucunun çıkış frekansını 12,5 MHz frekansa ve 800 mV tepeden tepeye değere sahip bir sinüs dalgasına ayarlayın.Şekil 12'de gösterildiği gibi sinyalin frekans spektrumunu ölçmek için bir spektrum analizörü kullanın.

Örneklenen dijital sinyali yakalamak için SignalTap II'yi kullanın, yakalama frekansı 48 MHz'e ayarlanmıştır ve dijital sinyal Şekil 13'te gösterilmektedir.

Data_out_ch0 verilerini MATLAB'a aktarın ve üzerinde FFT dönüşümü yapın ve frekans spektrumu Şekil 14'te gösterilmiştir.

ADC dönüşümü sonrası elde edilen dijital sinyal spektrumunun doğru olduğu, tasarlanan analog ön uçtaki sinyal kaynağı ölçümü sonucundan görülebilmektedir.

4. Sonuç

Bu makale, yüksek frekanslı radar tam dijital alıcının genel şemasını tanıtmakta ve çift frekanslı çok kanallı yüksek frekanslı radar tam dijital alıcının analog ön ucu için bir sistem tasarımı fikri ve yöntemi önermektedir.Bu tasarım, 8 kanal için bir ADC çipinin kullanımını gerçekleştirmektedir. Aynı zamanda, çift frekanslı alınan sinyal, her kanalın tutarlılığını sağlamak, devreyi basitleştirmek ve alıcının esnekliğini artırmak için kazanç kontrolüne ve örneklemeye tabi tutulur. Son olarak, sistem simülasyonu ve fonksiyonel test yoluyla, donanım devresinin ve program tasarımının doğruluğu doğrulandı ve ADC dönüşümünden sonra elde edilen dijital sinyalin sinyal-gürültü oranı 50 dB'ye ulaştı, bu da analog ön ucun radar alıcısı tarafından alınan okyanus yankısını karşılayabileceğini gösteriyor. İşleme gereksinimleri.

Referanslar

Li Zhengyong, Yan Songhua, Liu Zhizhong, ve diğerleri Gökten yere dalga ağa bağlı radar için senkronizasyon kontrol sisteminin tasarımı.Radar Bilimi ve Teknolojisi, 2014, 12 (5): 473-481.

Yang Longquan, Fan Junmei, Wei Na, vd.Gökyüzü / yer dalgası kombine yayılma modunun birinci dereceden deniz karmaşası özelliklerinin analizi.Çin Radyo Bilimi Dergisi, 2012 (4): 703-708.

YANG L, FAN J, WEI N, ve diğerleri Hibrit gökyüzü-yüzey dalgası yayılma modunda birinci dereceden deniz karmaşasının karakteristiği üzerine çalışma. Chinese Journal of Radio Science, 2012, 27 (4): 703-708.

Sun Lijia, Niu Jiling.Yüksek dinamik menzilli alıcı RF ön ucunun araştırılması ve tasarımı Heilongjiang Science and Technology Information, 2009 (20): 11,137.

Liu Jianfei, Wu Xiongbin, Tang Rui, vb. Çok tabanlı ve çok frekanslı ağ oluşturma için uygun yüksek frekanslı ufuk ötesi radar analog ön ucu: Çin, CN205027894U

.2016-02-10.

Tian Yingwei. Çift frekanslı tüm dijital yüksek frekanslı oşinografik radarın geliştirilmesi ve ilgili konularda araştırma. Wuhan: Wuhan Üniversitesi, 2015.

Wang Zheng. 4 kanallı veri toplama IF alıcısının tasarımı ve uygulaması Harbin: Harbin Teknoloji Enstitüsü, 2015.

Li Ming. FPGA'ya dayalı çok kanallı çift frekanslı dijital alıcı tasarımı. Yazılım Kılavuzu, 2016, 15 (8): 80-82.

Cheng Hui, Ren Yongfeng, Wang Qiang, vb. FPGA'ya Dayalı Çok Kanallı Veri Toplama Devresinin Tasarımı ve Uygulanması Elektriksel Ölçüm ve Enstrümantasyon, 2013, 50 (1): 125-128.

Liu Lijun. FPGA'ya dayalı çok kanallı bir veri toplama sisteminin tasarımı. Enstrümantasyon kullanıcıları, 2017, 24 (6): 31-34.

Yang Xiaoniu, Lou Caiyi, Xu Jianliang, vb Yazılım Radyosunun İlkeleri ve Uygulamaları Beijing: Electronics Industry Press, 2001.

Yang Zijie, Ke Hengyu, Wen Biyang, vb. Yüksek frekanslı yer dalga radarının dalga biçimi parametre tasarımı, Wuhan Üniversitesi Dergisi (Science Edition), 2001, 47 (5): 528-531.

Yang Xing, Zhou Hao, Tian Yingwei, vd.Taşınabilir yüksek frekanslı yer dalgası radarı için çift frekanslı alıcı antenin tasarımı ve uygulaması Bilim Teknolojisi ve Mühendisliği, 2015, 15 (10): 97-101.

yazar bilgileri:

Li Shijie, Chen Zhangyou, Zhang Lan, Yang Shanshan

(Elektronik Bilgi Okulu, Wuhan Üniversitesi, Wuhan 430072, Hubei)

-

- "Sergi Raporu" Gelecekteki otomobiller yeni enerjiye doğru hızlanacak. Mitsubishi Electric'in otomotiv sınıfı IGBT'leri tam yanıt veriyor

-

- 10.000 kişinin katıldığı dünyanın en büyük büyük veri zirvesine Splunk'ın büyük veriyi nasıl yorumladığını dinlemek ister misiniz?