FPGA'ya Dayalı HD Video Alma Sisteminin Tasarımı

Video görüntüleme teknolojisinin gelişmesiyle, video sinyali önceki standart tanımdan yüksek çözünürlüğe ve ardından tam yüksek çözünürlüğe doğru gelişti.Çözünürlüğü gittikçe yükseliyor ve veri miktarı iki katına çıktı.Bu, ekran arayüz teknolojisinin hızlı gelişimini teşvik etti. Arayüz teknolojisi, analogdan dijitale, paralelden seriye ve düşük hızdan yüksek hıza doğru bir gelişim sürecinden geçmiştir. HDMI arayüzü, en yeni yüksek çözünürlüklü multimedya arayüzüdür.DVI arayüzü ile karşılaştırıldığında boyutu daha küçüktür, bant genişliği daha büyüktür, iletim mesafesi daha uzundur ve desteklenen çözünürlük daha yüksektir.Sadece video sinyallerini iletmekle kalmaz, aynı zamanda ses sinyallerini de iletebilir. Ve telif hakkı koruması işlevine sahiptir. HDMI arabirimi, LCD monitörlerin, tablet bilgisayarların, dizüstü bilgisayarların ve diğer ekipmanların standart arabirimlerinden biri haline geldi ve yaygın olarak kullanılmaktadır. Bu sistem sadece standart HDMI arayüz devresini ve kontrolünü uygulamakla kalmaz, aynı zamanda full HD video veri kaynağı sağlar.5 milyon piksel seviyeli CMOS kamera OV5640 seçilir ve çıkış video sinyali çözünürlüğü 2K seviyesine ulaşabilir ve çoklu veri formatı çıkışını destekler. Yetersiz video veri önbellek hızı ve kapasitesinden kaynaklanan leke sorununu çözmek için, sistem önbellek değiştirme ortamı olarak 4 Gbit DDR3SDRAM'i seçer ve sorunu etkin bir şekilde çözebilecek ping-pong işlemiyle birlikte Xilinx'in MIG IP'si aracılığıyla kontrol eder. Yüksek veri ve büyük kapasiteli verilerin önbellek sorunu, görüntü kalitesini yükseltir. Bu sistem, full HD video sinyallerinin toplanmasını ve yüksek kaliteli görüntülenmesini gerçekleştirir ve askeri gözetim alanı, multimedya alanı, tıbbi alan vb. Dahil olmak üzere birçok alana uygulanabilir.

1 Şema tasarımı

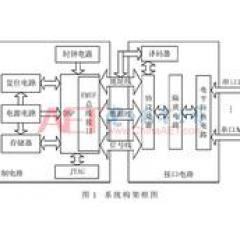

Bu video edinme ve görüntüleme sisteminin temel blok diyagramı Şekil 1'de gösterilmektedir. Sistem, temel olarak bir video toplama modülü, bir FPGA ana kontrol modülü, bir veri tampon modülü ve bir HDMI arayüz devresi içerir. Video yakalama modülü, tam bir HD video veri kaynağı sağlar. Yakalamaya başlamadan önce, FPGA ana kontrol modülünün kamera yapılandırma bilgilerini SCCB (Seri Kamera Kontrol Veriyolu) veriyolu aracılığıyla kameradaki kayıt defterine göndermesi gerekir; FPGA ana kontrol modülü, bu sistemin kontrol merkezidir , Kamerayı, DDR3-SDRAM'ı, HDMI arabirim yongasını ve video veri akışını kontrol eden; veri önbellek modülü, önbellek ortamı olarak 4 Gbit kapasiteli bir DDR3-SDRAM kullanır ve bu, yüksek hızlı ve yüksek kapasiteli verilerin önbellek sorununu etkili bir şekilde çözebilir; HDMI arabirim devreleri temel olarak şunları içerir İşlevi, video verilerinin paralelden seriye dönüştürülmesini gerçekleştirmek olan bir HDMI arabirim yongası; son olarak, seri video verileri HDMI arabirimini destekleyen ekrana HDMI iletim hattı üzerinden iletilir ve tam HD video görüntüsü gerçek zamanlı olarak görüntülenebilir.

2 Ana donanım devre tasarımı

2.1 Video yakalama modülü

Video yakalama modülü OmniVision'ın 5 milyon piksel seviyeli bir CMOS görüntü sensörü olan OV5640 kamerasını kullanır, 2K'ya kadar çözünürlüğü destekler, çeşitli görüntü formatlarında veri çıkışı sağlayabilir ve çoklu uyarlamalı ayarlama işlevlerini destekler. Bu CMOS görüntü sensörü iki veri arayüzünü, DVP ve MIPI'yi destekler ve bu sistemde DVP arayüzü seçilir. Ana kontrol modülü verileri almadan önce, sensör kayıt bilgilerinin SCCB veri yolu aracılığıyla sensöre yapılandırılması gerekir. Bu sistemdeki CMOS görüntü sensörünün görüntü veri çıkış formatı RGB24, video çözünürlüğü 1920 × 1080 (full HD) ve video kare hızı 30 f / s olarak yapılandırılmıştır.Bu modül ayrıca dijital ve analog güç kaynağı devrelerini de içermektedir.

2.2 FPGA ana kontrol modülü

Sistem kontrol çekirdeği için seçilen yonga, Xilinx'in Spartan6 serisi yonga XC6SLX45'tir. Altıncı nesil Spartan serisi ürün Spartan6 FPGA, gelişmiş güç tüketimi sağlayan tanınmış düşük güçlü 45 nm, 9-metal bakır katman ve çift geçitli oksit işleme teknolojisine dayanmaktadır. Yönetim teknolojisi, 150.000 mantık birimi, sabit çekirdekli DRAM bellek ve çeşitli IP'ler, vb., Xlinx'in çok gelişmiş teknolojiye sahip en yaygın kullanılan FPGA serisidir. FPGA ana kontrol modülü temel olarak kamera konfigürasyonu ve video veri toplama, DDR3-SDRAM veri erişimi, HDMI arayüz çip konfigürasyonu ve video veri iletimini tamamlar.Donanım devresi ayrıca güç kaynağı devresi, sıfırlama devresi, kristal osilatör devresi, indirme devresi ve konfigürasyonu içerir SPI Flaş devresi.

2.3 Veri Önbellek Modülü

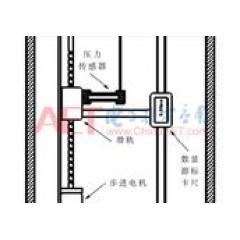

Bu sistem, yüksek hızlı ve büyük kapasiteli video verilerinin önbellek problemini çözmek için, önbellek ortamı olarak Micron'un 4 Gbit kapasiteli DDR3-SDRAM bellek yongası MT41J256M16HA-125'i kullanır.FpAG ile donanım bağlantısının şematik diyagramı Şekil 2'de gösterilmiştir. A0 A14 adres yollarıdır, B0 B3 Banka adresleridir, FPGA, adres veriyolu ve banka adresini kontrol ederek DDR3-SDRAM'deki verilerin depolanma konumunu kontrol edebilir; D0 D15, FPGA ile paralel bağlanan veri yollarıdır; CLK-N CLK-P ve CLK-P, diferansiyel saat giriş portlarıdır, bu sistemde saat frekansı 312,5 MHz'e ayarlanmıştır; FPGA, sütun adresi seçim sinyali (CAS), satır adresi seçim sinyali (RAS), DDR3-SDRAM'a yazma etkinleştirme sinyali (WE) kullanır Veri hattı kesintisi yansımasını önlemek için performansı optimize etmek üzere yonga üzerindeki direnci etkinleştirmek için ODT'yi kontrol ederek okuma ve yazma kontrolü; DQS, DDR3-SDRAM ile çift yönlü bir sinyal olan kontrolör arasındaki bir senkronizasyon sinyalidir, veri yazılırken, Veriler okunduğunda bellek tarafından gönderilir; DM veri maskesi sinyalidir. Spartan6 serisi FPAG'nin yalnızca Bank1 ve Bank3'ü MCB sabit çekirdeklerine sahip olduğundan, bu sistemde, Bank3'ü DDR3-SDRAM'a bağlamak için FPGA'yı seçin, bağlantı noktası voltajı standardı 1,5 V'tur ve FPAG UCF'de IO standardının SSTL15_II'ye ayarlanması gerekir.

2.4 HDMI arayüz modülü

Bu sistemde HDMI çıkış arabirim yongası olarak SiI9134'ü seçin, FPAG ile donanım bağlantı ilişkisi Şekil 3'teki gibi gösterilmiştir. Çip çalışmadan önce, kayıt bilgilerinin I2C (SCL, SDA) veriyolu aracılığıyla yongaya yapılandırılması gerekir.Yapılandırma sırasında, frekans 100 kHz'dir, veri giriş biçimi RGB24 olarak yapılandırılır ve video çıkış çözünürlüğü 1920 × 1080; CLK olarak yapılandırılır Bu, video veri senkronizasyon saatidir.Bu çipin 1080p video formatı saati 148,5 MHz'dir.DE veri geçerli sinyaldir ve yüksek seviye geçerlidir; HS ve VS sırasıyla hat senkronizasyon sinyali ve alan senkronizasyon sinyalidir; D, üstten RGB24 veri giriş veriyoludur Diğer video veri formatlarını desteklemek için, SiI9134'ün veri yolu genişliği 36 bittir.Bu sistemde sadece 24 bit kullanılır ve veri yolu pinlerinin geri kalanı topraklanır; SiI9134 çeşitli dijital sesleri destekler S / PDIF, I2S vb. Dahil olmak üzere sinyal giriş arabirimi, ses arabirimi bu sistemde kullanılmaz. RGB24 formatındaki video verileri SiI9134 tarafından kodlanır, seri verilere dönüştürülür ve ardından konektör ve iletim hattı aracılığıyla ekrana gönderilir ve son olarak tam HD videoyu görüntüler.

3 Kontrol mantığı tasarımı

Bu sistemin kontrol mantığı tasarımı, OV5640 konfigürasyonu ve video verisi toplama mantığı, DDR3-SDRAM veri erişim kontrol mantığı, SiI9134 konfigürasyonu ve video veri gönderme mantığını içerir. Sistem, video verilerini RGB24 formatında DVP bağlantı noktası üzerinden alır, ardından video verilerini alana göre DDR3-SDRAM'de depolar ve ardından video verilerini buradan okur ve ekranda görüntülenmek üzere HDMI arabirim yongasına gönderir. Sistem iş akışı Şekil 4'te gösterilmektedir. Güç açıldıktan sonra, sistem ilk olarak sıfırlanır ve ardından başlatma durumuna girer.Sistem yapılandırma bilgilerini OV5640 ve SiI9134'e gönderir ve DDR3-SDRAM de başlatma ve doğrulama sürecine girmeye başlar. Tüm başlatma çalışmaları tamamlandıktan sonra, sistem OV5640 konfigürasyonunun bitip bitmediğine karar verir Konfigürasyon bittiyse, sistem video verilerini alacak ve DDR3-SDRAM'da saklayacaktır. Arabellek alanında veri olduğunda ve SiI9134 yapılandırıldığında, sistem arabellek alanındaki video verilerini okur ve bunu SiI9134'e gönderir.

3.1 Video yakalama kontrol bölümü

OV5640'ın açılış sekansında belirli gereksinimleri vardır, bu nedenle bu açılış sırasını karşılayan modüller vazgeçilmezdir.Başlatma tamamlandıktan sonra, önce SCCB veriyolu üzerinden tamamlanabilen OV5640'ın çalışma modunu belirleyin.Bu sistem 303 konfigürasyona sahiptir. Kayıt; OV5640 yapılandırması tamamlandıktan ve DDR3-SDRAM başlatma ve kalibrasyonu tamamlandıktan sonra video verileri elde edilebilir; OV5640'ı kontrol etmek için 192 MHz olan bir sistem saati XVCLK sağlamanız ve ardından piksel çıkış saatini (PCLK) ve alan senkronizasyon sinyalini (VSYNC ), veri almak için hat senkronizasyon sinyali (HREF). Dikey senkronizasyon sinyalinin düşen kenarı, bir veri çerçevesinin başlangıcını gösterir.Yatay senkronizasyon sinyali yüksek olduğunda, geçerli veri çıkışıdır.Dikey senkronizasyon sinyalinin düşük seviyesi arasında, yatay senkronizasyon sinyali 1.080 kez yüksek seviyede görünecektir, bu da bir veri çerçevesi olduğu anlamına gelir. 1080 satır veri; Hat senkronizasyon sinyalinin yüksek bir seviyede olduğu, satır başına 1920 pikseli temsil ettiği dönemde 1920 piksel çıkış saati devam edecektir.

3.2 DDR3-SDRAM önbellek kontrol bölümü

DDR3-SDRAM veri erişimi, Spartan6 serisi FPGA tarafından sağlanan MIG IP çekirdeğini kullanır ve aynı zamanda, harici SDRAM yongası ile veri alışverişi yapmak için MCB sert çekirdeği gerekir. Xilinx derleme ortamı ISE'de SDRAM denetleyicisi oluşturulduktan sonra, MIG IP çekirdek kullanıcı arabirimi veri erişimi için kullanılabilir.Bu sistemde, MIG IP çekirdeği, 64 bit bit genişliğinde iki çift yönlü bağlantı noktası olarak yapılandırılır, bir bağlantı noktası veri yazmak için kullanılır , Verileri okumak için bir port kullanılır. Çalışma durumunun şematik diyagramı Şekil 5'te gösterilmektedir. MIG IP çekirdeğinin ön ve arka uçlarına, sırasıyla bir yazma verisi FIFO ve bir okuma verisi FIFO eklenir.Bu tampon modülünü çağırmanın mantığı için, büyük kapasiteli bir FIFO'ya eşdeğerdir. MIG IP çekirdeğinin içinde, önbellek verimliliğini artırmak için ping-pong işlemi kullanılır Önbellekleme sürecinde, 4 Gbit depolama alanı N alana bölünür ve her alanın kapasitesi bir video verisi çerçevesinin kapasitesidir. İçe aktarma sürecinde önce verileri ilk alana yazın ve ilk alan dolduktan sonra bir alan yazmaya başlayın (bu ikinci alandır, bir alan yazarken alandaki verilerin boş olduğundan emin olun), sonra ilk alanı okuyabilirsiniz Alan 1'deki veriler, ilk alanı okuduktan sonra, sonraki alanı (ikinci alan, sonraki alanı okurken alandaki verilerin dolu olduğundan emin olun) verileri okuyun, ping-pong işlemini tamamlamak için bu sırayla okuyun ve yazın. Bu önbelleğe alma yöntemi, video verilerinin önbelleğe alınmasının verimliliğini büyük ölçüde artırabilir ve yüksek hızlı ve büyük kapasiteli veri önbelleğe alma sorununu etkili bir şekilde çözebilir. Bir video verisi çerçevesi, veri geçişi olmadan süreklidir (adresler kesişmez) ve video görüntüsünün bulaşmasını önler fenomen.

3.3 HDMI arayüzü kontrol bölümü

HDMI çalışmadan önce, kayıt için verileri I2C veriyolu üzerinden yapılandırmak gerekir.Veri formatı RGB24 olarak yapılandırılır, çözünürlük 1920 × 1080 ve video kare hızı 30 f / s'dir. Yapılandırma tamamlandıktan sonra, ara bellek alanı dolduğunda, video verileri okunabilir ve belirli bir zamanlamaya göre SiI9134'e gönderilebilir.SiI9134'ün veri iletim zamanlaması Şekil 6'da gösterilmektedir. Hat senkronizasyon sinyalinin düşen kenarı, bir video verisi çerçevesinin başlangıcını ve yükselen kenarı temsil eder. Bir veri çerçevesinin sonunu temsil eder. Bir veri satırı gönderildiğinde, sonraki veri satırı gönderilir. Bir veri çerçevesinin son satırı gönderildiğinde, sonraki çerçevenin ilk veri satırı gönderilir. Verileri tekrarlanan bir döngüde gönderin, DE veri geçerli sinyaldir ve yüksek seviye geçerlidir.

4 Test sonuçları

Donanım devresinin elektriksel performans testi tamamlandıktan sonra, genel performans testi başlar.Genel performans testinden önce, FPGA programında fonksiyonel simülasyon ve zamanlama simülasyonu gerçekleştirmek ve ardından kodun doğru olduğundan emin olmak için her bir fonksiyonel modülü ayrı ayrı test etmek gerekir.

4.1 DDR3-SDRAM testi

DDR3-SDRAM kodunu test etmek için Xilinx tarafından sağlanan ChipScope Pro aracını kullanın.Test sırasında, sistem içinde üretilen artımlı sayı FIFO yazma verisine yazılır ve daha sonra veriler okunan veriler FIFO'dan okunur ve yazılan veriler ile birleştirilir. Okunan veriler ChipScope Pro aracı tarafından yakalanır ve ardından yakalanan dalga formu çizilir ve karşılaştırılır Test sonucu Şekil 7'de gösterilir. Test sonuçlarına göre okuma ve yazma hızı hızlıdır ve sistem gereksinimlerini karşılayan bozuk veri yoktur.

4.2 HDMI arayüz testi

HDMI arayüz modülünün test sonucu Şekil 8'de gösterilmektedir. Test sırasında, üç ana renk, dama tahtası ve renk çubukları gibi veriler dahil olmak üzere video veri kaynağı sistem tarafından dahili olarak üretilir.Son olarak seri veriler 1080p çözünürlüğü destekleyen bir monitöre gönderilir. Test sonuçlarından, görüntü efekti gereksinimleri karşılar.

4.3 Genel sistem testi

Şekil 9, sistemin genel test sonuçlarını göstermektedir Test sırasında, video veri kaynağı kamera tarafından toplanan video verileridir.Veri, DDR3-SDRAM tarafından arabelleğe alınır ve ardından HDMI arabirim yongasına gönderilir ve ardından diferansiyel veriler HDMI konektörüne ve iletim hattına iletilir. monitör. Test sonuçlarından, Şekil 9 (a) 'da gösterildiği gibi, video görüntüsü net ve tamamlanmıştır; Şekil 9 (b)' de gösterildiği gibi, kamera hareket ettiğinde, görüntü herhangi bir leke fenomeni göstermez, bu da DDR3-SDRAM üzerinden yüksek verimli önbellek ve ping-pong İşlemlerin kombinasyonu, yüksek hızlı ve büyük kapasiteli verilerin önbellek sorununu etkili bir şekilde çözebilir.

5. Sonuç

İnsanların video görüntüleme kalitesi talebini karşılamak için, bu sistem tam bir HD video yakalama ve görüntüleme sistemi tasarladı.Sistem, ön uç yakalama kamerası olarak OminiVision'ın 5 milyon piksel seviyeli CMOS görüntü sensörü OV5640'ı ve ana kontrol olarak Xilinx'in Spartan6 serisi FPGA'sını kullanıyor. Çip, önbellek yongası olarak 4 Gbit kapasiteli DDR3-SDRAM kullanır ve verimli video verilerini önbelleğe almak için MCB sabit çekirdek, MIG IP çekirdeği ve ping-pong işlemi ile birlikte kullanılır; aynı zamanda Silion Image'ın SiI9134'ü, tam HD videoyu etkin bir şekilde destekleyebilen HDMI yongası olarak kullanılır . Sistem, yüksek görüntü kalitesiyle ve lekelenme olgusu olmadan tam HD videoyu kararlı bir şekilde toplayabilir ve görüntüleyebilir.Sistem askeri gözetim sistemlerine, sivil multimedya sistemlerine ve tıbbi alanlara uygulanabilir.

Referanslar

Huang Qingmin, Luo Jian. HDMI arayüz standardı ve uygulama tasarımı Televizyon Teknolojisi, 2007 (2): 32-34.

Gu Haifeng, Xia Ning, Wu Jie. CH7301C'ye dayalı bir ekran arayüz devre tasarımı. Information Research, 2012, 38 (6): 30-34.

Liu Jia. Yüksek hızlı dijital görüntü elde etme ve aktarım teknolojisinin araştırılması ve uygulanması Tianjin: Tianjin Üniversitesi, 2014.

Li Xianyou, Zhao Shuguang, Duan Yongcheng, vb. FPGA tabanlı gerçek zamanlı MIPI CSI-2 görüntü toplama ve işleme sistemi Elektronik Teknoloji Uygulaması, 2019, 45 (1): 97-100.

Pan Lei, Ge Zhongqin, Zhuang Jianjun ve diğerleri.FpGA'ya dayalı HDMI video akışı görüntü işlemenin sistem tasarımı.Laboratuvar araştırması ve keşfi, 2015, 34 (10): 76-80.

Xiang Zihao, Lu Anjiang. HDMI çok modlu ekran modülünün FPGA tabanlı tasarımı.Elektronik Teknoloji Uygulaması, 2017, 43 (12): 48-51.

Chen Yibo, Yang Yuhua, Wang Hongliang, vb. DDR3-SDRAM tabanlı görüntü edinme ve görüntüleme sistemi Elektronik Cihazlar, 2017, 40 (3): 702-707.

Zhou Hao, Wang Haoquan, Ren Shilei.FpGA ve NAND Flash'a dayalı taşınabilir bir sinyal toplama sisteminin tasarımı.Elektronik Teknoloji Uygulaması, 2018, 44 (9): 82-86.

Lin Moujin, Lin Ziwei. DVI arayüzü ile HDMI arayüzünün karşılaştırılması China Cable Television, 2005 (6): 581-582.

Yang Fan, Zhang Hao, Ma Xinwen, vb FPGA tabanlı görüntü işleme sistemi Huazhong University of Science and Technology (Natural Science Edition), 2015, 43 (2): 119-123.

Song Haizha, Tang Lijun, Xie Xinhui.FpGA ve OV7620'ye dayalı görüntü edinimi ve VGA ekranı. Television Technology, 2011, 35 (5): 45-47.

Li Hua.FpGA'ya dayalı yüksek hassasiyetli görüntü toplama sistemi tasarımı Elektronik Cihazlar, 2014, 37 (5): 840-843

Pan Ming, Chen Yuanzhi, Li Qiang.FpGA tabanlı görüntü toplama sisteminin tasarımı.Yabancı Elektronik Ölçüm Teknolojisi, 2012, 31 (3): 58-61.

yazar bilgileri:

Wang Shaobin, Su Shujing, Yuan Caiyuan

(Eyalet Elektronik Test Teknolojisi Laboratuvarı, Çin Kuzey Üniversitesi, Taiyuan, Shanxi 030051)

-

- Hırsız, hırsızı yakalamak için bağırır! Takım arkadaşları bir kaza geçirdiğinde netizenler öfkelidir: Holden konuşmak için dışarı çıkar