Düşük voltajlı yüksek performanslı operasyonel amplifikatör tasarımı

Hu Qiyu, Chen Yimin, Peng Song

(Bilgi Mühendisliği Okulu, Guangdong Teknoloji Üniversitesi, Guangzhou, Guangdong 510006)

Düşük voltajlı, yüksek performanslı bir işlemsel amplifikatör, 0,18 m CMOS standart prosesi temel alınarak tasarlanmıştır. Negatif geri beslemeli üç dallı referans akım kaynağı ve pozitif geri besleme döngüsü kazancı iyileştirmeli CMOS kaynağa bağlı diferansiyel giriş aşaması devresi açıklanmaktadır. Frekans kompanzasyonu fikrine dayanarak, işlemsel kuvvetlendiricilerin sistem performansını etkin bir şekilde iyileştirebilecek yeni bir frekans kompanzasyon yöntemi önerilmiştir. Yerleşim sonrası simülasyon, işlemsel yükselticinin 1,2 V besleme voltajı altında 109 dB DC kazancı, 259 MHz kazanç bant genişliği, 74 ° faz marjı ve çoğu devrede yaygın olarak kullanılabilen 0,82 mW güç tüketimine sahip olduğunu göstermektedir.

Düşük voltaj; üç dallı referans akım kaynağı; pozitif geri besleme döngüsü; ileri besleme kompanzasyonu

TN432 belge tanımlama kodu: ADoi: 10.19358 / j.issn.16747720.2016.23.008

Hu Qiyu, Chen Yimin, Peng Song.Düşük voltajlı yüksek performanslı işlemsel amplifikatör tasarımı J. Mikrobilgisayar ve Uygulama, 2016, 35 (23): 28-30.

0 Önsöz

Operasyonel amplifikatör, gerçek elektronik ürün tasarımındaki en temel modüldür.Elektronik ürünler uygunluk yönünde gelişmeye devam ettikçe, bunun için voltaj gereksinimleri azalıyor.Şu anda, düşük voltajlı operasyonel amplifikatörlerin performansını iyileştirirken, en çok dikkat etmeye değer. Geliştirme eğilimi, yapının [1] iyileştirilmesidir. Bu yazıda, diferansiyel giriş MOS çift tüpünün eşik altı bölgede çalışmasını sağlamak için yeni çerçeve yapısına bir eşik altı çalışma devresi dahil edilmiştir Devre eşik altı durumda çalıştığı zaman akım küçüktür, böylece güç tüketimini azaltır. Giriş aşaması diferansiyel çiftinin yükü, pozitif geri beslemeli çapraz bağlı bir yapı benimser ve giriş tüpünün transkondüktansını artırarak kazanç geliştirilir. Frekans kompanzasyonu, geleneksel sıfır kutup ayrımını Miller kapasitör kompanzasyon teknolojisi ile değiştirmek için yeni bir ileri besleme teknolojisi kullanır.

1 İşlemsel yükselticinin devre gerçekleştirilmesi

Bu makalede tasarlanan taşıma ve deşarj yolu, Şekil 1'de gösterildiği gibi bir öngerilim modülü, iki aşamalı bir yükseltme modülü ve bir ileri beslemeli telafi devresinden oluşur. Bunların arasında, öngerilim devresi referans akımı sağlar; iki aşamalı yükseltme modülü, işlemsel yükselticinin çekirdek devresidir; ileri besleme modülü, sistemi kararlı hale getirmek için işlemsel yükselticiye belirli bir kazanç ve frekans telafisi sağlar.

1.1 Üç dallı referans akım kaynağı

Referans akım kaynağı, diğer devreler için yüksek hassasiyet, düşük sıcaklık katsayısı sağlamak için analog entegre devrelerde kullanılan bir akım kaynağıdır ve devrede [2] vazgeçilmez bir modüldür. Op amp'e sağlanan referans akımın güç kaynağı reddetme oranını (PSRR) iyileştirmek ve VDD ile referans akım değişikliğini daha az yapmak için tasarım, üç dallı bir referans akım kaynağı yapısını benimser. resim 2'de gösterildiği gibi.

Referans devresi MOS tüpleri M1 ~ M6 ve direnç R'den oluşur. Bu devre, negatif geri besleme oluşturmak için kullanılan sıradan referans akım kaynağı temelinde güç kaynağından R direncinin üst ucuna toprağa M5 ve M6'dan oluşan üçüncü bir dal ekler. Çalışma prensibi: Güç kaynağı voltajı pozitif yönde arttığında, ID5'in A noktasındaki voltaj artar ve M2'nin B drenajındaki voltajın düşmesine neden olur.M1 tüpünün etkisi altında, ID1'in C noktasındaki voltaj artar ve M6 da ortak bir kaynak aşaması olarak kullanılır Eylem altında, ID6'nın A noktasındaki voltaj azaltılır ve negatif bir geri besleme döngüsü oluşturur.

Negatif geri besleme sisteminin kazancını artırmak için, M6 kaynağı ve M2 kaynağı birbirine bağlanır ve ardından voltaj farkı oluşturan R direncinin üst ucuna bağlanır.Aynı şekilde, güç kaynağı voltajı pozitif dalgalandığında, M5'in boşaltma terminali A'daki voltaj artar ve M5, M4 tüpünün VSG'si azalacak, ID5 ve ID4 azalacaktır Rezistör R'nin her iki ucundaki VR = (ID5 + ID4) × R voltajı ile elde edilir. Direnç R'nin üst ucundaki voltaj hızla düşer, böylece M5'in boşaltma voltajı hızla düşer. Devre, güç kaynağı voltaj değişiminin sistem üzerindeki etkisini baskılayarak daha hızlı bir negatif geri besleme oluşturur.

Aynalanmış akım IREF'in değerini daha doğru hale getirmek için devrede ID3 = ID4 olması, yani M3 ve M4'ün her bir ucundaki voltajların ofset olması gerekir. Şekil 2'de gösterildiği gibi, M5, M4 ve M3 bir akım aynasını oluşturur ve M7-M9 başlangıç devresidir. M5'in kaçak akımını ve M6'nın en boy oranını VGS6'yı VGS2'ye eşit yapacak şekilde ayarlayarak, VD1 = VD6 = VS2 + VGS6 = VS2 + VGS2 = VD2, M3 ve M4'ün kaynak ve kapı terminallerinin her ikisi de astar ile hizalı olduğundan, VD3 = VD4 elde eder. Alt kısım doğrudan bağlı, çalışma durumu aynı, bu yüzden

Doyma bölgesinde çalışan MOS tüpünün kaynak-boşaltma akımı şu şekilde ifade edilir:

MOS tüpünün geçit uzunluğu, kanal uzunluğu modülasyon etkisini göz ardı etmek için tasarımda artırılmıştır. Yukarıdaki formülde VDS ihmal edilebilir. MOS tüpü kritik satürasyon durumundayken, kaynak boşaltma akımı ifadesi şöyledir:

Devrede, R = (ID5 + ID4) × R direncinin ürettiği kaynak voltaj farkı VR, üçüncü kol M5 ve M6'dan geçen akım başlangıçta referans akım kaynağının N katı olacak şekilde tasarlanmıştır, yani ID5 = N · ID4, Yukarıdaki formül elde edilebilir:

İşte sipariş:

bu nedenle:

Yukarıdan, güç kaynağı voltajı VDD'den bağımsız bir çıkış referans akımının elde edildiği görülebilir. Direnç R'den geçen iki dal akımı olduğundan, üçüncü dal M5 ve M6'dan geçen akım referans akımının N katıdır Denklem (6) 'dan hem N hem de R'nin IOUT ile ters orantılı olduğu ve sabit bir çıkışın istendiği görülebilir. Referans voltajı IOUT ve N arttığında, rezistör R'nin değeri büyük ölçüde azaltılabilir ve böylece çip yerleşim alanı tasarrufu sağlanır. (N bu tasarımda 4 alır).

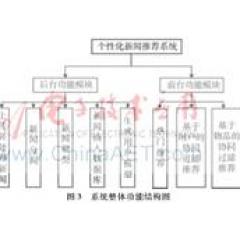

1.2 Pozitif geri besleme çapraz kuplajlı diferansiyel giriş katı

CMOS devrelerinde, devrenin üzerinde çalışabileceği en düşük voltaj bir yandan belirli devrenin yapısına, diğer yandan CMOS cihazının eşik voltajına ve onun aşırı hız voltajına bağlıdır [3]. Pozitif geri beslemeli çapraz kuplajlı diferansiyel giriş aşaması devresi Şekil 3'te gösterilmektedir.

Orijinal M3 ve M4 MOS diyot yüklerine iki adet çapraz bağlı pozitif geri besleme yükü, M5 ve M6 eklenir. Minimum çalışma güç kaynağı voltajının 1 VTP ve 3 aşırı hız voltajının toplamı olduğu devreden görülebilir.VTH = 0,5 V ile MOS teknolojisi kullanılarak minimum çalışma voltajı yaklaşık 1 V azaltılabilir. Belirli bir derecede yedeklilik ayırmak için, bu tasarımın güç kaynağı 1,2 V kullanır.

Diferansiyel çift tüp M1 ve M2, güç kaynağı voltajının uygun şekilde azaltılması için yararlı olan, eşik altı bölgede çalışmak üzere devrede ayarlanır. M5 ve M6 ekleyerek, devre giriş geçirgenliği:

Formülde gm1, M1 tüpünün içsel geçirgenliğidir ve giriş tüpünün geçirgenliğinin 1 / (1-gm6 / gm3) faktörü kadar arttığı görülebilir. Bu yöntemi kullanarak kazanç şu şekilde geliştirilir:

1.3 İleri beslemeli tazminat

Bu makale, düşük voltaj koşullarında geleneksel birincil ve ikincil kutup ayırma Miller kapasitör kompanzasyon teknolojisinin yerini almak için ileri besleme kompanzasyon teknolojisini kullanır. Frekans kompanzasyonu, kutbun [5] neden olduğu negatif faz kaymasını iptal etmek için yüksek frekans bandında sol yarım düzlemin sıfır noktasının pozitif faz kaymasını tanıtmak için ileri besleme yolunu kullanmaktır. Şekil 4'ten op amp'in transfer fonksiyonunun iki kutba ve bir sol yarım düzlem sıfıra sahip olduğu görülebilir, burada p1 ve Z1:

Yukarıdaki formülde, O1, ilk kazanç aşamasının çıkış düğümünün toplam parazitik kapasitansıdır, go çıkış iletkenliğidir ve geri bildirim faktörüdür.

İleri besleme telafisi devresi ve ikinci kazanç aşaması Şekil 4'te gösterilmektedir. M8 M11, ikinci amplifikasyon kazanç aşamasıdır; M3 / M14 ileri besleme aşamasıdır; M12 ve M17, ilgili kuyruk akımı tüpleridir.

İkinci aşama ve ileri besleme aşaması (A3) amplifikatörünün DC kazançları, ifadeler şunlardır:

İkinci kademe ve ileri besleme kademesinin polarlama akımını ve boru genişliği-uzunluk oranını ayarlayarak, sıfır noktasının sol yarı düzlemde olması sağlanır.

2 Simülasyon sonuçları

0.18 m CMOS standart sürecine dayanan işlemsel yükselticinin yerleşim fotoğrafı Şekil 5'te gösterilmektedir. İşlemsel yükselticinin devre düzeni Cadence ortamında simüle edilir. 1,2 V çalışma voltajı ve 2,5 pF kapasitif yük altında, açık döngü kazancı ve faz eğrisi Şekil 6'da gösterilmektedir. Bu yapı 109 dB kazanç, 259 MHz birim kazanç bant genişliği ve yaklaşık 73,8 ° faz marjı elde edebilir; Şekil 7 Düşük frekansta -80.16 dB'ye ulaşabilen devre ortak mod reddetme oranı eğrisidir.

Bu makalenin performans parametreleri Tablo 1'de gösterildiği gibi ilgili literatür ile karşılaştırılmıştır. Tablodan, bu makalenin, çoğu devrenin gereksinimlerini karşılayabilecek az miktarda statik güç tüketimini artırarak genel performansı iyileştirdiği görülebilir.

3 sonuç

Geleneksel iki aşamalı operasyonel amplifikatöre dayanan bu makale, düşük voltajlı yüksek performanslı CMOS işlemsel amplifikatörün yeni bir çerçevesini gerçekleştirmek için kazanç önyükleme, ileri besleme telafisi ve diğer teknolojileri birleştirir. Düşük güç tüketimi koşulları altında, yerleşim simülasyon doğrulaması, yüksek DC kazancı ve yüksek bant genişliği elde edebilir ve sistem, kararlılık açısından iyi bir performansa sahiptir. Bu devre, bant aralığı referans kaynaklarında ve toplayıcılar, karşılaştırıcılar, vb. Gibi çeşitli aritmetik devrelerde kullanılabilir ve çok geniş bir uygulama alanına sahiptir.

Referanslar

[1] He Lenian, Wang Yi. Analog Tümleşik Devrelerin Tasarımı ve Simülasyonu M Pekin: Science Press, 2008.

2 WANG R T, HARJANNI R.Düşük güçlü CMOS OTA'ların kazanç artırımı için kısmi pozitif geri besleme J. Analog Tümleşik Devreler ve Sinyal İşleme, 1995 (8): 21-35.

[3] THANDRI B K, SILVA MARTNEZ J. Daha değirmen kapasitörleri bulunmayan çok aşamalı operasyonel transkondüktans amplifikatörleri için sağlam bir ileri besleme kompanzasyon şeması J. IEEE Journal of Solid-State Circuits, 2003, 38 (2): 237-243.

4 CHANG Y S, WU H C, SHIAU M S, ve diğerleri, Ortak mod ileri beslemeyi ve HD3 ileri beslemeyi kullanan sözde diferansiyel işlemsel iletim iletkeni amplifikatörü J. International Symposium on Integrated Circuits, 2011,10 (11): 250-253.

5 AKBARI M, BIABANIFARD S, ASADI S. DC kazanımı ve geçiş iletkenliği artırılmış geri dönüşüm katlanmış kas kodunun tasarımı ve analizi OTA J .AEU International Journal of Electronics and Communications, 2014, 68 (11): 1047-1052.

-

- Yeni film incelemesi: "Psychological Sin" oyuncuları en güçlü oyunculuk becerilerine katkıda bulundu