Geliştirilmiş FPGA tabanlı (2, 1, 4) Viterbi kod çözücü

Hata düzeltici kod teknolojisi, dijital iletişimde önemli bir rol oynar Evrişimli kodun kodlama yöntemi, mükemmel hata düzeltme performansı nedeniyle yaygın olarak kullanılmaktadır Viterbi kod çözme yöntemi, evrişimli kodlar için optimal bir olasılık kod çözme yöntemidir. Evrişimli kodların geniş uygulaması önemli bir değere sahiptir. Son yıllarda, yarı özel bir devre olarak FPGA, dijital sinyal işleme sistemlerinde yaygın olarak kullanılmakta ve Viterbi kod çözücülerin gerçekleştirilmesi için uygun koşullar sağlamaktadır.

Viterbi kod çözücülerin performansını değerlendirmek için ana göstergeler kod çözme hızı ve kaynak tüketimidir, bu nedenle kod çözme gecikmesinin nasıl azaltılacağı, kod çözme hızının nasıl artırılacağı ve kaynak tüketiminin nasıl azaltılacağı son yıllarda gündemdeki konular haline gelmiştir. Literatür, kod çözme gecikmesini azaltmak ve kod çözme oranını arttırmak için literatür ızgara grafiğinin yapısını geliştirir Literatür, iki temel algoritmayı kullanır ve literatür, dört temel algoritmayı kullanır. Temel iki algoritma daha az kaynak tüketir, ancak temel iki algoritmanın veri işleme kapasitesi, dört temel algoritmanınkinden daha zayıftır; temel dört algoritma, temel iki algoritmadan daha güçlü bir veri işleme kapasitesine sahiptir, ancak temel dört algoritmanın temel frekansı düşüktür ve hızın iyileştirilmesi zordur. Literatür, Viterbi'nin yinelemeli yöntemini geliştirerek kod çözme hızını artırır, ancak bu yöntem karmaşıktır ve çok fazla kaynak tüketir. Literatür, kod çözme gecikmesini azaltmak ve kod çözme oranını arttırmak için geri izleme yapısını geliştirir Literatüre dayanarak, kayan pencere boru hattına dayalı bir ileri geri izleme tabanı dört algoritması önerilmiştir, ancak bu yöntem, çok fazla kaynak tüketen fazlalık kayan pencereler ekler. Sınırlı kaynaklara sahip senaryolar için uygun değildir.

Viterbi kod çözme algoritmasının XC6SLX16-2CSG-324 FPGA'da uygulanmasını sağlamak için ve mevcut geliştirilmiş algoritmaların çoğunun, sınırlı kaynaklar koşulu altında gecikmeyi ve kaynak tüketimini dengelemesinin zor olduğu gerçeği göz önüne alındığında, bu makale iki temel algoritmaya dayalı bir yöntem önermektedir. algoritmayı geliştirin. Temel iki algoritmaya dayalı olarak, bu algoritma, temel iki algoritmanın veri işleme kapasitesini geliştirmek için Viterbi kod çözücünün metrik kontrolünü ve hayatta kalan yol bilgisi depolama modüllerini geliştirir Sınırlı kaynakların koşulu altında, kod çözücüyü etkili bir şekilde basitleştirebilir. Uygulama yapısı, ardından gecikmeyi ve kaynak tüketimini hesaba katar ve kod çözme performansını geliştirir.

1 Geliştirilmiş Viterbi algoritması

1.1 Algoritma prensibi

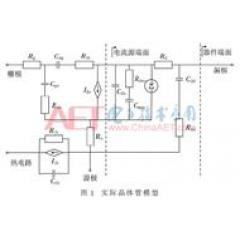

Viterbi algoritması, sonlu durum ayrık zamanlı Markov zincirinin durum tahmin problemini çözmek için kullanılan bir optimizasyon algoritmasıdır. Şekil 1'de gösterilen taban iki kafes diyagramı, evrişimli kodun kod çözme sürecini gösterir ve spesifik açıklama literatürde bulunabilir. Zaman düğümü t, t'inci bilgi sembolünü temsil eder ve Viterbi kod çözücüsü, kafesten maksimum olasılık yolunu bulur.

Viterbi kod çözücünün iş akışı Şekil 2'de gösterilmektedir. Alıcının her an kanaldan aldığı bilgi dizisini kodlama ızgarasındaki tüm bilgi dizileri ile karşılaştırın, her dalın yol metrik değerini yumuşak karar prensibine göre hesaplayın ve bir sonraki anda duruma giren dalın metrik değeri ile biriktirin , Her duruma giren en küçük metrik değere sahip dal yolu ve hayatta kalma yolu bilgilerini korumak için Geri izleme derinliğine ulaşıldığında, en küçük metrik değere sahip durum, ters geri izlemeyi başlatmak için başlangıç durumu olarak seçilir ve hayatta kalma yolu bilgilerine göre geri izleme olasılığının maksimum yolu bulunur .

Not (n0, k0, m) evrişimli kod kodlayıcıdır, kodlayıcı toplam 2k0 × m durumlara sahiptir, Viterbi kod çözücü aynı 2k0 × m durum üretecine sahip olmalıdır ve her durum bir depolama yoluna sahip olmalıdır Metrik değerin hafızası ve hayatta kalma yolu bilgisinin hafızası, dolayısıyla Viterbi kod çözücünün karmaşıklığı 2k0 × m ile üssel olarak artar.

1.2 Algoritma iyileştirmesinin ayrıntılı açıklaması

Temel iki Viterbi kod çözücü temelde dal ölçüsü hesaplama birimi (BMU), toplama karşılaştırma birimi (ACSU), yol metrik depolama birimi (PMU), hayatta kalma yolu depolama birimi (SMU) ve geri izleme biriminden (TBU) oluşur. Sistem blok diyagramı aşağıdaki gibidir. Şekil 3'te gösterilmiştir.

Temel iki algoritmaya dayalı olarak, geliştirilmiş algoritma esas olarak ACSU'daki metrik kontrol yapısını ve SMU'nun depolama yapısını iyileştirir. Si durumu i, PMi Si durumunun yol metriğinin kümülatif değeri olsun, geri izleme derinliğidir ( = L + m, L bilgi sembollerinin sayısıdır) ve Alt_bit hayatta kalma yolu bilgisidir. Algoritma geliştirmesinin spesifik açıklaması aşağıdaki gibidir:

2 Teorik analiz

2.1 Ayrık belleksiz kanal (DMC) modeli

Viterbi kod çözme algoritmasının performansı, kod çözücü tarafından çıkan bit hata oranı ile analiz edilebilir. Geliştirilmiş algoritma yumuşak kararı benimsediğinden, burada esas olarak Gauss beyaz gürültüsü (AWGN) için, BPSK modülasyonunun DMC kanal modeli farklı geri izleme derinliği , = (5 10) m'ye göre analiz edilir. DMC kanal modeli Şekil 5'te gösterilmektedir. Q, seviye niceleme dizisidir.Sol taraf, kanal girişini ikili 0, 1 olarak temsil eder, sağ taraf kanal çıkışını 0 (q-1) olarak temsil eder ve p (q-1 | 0) girişi şu şekilde temsil eder: 0, çıktının q-1 olma olasılığıdır.

Kanal kodlama teoremine göre, ikili simetrik kanal (BSC) altında, belirli bir (n0, k0, m) evrişim kodu için, Viterbi kod çözücüsü tarafından maksimum olasılık kod çözme kullanılarak oluşturulan bir hata olayının olasılığı PE:

2.2 Geliştirilmiş algoritma analizi

Bir (2,1,4) evrişimli kod verildiğinde, Viterbi'nin kesilmiş kod çözücüsü için, geri izleme derinliği , = (5-10) m'yi karşılamalıdır. Metrik kayıt kaynaklarını korumak için, bu makale = 20'yi seçer. Ardından, Şekil 6'da gösterildiği gibi = 20 olduğunda Q değerini değiştirin. Q'nun < Saat 8'de karar kazancı, Q > 8'den sonra yargı kazancı çok yavaş artar. Bu nedenle, pratik uygulamalarda genellikle sekiz seviyeli ve on altı seviyeli niceleme kullanılır, Kod çözücü çok karmaşık değildir ve 2 ila 3 dB yumuşak karar kazancına sahiptir. Bu nedenle, = 20 ve Q = 8'in seçilmesi, kod çözücünün performansını etkin bir şekilde garanti edebilir.

3 Simülasyon analizi

3.1 MATLAB simülasyon sonuç analizi

MATLAB'de, Viterbi kod çözücü AWGN kanalında ve düz Rayleigh sönümleme kanalında modellenir. = 20, Q = 8 olduğunda, bir (2, 1, 4) evrişimli kod verildiğinde, doğru Geleneksel ve geliştirilmiş kod çözücüler sırasıyla AWGN kanalında ve düz Rayleigh sönümleme kanalında simüle edilir. Bu modelde, giriş kanalının sinyali, ikili faz kayması anahtarlaması (İkili Faz Kaydırma Anahtarlaması, BPSK) modüle edilmiş bir sinyaldir ve kanalın çıkışı sekizlik olarak nicelendirilir. Bit Hata Oranının (BER) istatistiksel performansı Şekil 7'de gösterilmektedir. BER performansı açısından bakıldığında, bu makalede AWGN kanallarında kullanılan Viterbi algoritması, geleneksel Viterbi algoritmasına göre yaklaşık 0,5 dB kazanç sağlamıştır; düz Rayleigh fading kanallarında bu makalede kullanılan Viterbi algoritmasının performansı geleneksel Viterbi algoritması ile karşılaştırılmıştır. , Sinyal-gürültü oranı düşük olduğunda kazanç artışı belirgin değildir ve sinyal-gürültü oranı yüksek olduğunda kazanç yaklaşık 1 dB artar.

3.2 İMKB simülasyon sonuçlarının analizi

= 20 ve Q = 8 ile (2, 1, 4) kod çözücüyü hedefleyen bu makale, Verilog donanım tanımlama diline dayalı olarak RTL seviyesindeki her modülü açıklar ve işlevsel simülasyon için ISE Design Suite 14.7'yi kullanır.

İyileştirmeden önce ve sonra Viterbi dekodere ISE simülasyonu, kaynak tüketimi ve gecikme süresi Tablo 1'de gösterilmektedir. Tablodan, bu yazıda önerilen metrik kontrol yöntemini ve hayatta kalan yol depolama yapısını kullanan Viterbi kod çözücünün, geleneksel metrik kontrol ve RE kullanarak yalnızca 15 CLK gecikmesi ile geri izleme derinliğine ulaştıktan sonra ilk sembolü çözebildiği görülebilir. Hayatta kalma yolu depolama yapısının Viterbi kod çözücüsü, 32 CLK gecikmesi gerektirir. İyileştirilmiş kod çözücünün hızı büyük ölçüde iyileştirildi ve kaynak tüketimi de bir dereceye kadar tasarruf edildi.

Viterbi kod çözücünün testi temel olarak iki bölümden oluşur: işlevsel doğrulama ve kod çözücünün hata düzeltme performansı.

Önce işlevsel doğrulamayı gerçekleştirin, tüm veriler idealdir. = 20 olduğundan, kod çözücü, kod çözme için bir grup olarak 20 veriyi kullanır.Bu makaledeki Viterbi kod çözücü, kesilmiş kod çözme kullanır, bu nedenle, bir bilgi grubu oluşturmak için 16 rastgele dizi artı 40s üretmek için MATLAB kullanır. sekansı, C1: 11111101101110110000, kodlayıcı C2 çıkış dizisi boyunca: 11_10_11_01_10_10_01_11_11_11_00_11_00_10_11_11_11_11_01_11, sekiz seviyeli kuantizasyon C3 sekansı 111111_111000_111111_000111_111000_111000_000111_111111_111111_111111_000000_111111_000000_111000_111111_111111_111111_111111_000111_111111, giriş Viterbi kod gibi C3 sekansı ISE simülasyon sonuçları Şekil l'de gösterilen.

Şekilde, Clk sembol saati, kod C3 dizisidir, TB_flag, geri izleme derinliğine ulaşıldığını belirtmek için 1'dir ve kod çözülmüş çıktı sonucudur: 11111101101110110000, C1 dizisi ile tam olarak aynıdır, böylece kod çözücü doğru çalışır.

İkincisi, yanlış girişim bilgilerinin yapay olarak ideal verilere eklendiği hata düzeltme performans testidir. Hesaplamadan sonra, (2, 1, 4) kod çözücünün df'si 7'dir, bu nedenle teorik olarak bu kod çözücü ardışık 5 kod çözmede 3 rastgele hatayı düzeltebilir. Testten sonra, 20 ardışık sembol bölümüne rastgele 3 hata sembolü ekleyerek, yani bit hata oranı% 2.5 olduğunda, kod çözücü hatayı tamamen düzeltebilir. 20 ardışık sembol segmentine 4 rastgele hata sembolü eklenir, yani bit hata oranı% 3,33 olduğunda hata tamamen düzeltilemez, ancak hata sembolleri arasındaki aralık 5 sembol ise tamamen düzeltilebilir. Teorik değerin hata düzeltme performansı, kod çözme derinliği sonsuz olduğunda hesaplanır ve sonsuz kod çözme derinliği donanımda gerçekleştirilemez, bu nedenle pratik uygulamalardaki hata düzeltme performansı teorik değerle belirli bir boşluğa sahip olacaktır. Bununla birlikte, gerçek iletişim sisteminde, modülasyondan sonra kanaldan iletilen hata kodu oranı 10-2 mertebesinden uzaktır. Şekil 7'de gösterildiği gibi, AWGN kanalında, sinyal-gürültü oranı 4,5 dB'den büyük olduğu sürece, bit hata oranı 10-2'den daha azdır; düz Rayleigh sönümleme kanalında, sinyal-gürültü oranı 14 dB'den büyük olduğu sürece, bit hata oranı şöyledir: Bu büyüklük derecesinin 10-2'den azı ve gerçek iletişim sistemindeki kanalın sinyal-gürültü oranı 14 dB'den çok daha büyüktür, bu nedenle bu makaledeki geliştirilmiş Viterbi kod çözücü pratik uygulamaların ihtiyaçlarını karşılayabilir.

4. Sonuç

Bu tasarım esas olarak ACS ve SMU birimlerini hedefler, kod çözücünün yapısını basitleştirir, donanım uygulamasının karmaşıklığını azaltır ve hesaplama hızını artırır. Ek karşılaştırma biriminin kontrol ölçüsü bölümünde, yol ölçüsü veri taşması sorununu çözmek için, bu makale, hesaplama miktarını azaltan ve kod çözme hızını geliştiren önceden tanımlanmış bir depolama ölçüsü değeri yazmaç kapasitesi yöntemi önerir. Hayatta kalma yolunun depolama bölümünde, depolama yöntemi optimize edilir ve kod çözücünün güç tüketimini azaltmak için adım adım depolama yöntemi benimsenir. Geri izleme kod çözme yapılırken, RAM'in depolama alanını azaltan, kalan durumun paritesine göre çıktıyı tamamlamak için eşlik geri izleme kod çözme yöntemi benimsenir. Simülasyon sonuçları, bu makaledeki optimize edilmiş tasarımın donanım devresinin yapısını büyük ölçüde basitleştirebileceğini ve kod çözücünün tasarımında uygulama değerine sahip olduğunu göstermektedir.

Referanslar

Wang Xinmei, Xiao Guozhen Hata düzeltme kodları - ilkeler ve yöntemler (gözden geçirilmiş baskı) Xi'an: Xidian University Press, 2001.

GAO Z, ZHU J, HAN R, vd.SRAM tabanlı FPGA'larda yapılandırma belleği SEU-Tolerant Viterbi kod çözücülerinin tasarımı ve uygulaması. Nanoteknoloji üzerine IEEE İşlemleri, 2019, 18: 691-699.

Zhang Shen. Evrişimli Kod Kodlayıcı ve Viterbi Kod Çözücünün Tasarımı Chengdu: Çin Elektronik Bilim ve Teknoloji Üniversitesi, 2008.

Ping Lei. 5G iletişimi için kuyruk ısıran evrişimli kodlar ve turbo kodlar üzerine araştırma Xi'an: Xidian Üniversitesi, 2017.

MAMARDE R, KHOJE S. Viterbi kod çözücü, Zynq-7000 AP-SoC. 2018 İkinci Uluslararası Akıllı Hesaplama ve Kontrol Sistemleri Konferansı (ICICCS) .IEEE, 2018: 941-944.

EL-GOHARY A, SAAD M, MAHMOUD O, et al. IEEE 802.11 n standardına dayalı OFDM alıcı-vericinin düşük kullanımlı FPGA uygulaması. 20198. Uluslararası Modern Devreler ve Sistem Teknolojileri Konferansı (MOCAST). IEEE, 2019: 1-4.

ZHOU L, TANG M, LIU D, vd.Yazılım tanımlı radyo için esnek bir viterbi kod çözücü. Journal of Theoretical and Applied Information Technology, 2013, 47 (2): 702-706.

SANTHI M, LAKSHMINARAYANAN G, SUNDARAM R, ve diğerleri FPGA.2009 Uluslararası SoC Tasarım Konferansı'nda (ISOCC) senkronize boru hatlı iki aşamalı radix-4200Mbps MB-OFDM UWB Viterbi kod çözücü. IEEE, 2009: 468-471.

Zhu Mingzhe, Xiao Rui, Su Xiaofan ve diğerleri.Karışık gürültü altında Viterbi senkron sıkıştırması S dönüşümüne dayalı FM sinyal analizi. Journal of Electronics and Information, 2018, 40 (12): 2913-2918.

YOSHIKAWA H. K-best viterbi kod çözme algoritmasının hata performans analizi. 2018 Uluslararası Bilgi Teorisi ve Uygulamaları Sempozyumu (ISITA) .IEEE, 2018: 257-260.

AHMED S, SIDDIQUE F, WAQAS M, ve diğerleri.Farklı kısıtlama uzunlukları için Viterbi algoritması performans analizi. 201916. Uluslararası Bhurban Uygulamalı Bilimler ve Teknoloji Konferansı (IBCAST). IEEE, 2019: 930-932.

Yang Min.Yüksek oranlı ve düşük gecikmeli Viterbi kod çözücünün tasarımı ve uygulaması.Elektronik Teknoloji Uygulaması, 2018, 44 (9): 56-58, 62.

Xin Yuanbo, Hou Hong. FPGA'ya Dayalı Dijital Kanallı Alıcının Araştırma ve Uygulaması. Elektronik Teknoloji Uygulaması, 2009, 35 (5): 163-165, 170.

Qiu Peiliang, Chen Huifang, Xie Lei. Temel Dijital İletişim. Beijing: Electronics Industry Press, 2007.

yazar bilgileri:

Wu Xueling, Jiang Hong

(Bilgi Mühendisliği Okulu, Güneybatı Bilim ve Teknoloji Üniversitesi, Mianyang, Sichuan 621000)

-

- Çok düşük bırakma voltaj regülatörünün çıkış akımını artırın ve eşit ısı dağılımının paralel tasarımını gerçekleştirin

-

- Deng Chao'nun Fang Sijin'in tarzı için kredisi mi? Sun Li'nin "An Jia" nın perde arkasındaki kişiler hakkındaki konuşmasını dinleyin ...