FPGA ve NAND Flash'a Dayalı Taşınabilir Sinyal Toplama Sisteminin Tasarımı

0 Önsöz

Modern algılama teknolojisinin ve teknolojik seviyenin hızlı gelişimi ile, sinyal toplama teknolojisinin uygulama yelpazesi genişliyor ve genişliyor. Aynı zamanda, sinyal edinim sisteminin edinim doğruluğu, örnekleme hızı ve taşınabilirliğinin tasarım gereksinimleri için daha yüksek gereksinimler ortaya konmuştur. Alan programlanabilir kapı dizisi (FPGA), yeterli mantık kapısı, yüksek saat frekansı, hızlı hız, yüksek verimlilik ve zengin IP çekirdeklerinin özelliklerine sahiptir, bu da onu yüksek hızlı sinyal toplama sistemi tasarımı için etkili bir araç haline getirir. Mevcut sinyal edinim sisteminin tasarım gereksinimlerini hedefleyen bu makale, temel olarak örnekleme hızının ve sinyal edinim sisteminin taşınabilirliğinin nasıl geliştirileceğini açıklamaktadır.

Şu anda, taşınabilir sinyal edinim sisteminin düşük örnekleme hızı, esas olarak yetersiz iletim hızı ve sinyal edinim sisteminin işleme hızı ile sınırlıdır. Son yıllarda ilgili literatüre bakın, FPGA tabanlı sinyal toplama sistemi esas olarak aşağıdaki iki tasarım şemasına sahiptir: Şema 1, mantık kontrol modülü olarak FPGA'yı kullanarak, ADC edinme modülü ve USB2.0 iletim modülü ile; Şema 2, FPGA'yı aynı şekilde kullanıyor ADC modülü tarafından toplanan verileri önbelleğe almak için DDR2 / DDR3 modülüne sahip mantık kontrol modülü. İlk çözüm, USB iletim hızı ile sınırlıdır ve örnekleme hızı nispeten düşüktür; ikinci çözüm daha yüksek bir örnekleme hızı elde edebilmesine rağmen, uçucu veri, küçük depolama kapasitesi ve yetersiz taşınabilirlik sorunlarına sahiptir.

Yukarıdaki sorunlara yanıt olarak, bu makale mevcut NAND Flash yüksek hızlı depolamanın özelliklerini birleştirmekte ve taşınabilir bir yüksek hızlı sinyal toplama sistemi tasarımı önermektedir. Bu tasarımın anahtarı, hızlı yazmak için bellek yongasının özelliklerinden yararlanmaktır ve veri yolu, ADC tarafından toplanan sinyaller DMA tarafından bellek yongasında saklanacak şekilde yeniden kullanılabilir. İkinci olarak, tasarım, ana bilgisayarın konfigürasyonunu azaltan sinyallerin sahada görüntülenmesi için bir LCD ekran ile donatılmıştır. Sistem, uzun vadeli, çok partili sinyal alımını karşılar.

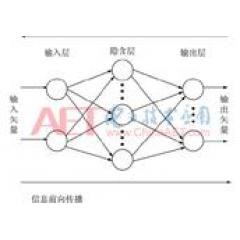

İşlev ve prensibe göre, sistem 4 modüle ayrılmıştır: Şekilde gösterildiği gibi FPGA yongasına dayalı mantık kontrol modülü, ADC yongasına dayalı veri dönüştürme modülü, NAND_Flash yongasına dayalı yüksek hızlı veri depolama modülü ve LCD dokunmatik ekran modülü 1 gösterilmektedir.

Sistemin temel çalışma prensibi: İlk olarak analogdan dijitale dönüştürme modülü, analog sinyali aldıktan sonra, sinyali dijital sinyale dönüştürür ve FPGA mantık kontrol modülündeki FIFO'ya gönderir; ikincisi, FPGA mantık kontrol modülü Doğrudan Bellek Erişimini kullanır , DMA) modu, verileri FIFO'dan NAND_Flash veri depolama modülüne aktarır; daha sonra, NAND_Flash modülü, yüksek hızlı verileri senkronize bir şekilde depolamak için karşılık gelen dahili yapısını birleştirir; son olarak, LCD modülü ilgili talimatları belirli bir hızda okumak için gönderir Veriler, FPGA aracılığıyla belirli sinyal işlemeye tabi tutulur ve LCD ekranda görüntülenir.

2 donanım devre tasarımı

2.1 FPGA mantık kontrol modülü

FPGA mantık kontrol modülü, EP4CE40F29C8N, ALTERA Company'nin EPCS64SI16 ve Hynix'in H27U1G8F2B'sinden oluşur. Bunların arasında EP4CE40F29C8N, Cyclone IV serisi FPGA yongasıdır.Çipin maksimum saat frekansı 472 MHz ve sistem tasarımının gerektirdiği maksimum saat frekansı ve çevresel bağlantı arabirimlerini karşılamak için 533 IO arabirimine sahiptir. Mantık kontrol modülü, üst seviye tasarım kısmı, sistem saati ve sıfırlama kısmı, edinim kontrol kısmı, depolama kontrol kısmı, LCD ekran kontrol kısmı ve NISO II kısmından oluşur.Üst seviye tasarım kısmı, her bir parçanın bağlanmasından ve mantık kontrol modülü ile diğer modüller arasındaki arayüzden sorumludur. . FPGA'nın üst seviye şematik diyagramı Şekil 2'de gösterildiği gibidir.

Sistem saati ve sıfırlama bölümünde, FPGA yonga sistemi saat arabirimi 25 MHz'lik bir pasif kristal osilatör bağlayarak 25 MHz saat sinyali elde eder ve 25 MHz saat sinyalini "PLL" IP çekirdeği üzerinden 33 MHz, 50 MHz, 100 MHz ve 200 ile çarpar. MHz, sistemin saat devresi olarak. İkinci olarak, eşzamansız olarak sıfırlanan ve eşzamanlı olarak serbest bırakılan bir sistem sıfırlama sinyali oluşturun.

LCD ekran kontrol kısmı, bir dalga formu modülü, bir veri tampon modülü, bir LCD ekran sürücü modülü ve bir dokunmatik ekran komut alma modülünden oluşur. Bu bölüm, QSYS'deki görüntü verilerini DDR2 önbellek modülüne göndermek için bir arayüz sağlar ve görüntü verilerinin çıkışını gerçekleştirmek için DDR2 yongası ve LCD ekran yongası için bir DMA iletişim mekanizması kurar.

NIOS II çip üzerinde gömülü işleme sistemi, sinyal toplama sistemi komut alımı ve program yürütme kontrolünden sorumlu QSYS sistemiyle entegre geliştirme aracı tarafından oluşturulur. NIOS II sistemi aşağıdaki görevleri tamamlar: (1) Sistem başlatma programı yürütülür ve LCD komut girişi izlenir; (2) Yapılandırma Flash yongasının (H27U1G8F2B) okuma ve yazma işlemleri gerçekleştirilir ve ekran modülündeki arka plan görüntüsü, yazı tipi kitaplığı ve yazı tipi kitaplığı yapılandırma Flash yongasında saklanır. Toplama işlemi sırasında, toplama veri depolamasının başlangıç ve bitiş konumu bilgileri toplama işlemi sırasında; (3) Toplama verileri okuma işlemini gerçekleştirin ve toplanan sinyal verilerini dalga formu görüntüleme verilerine dönüştürün; (4) Sistemin çevresel sürücü talimatlarının çıkışından sorumludur .

2.2 Analogdan dijitale dönüştürme modülü

Analogdan dijitale dönüştürme devresi, dönüşüm yongası olarak AD9226'yı kullanır.Bu yonga, maksimum 65 MSPS dönüştürme oranı ve iyi sinyal-gürültüye sahip, düşük güçlü (475 mW), yüksek hassasiyetli (12 bit) yüksek hızlı analogdan dijitale dönüştürme yongasıdır. Oran (70 dB). Bu tasarımda, sinyal giriş aralığı 1 V ila 3 V arasındadır. Bu modülün örnekleme saati FPGA mantık modülü tarafından sağlanmıştır, örnekleme hızının kontrolüne ulaşmak için bu metindeki tüm test içeriğindeki örnekleme hızı 50 MHz olup, analog-sayısal dönüşüm modülünün devre şeması Şekil 3'teki gibi gösterilmiştir.

2.3 Yüksek hızlı veri depolama modülü

Yüksek hızlı örnekleme oranını eşleştirmek için, yüksek hızlı veri depolama modülü, SLC parçacıklarının NAND Flash yongalarını seçer. Bu tasarımda Micron'un MT29F256G08AUCABH3 yongası seçilmiştir.Senkronize durumda bu yonganın pin okuma ve yazma hızı 200 MT / sn'ye ulaşabilir ve DDR modu veri yazma sürecinde yani saatin hem yükselen hem de düşen kenarlarında kullanılır. Veriler yazılır. Veri kılavuzunun analizi sayesinde, NAND Flash'ın PROGRAM SAYFASI işlemine devam etmesi gerektiğinden, bu yonga 1 sayfa veri (8 KB) yazar Yaklaşık 400 s sürer. Bu süre boyunca, AD sinyal toplama modülü, NAND Flash'ta depolanan verilerden çok daha büyük olan ve sistemin tasarım gereksinimlerini karşılayamayan verileri 4 × 104B toplar. Senkronize yazma işlemi sırasında NAND Flash yongasının 8 KB veri yüklemesinin 40,96 s sürdüğü düşünüldüğünde, analogdan dijitale dönüştürme modülünün 8 KB veri toplaması 81,92 s alır. Sistem depolama süresini etkileyen ana faktör, NAND Flash programlama süresidir (350 s).

Bu sorunu hedefleyen bu tasarım, Şekil 4'te gösterildiği gibi MT29F256G08AUCABH3'ün depolama yapısı özelliklerini birleştirir. Çipin içinde 8 LUN yapısı vardır ve bir LUN programlama durumundayken diğer LUN'lar okunabilir, yazılabilir ve programlanabilir. Bu özelliğe göre, bu tasarım dahili 8 LUN yongasını bir boru hattı şeklinde düzenler ve Şekil 5'te gösterildiği gibi veri depolama işlemlerini sırayla gerçekleştirir. Toplanan veriler 8 KB'ye ulaştığında, yazmaya hazır durumdaki LUN, DDR modunda veri yazmaya başlar. 1 sayfa veriyi (8 KB) yazdıktan sonra, sonraki LUN yazmaya hazır durumuna girer ve depolanmamış verilerin tekrar 8 KB'ye ulaşmasını bekler. Bu şekilde döngüleme, sekizinci LUN yazma işlemini tamamladığında, ilk LUN programlama işlemini tamamlar ve yazma işlemleri için boşta durumdadır Şekil 5, depolama yongası boru hattı çalışma modunu gösterir.

2.4 Ekran modülü

Sistemin ekran modülünde 800 × 480 çözünürlüklü 7 inç LCD likit kristal ekran ve dijital arayüz sürücüsü seçilmiştir. Görüntü ekranının çıktı renk sinyali, görüntü verilerini arabelleğe almak için 512 MB DDR2 SDRAM yongası ile 565 RGB paralel bağlantı noktalı dijital sinyal yoluyla iletilir. Sistem görüntüleme modülünün saat frekansı 33 MHz'dir.

Modül, görüntüleme işlevine ek olarak insan-bilgisayar etkileşimi işlevini de omuzlar. Dokunmatik ekranın özelliklerini kullanarak, tüm sistemin işletim kontrolünü tamamlayın, klavye modülünü azaltın ve işlemi kolaylaştırın. Bu tasarım, dirençli bir dokunmatik ekran kullanır; ekranın x ekseni ve y ekseninin her biri, dokunmatik ekrana özel AD çipine bağlı iki sinyal hattına sahiptir (bu tasarımda AW2083 çipi seçilir) ve dokunmatik ekrana her basıldığında, karşılık gelen x ekseni ve y ekseni Bir direnç değeri oluşturun. İki koordinat ekseninin pozitif ve negatif kutupları arasına bir referans voltaj uygulanır.Kordinat eksenlerinden birinin belirli bir konumuna dokunulduğunda, bu konum ile karşılık gelen koordinat ekseninin pozitif ve negatif kutupları arasındaki direnç, voltaj şeklinde geri beslenir. ADC'nin giriş terminali 12 bitlik AD niceleme değeri üretir AD çipi tarafından toplanan koordinat verileri gerçek koordinat değeriyle orantılıdır ve ilişki doğrusaldır. Şekil 6, y ekseni koordinat ölçümünün eşdeğer devre şemasını göstermektedir.

3 Sistem programı mantık tasarımı

Sistem açıldığında, sistem başlatma işlemlerini gerçekleştirir. FPGA, sistemin konfigürasyon bilgilerini NAND Flash yongasında okur ve yapılandırır. Görüntü modülünün başlatma arabirimini edinin ve çıktı ve görüntüleme gerçekleştirin ve aynı zamanda yapılandırma yongasından depolama modülünün bir sonraki saklama adresini alın. Sistem başlatıldıktan sonra, sistem bekleme durumuna girer ve LCD ekran modülünün komut girişini izler.

3.1 Sinyal edinme süreci

LCD modülündeki "Edinmeyi Başlat" düğmesine tıklayarak sinyal edinme programını tetikleyin. Mantık kontrol modülü, sinyal edinme başlatma talimatını izler ve sistem sinyal toplama sürecine girer.

Sinyal edinme süreci:

(1) Yüksek hızlı depolama modülü başlatılır ve depolama durumu, önceki toplu işin sona erdiği LUN'un sonraki LUN'u için etkinleştirilir.

(2) Mantık kontrol modülü, bir mod dönüştürme modülü etkinleştirme sinyali gönderir ve aynı zamanda analog-dijital dönüştürme modülüne 50 MHz saat sinyali girer.

(3) Analogdan dijitale dönüştürme modülü çalışmaya başlar, giriş analog sinyalini 50 MS / s dönüştürme oranında 12 bitlik bir dijital sinyale dönüştürür ve bunu mantık kontrol modülüne verir.

(4) Mantık kontrol modülü 12 biti aldıktan sonra, onu 4 bit sola kaydırır ve bir 16 bit oluşturmak ve bunu FIFO'ya kaydetmek için mevcut alım partisinin 4 bitlik ikili değerini ekler. FIFO, giriş sinyali 16 bit, frekans 50 MHz; çıkış sinyali 8 bit, çıkış sinyali frekansı 400 MHz; derinlik 4096 kelimedir.

(5) FIFO durumu "FULL" olduğunda, mantık kontrol modülü yüksek hızlı veri depolama modülüne bir yazma komutu gönderir ve FIFO'ya bir okuma komutu gönderir Sistem, FIFO'dan yüksek hızlı veri depolama modülüne DMA şeklinde veri göndermeye başlar.

(6) Sayfa verilerinin depolanması tamamlandığında, mantık kontrol modülü FIFO okuma etkinliğini kapatır. Yüksek hızlı veri depolama modülü, sonraki LUN'un depolama durumunu etkinleştirir ve (5) ila (6) arasındaki adımları tekrar eder. Sinyal edinme akış şeması Şekil 7'de gösterilmektedir.

3.2 Sinyal edinme durdurma işlemi

LCD ekran modülündeki "Örneklemeyi Durdur" düğmesi tetiklenir.Lojik kontrol modülü veri toplama sürecinde adım (6) 'nın yürütülmesini beklediğinde, yüksek hızlı veri depolama modülünü ve analogdan dijitale dönüştürme modülünü etkinleştirin ve mevcut alım parti numarasını ve ilgili verileri ayarlayın Kaydedilen başlangıç ve bitiş konumları, Flash yapılandırma bilgileri deposunda saklanır. Sistem bekleme durumuna girer, LCD ekran modülünün komut girişini izler ve LCD ekran modülü arabirimi başlatır.

3.3 Dalga formu görüntüleme işlemi

LCD dalga biçimi görüntüleme düğmesi tetiklendikten sonra, arabirim toplama toplu seçim arabirimine geçer ve dalga biçimi görüntüleme işlem işlemine girmek için tıklanarak karşılık gelen partinin dalga biçimi görüntüsü seçilir.

Dalga formu görüntüleme işlemi:

(1) Mantık kontrol modülü, karşılık gelen toplu veri toplamanın depolama başlangıç ve bitiş konumlarını Flash konfigürasyonundan okur.

(2) Yüksek hızlı depolama modülündeki adrese karşılık gelen verileri okuyun ve bunu dalga formu kontrol IP çekirdeğine yazın. Dalga formu kontrol modülü, LCD dalga formu pencere kontrolünü kontrol etmekten ve toplanan veri değerini çift portlu RAM'e kilitlemekten sorumludur ve ayrıca dalga formu noktası görüntüleme koordinat pozisyonunu ve dalga formu ekran saat frekansını çıkarmaktan sorumludur.

(3) Dalga formu kontrol modülündeki verileri LCD ekran modülündeki DDR2 yongasına girin.

(4) LCD ekranda, DDR2'deki verileri okuyun ve görüntüleyin.

(5) Karşılık gelen partinin tüm verileri okunduğunda, dalga formu görüntüleme işlemi sona erer.

3.4 Yüksek hızlı veri depolama kontrol süreci

Yüksek hızlı veri depolama kontrol programı, temel olarak veri toplama işlemine ve görüntü veri okuma sürecine bölünmüştür. Bu tasarımda, veri toplama işlemi 200 MHz çalışma frekansı ile eşzamanlı bir yazma yöntemi benimser; ekran veri okuma işlemi, 50 MHz çalışma frekansı ile bir asenkron okuma yöntemi benimser.

(1) Yüksek hızlı veri yazma işlemi: NAND Flash çipi eşzamanlı okuma ve yazma durumunu etkinleştirir; Lojik kontrol modülünden yazma sayfası adresini alır; Yazma işlemi komutunu NAND Flash'a gönderir; Yazma işlemi adresini NAND Flash'a yazar; NAND Flash bekler Veri yazma etkinleştirme; Mantık kontrol modülü tarafından gönderilen yazma etkinleştirmesini alın, verileri yazmaya başlayın; Veri bir sayfayla dolduğunda, LUN programlama durumuna girer ve aynı zamanda mantık kontrol modülünden sonraki LUN'un depolama adresini alır , adımlarını tekrarlayın.

(2) Yüksek hızlı veri okuma işlemi: NAND Flash çipi eşzamansız okuma ve yazma durumunu etkinleştirir; Mantık kontrol modülünden okuma sayfası adresini alır; Okuma işlemi komutunu NAND Flash çipine gönderir; Çok işlemli işlem adresini NAND Flash'a yazar; NAND Flash verilerini okuyun ve mantık kontrol modülüne gönderin; Bir veri sayfasını okuduktan sonra, adımlarını tekrarlayın.

4 Deneysel test

Test platformu bir ultrasonik iletim devresi, bir ultrasonik alıcı devre, bir ultrasonik sonda ve kaynaklı ince bir metal plakadan oluşur. Ultrasonik prob ince metal plakaya 2,5 MHz ultrasonik sinyal iletir. Ultrasonik sinyal kaynağa ulaştığında, sinyalin bir kısmı veya tamamı yansıtılarak bir yankı sinyali üretilir. Sinyal edinim sistemi, yankı sinyalini ultrasonik alıcı devre aracılığıyla toplar ve mantık kontrol modülü tarafından işlendikten sonra depolama modülüne yazar. Aynı zamanda işlenen veriler LCD ekranda görüntülenir. Şekil 8, sinyal algılama sisteminin çıkış dalga biçimini gösterir. İki dalga biçimini karşılaştırdığımızda, sistemin 50 MHz'lik bir örnekleme hızında iyi örnekleme yapabildiği bulunmuştur. Şekil 9 ve Şekil 10, sürekli çok partili sinyal alımını gerçekleştiren sürekli örnekleme veri dalga formu çıktısını gösterir.

5. Sonuç

Sistem, toplanan analog sinyalleri AD9226 yüksek hızlı analogdan dijitale dönüştürme modülü aracılığıyla dijital sinyallere dönüştürür, bunları FPGA aracılığıyla büyük kapasiteli NAND Flash'ta depolar ve dalga biçimini LCD ekranda görüntüler. Pratik uygulamalarda, sistem uzun vadeli çok partili yüksek hızlı sinyal alımını gerçekleştirebilir ve minyatürleştirme ve kolay taşınabilirlik özelliklerine sahiptir.

Referanslar

Zhang Xiaowei, Su Shujing.FpGA tabanlı yüksek hızlı ve yüksek hassasiyetli veri toplama sisteminin tasarımı.Enstrümantasyon Teknolojisi ve Sensörler, 2016 (1): 70-72.

BAO S, YAN H, CHI Q, et al., Endüstriyel sensörler için FPGA tabanlı yeniden yapılandırılabilir veri toplama sistemi. Endüstriyel Bilişimde IEEE İşlemleri, 2017, 13 (4): 1503-1512.

Yang Haigang, Sun Jiabin, Wang Wei FPGA cihaz tasarım teknolojisi geliştirmeye genel bakış Elektronik ve Bilgi Dergisi, 2010, 32 (3): 714-727.

XU Z, ZHU L, SHAN J F, ve diğerleri.Yeni bir yüksek hızlı veri toplama sistemi. Journal of Fusion Energy, 2015, 34 (3): 1-4.

Huang Yuanwang, Yan Jihong, Zhou Wei.FpGA tabanlı veri toplama ve test sistemi tasarımı Modern Radar, 2015, 37 (4): 73-76.

KHEDKAR A A, KHADE R H. Yüksek hızlı FPGA tabanlı veri toplama sistemi Mikroişlemciler ve Mikrosistemler, 2016, 49: 87-94.

Li Mao, Yang Lu, Zhang Yanhua. FPGA ve USB'ye dayalı çok kanallı ultrasonik test sistemi tasarımı. Enstrümantasyon Teknolojisi ve Sensörleri, 2017 (8): 82-84.

Meng Xiaodong. FPGA tabanlı DDR3 kontrolör tasarımı ve doğrulaması Changsha: Ulusal Savunma Teknolojisi Üniversitesi, 2012.

LIU D, WANG Y, QIN Z, vd. SLC NAND Flash bellek depolama sistemlerinde Flash çeviri katmanları için alanı yeniden kullanma stratejisi.Çok Büyük Ölçekli Entegrasyon Sistemlerinde IEEE İşlemleri, 2012, 20 (6): 1094-1107.

Xiao Jia. NANDFLASH'a dayalı büyük veri yüksek hızlı depolama sisteminin tasarımı ve uygulaması Xi'an: Xidian Üniversitesi, 2014.

yazar bilgileri:

Zhou Hao, Wang Haoquan, Ren Shilei

(Bilgi ve İletişim Mühendisliği Okulu, Çin Kuzey Üniversitesi, Taiyuan, Shanxi 030051)

-

- Samsung, Hindistan için tasarlanmış 32 milyona kadar pikseli destekleyen Exynos 7904 çipini piyasaya sürdü

-

- Notre Dame Katedrali yangınından sonra Fransız lüks eşya devi 760 milyon yuan bağışladı ve Çin'deki Eski Yaz Sarayı'nın hayvan başını bedavaya iade etti.