Dinamik | AI çipinden hedef tespit tahtasına, "Xi'an Jiaotong University" DAC FPGA pistinde ikinciliği nasıl kazandı?

"

"XJTU-Tripler, Xi'an Jiaotong Üniversitesi Yapay Zeka ve Robotik Enstitüsü Ekibi" için tebrikler!

"

AI Technology Review Press: 5 Haziran 2019'da, en iyi elektronik otomasyon tasarım konferansı DAC 2019'un ev sahipliği yaptığı "Düşük Güçlü Hedef Tespit Sistemi Tasarım Yarışması" ABD'nin Las Vegas kentinde sona erdi. Xian Jiaotong Üniversitesi Yapay Zeka ve Robotik Enstitüsü'nden XJTU-Tripler ekibi, algoritmaların ve mimarinin özel optimizasyonuyla nihayet% 61,5 IoU doğruluk oranına ulaştı; enerji tüketimi 9537J, kare hızı 50,91 Hz, güç 9,248 W mükemmel sonuçlar, FPGA yarışmasını kazandı Taonun ikincisi ve aynı zamanda ülkede ilk üçe giren tek takım. Şu anda, rekabet ile ilgili araçları açık kaynak kodlamayı ve takip desteği sağlamayı planladılar. AI Technology Review, sağladıkları tasarım çözümlerini ve analizlerini aşağıdaki şekilde düzenler.

1

Rekabet geçmişi

ACM / IEEE Tasarım Otomasyon Konferansı'nın tam İngilizce adı olan DAC, elektronik tasarım otomasyonu ve gömülü sistemler alanındaki en önemli konferanstır. Sistem Tasarım Yarışması, DAC tarafından düzenlenmektedir ve küresel makine öğrenimi sistem tasarımcıları için teknik alışverişler için bir platform sağlamayı ve bu alandaki üstün çözümlere ve yeteneklere ulaşmayı amaçlamaktadır.

Yarışma sistemi, FPGA ve GPU olmak üzere iki donanım mimarisine ayrılmıştır ve yarışmalar ayrı ayrı yapılır. FPGA parkuru için, bu yarışma Xilinx, DJI ve NVIDIA tarafından desteklenmektedir.Yarışma ekibi tarafından drone perspektifi verilen eğitim veri seti (360x640 çözünürlükte 90.000 resim, tek hedefli açıklamalar) eğitilmektedir. Fangın kendi 50.000 test verisi setinde test edildi. Nihai tespit doğruluğu IoU (Intersection over Union)) yüksektir ve enerji tüketimi düşüktür.

2

Görev dağıtımı

Xi'an Jiaotong Üniversitesi Yapay Zeka ve Robotik Enstitüsü'nden Doçent Ren Pengju'nun bilişsel bilgi işlem mimarisi ekibi XJTU-Tripler. Bu yarışmada, donanım, düşük güçlü IoT ortamları için tasarlanmış Ultra96'yı kullandı - Xilinx ZYNQ geliştirme kurulu PS tarafı, rekabet tarafından sağlanan 1.5GHz ana frekansa sahip dört çekirdekli bir ARM Cortex-A53 CPU ile donatılmıştır. Yazılım açısından, Python tabanlı PYNQ çerçevesi geliştirme için kullanılır. Bunların arasında ekip üyeleri: Zhao Boran, Zhao Wenzhe, Xia Tian, Chen Fei, Fan Long, Zong Pengchen, algoritma optimizasyonundan Wei Yadong, Tu Zhijun, Zhao Zhixu, Dong Zhiwei sorumludur.

Algılama doğruluğu ile enerji tüketimi arasında bir denge sağlamak amacıyla, XJTU-Triper ekibi uç taraf için hafif bir sinir ağı çerçevesi seçti ve optimize etti; ZU3'ün kaynak kısıtlamaları göz önüne alındığında, ekip tarafından tasarlanan ve genel ağları destekleyebilen bir DNN hızlandırıcıyı kolaylaştırdı. (HiPU), ZU3'ün PL tarafında konuşlandırın. Bu nedenle, XJTU-Triper ekibinin ana çalışması, donanım platformu için algoritma optimizasyonu ve mimari tasarım optimizasyonu olarak ikiye ayrılmıştır:

Algoritma optimizasyonu

Özellik çıkarma için ana çerçeve olarak ShuffleNet V2'yi seçin;

Tek hedef konum regresyon çerçevesi olarak YOLO'yu seçin;

Sinir ağında 8 bit nicemleme gerçekleştirin.

HiPU optimizasyonu

CONV, FC, Dep-wise CONV, Pooling, Ele-wise Add / Mul gibi işlemleri destekleme, 268Gops'luk en yüksek bilgi işlem gücü ve% 80'den fazla verimlilik;

Ekstra zaman harcamadan Channel shuffle, divide ve concat işlemlerini destekleyin;

C, RISC-V montaj arayüzü API'si, esnek zamanlama sağlayın;

HiPU tamamen PL tarafında uygulanır ve PS tarafına dayanmaz. PS'nin ana iş yükü, görüntü ön işleme ve sonuç çıktısıdır.

3

Ayrıntılı ilgili teknolojiler

-

Tek hedef tespit ağı seçimi

Mobil terminalin gerçek zamanlı tespitini karşılamak için, XJTU-Triper ekibi nihayet YOLO'yu temel algılama çerçevesi olarak seçti ve ShuffleDet ağını özelleştirdi. Ve özellik çıkarma ağını, parametre ölçeği 1X'ten biraz daha büyük olan hafif bir ShuffleNet V2 ile değiştirin. Aşağıdaki şekil özelleştirilmiş bir tek hedef tespit ağını göstermektedir.

ShuffleDet ağ yapısı diyagramı

-

Sinir ağlarının eğitimi ve miktar tayini

XJTU-Tripler ekibi ilk olarak ImageNet veri setinde standart bir ShuffleNet V2 sınıflandırma ağını önceden eğitti. Model birleştikten sonra, özellik çıkarımının ilk üç katmanının parametreleri ShuffleDet ağına yeniden yüklenir. Tüm katman parametrelerini eğitmek için yarışma ekibinin eğitim setini kullanın.

FPGA'nın sabit nokta çalışmasına uyum sağlamak için, tüm parametre eğitimi tamamlandıktan sonra, tüm parametreler nicelleştirilir. Ekip, hem ağ parametrelerini hem de özellik haritasını 8 bit sabit noktalara ölçtü. Niceleme işlemi esas olarak aşağıdaki adımlara bölünmüştür: 1) BN katmanını parametrelere birleştirin; 2) birleştirilen parametreleri simetrik olarak niceleyin; 3) çevrimdışı niceleme tamamlandıktan sonra parametreleri ince ayarlayın. Aşağıdaki şekil, niceleme işleminin şematik bir diyagramıdır.

Ağ parametrelerinin kantifikasyon süreci

Nicemlemeden sonra, nihai hedef saptama ağı ShuffleDet, yaklaşık 1.94MB ağırlığa sahip yaklaşık 74 evrişimli katmana ve yaklaşık 78KB Bias'a sahiptir. Niceleme öncesi tam doğruluk doğruluk oranı% 67,1, nicelemeden sonraki doğruluk% 61,5 ve niceleme işleminin neden olduğu doğruluk kaybı% 5,6'dır.

-

HiPU hakkında

1) Genel bakış

Xian Jiaotong Üniversitesi Yapay Zeka ve Robotik Enstitüsü ekibi ağırlıklı olarak uygulamaya özel entegre devreler (AISC) için tasarladığından, FPGA'daki tasarım uygulaması esas olarak işlevsel doğrulama içindir. Bu nedenle, yarışma tarafından sağlanan bilgi işlem platformu için HiPU gerçekleştirmemiz gerekir. ZU3'ün kaynaklarına uyacak şekilde uygun terzilik. Aşağıdaki şekil, kesilmiş HiPU tasarımının blok şemasını ve özelliklerini göstermektedir. HiPU 233MHz'de çalışır ve en yüksek hesaplama gücü 268Gops'tur; C / RISC-V düzeneği programlama arayüzü olarak kullanılır ve evrişim verimliliği ortalama% 80'in üzerindedir.

HiPU'nun yapı blok şeması ve özellikleri

HiPU, CONV, FC, Dep-wise CONV, Pooling, Ele-wise Add / Mul ve diğer işlemler dahil olmak üzere çeşitli yaygın NN işlemlerini destekler. Bunların arasında FC,% 100'e yakın bir hesaplama verimliliği de elde edebilir.

HiPU, kanal yönünde karıştırma, bölme ve birleştirme işlemlerini destekler. Bu işlemler evrişim işlemini hemen takip ettiğinde, ek zaman harcamadan donanım üzerinde birleştirilebilirler.

HiPU, Zynq mimarisi tarafından kısıtlanmadan her türlü Xilinx FPGA üzerinde çalışabilir.

HiPU'nun alt katmanı matris işlemlerini, vektör işlemlerini ve skaler işlemleri uygular. İyi bir planlama ile her tür paralel hesaplama desteklenebilir. Gelecekte, verimli DeCONV işlemlerini desteklemek ve harita seyrek optimizasyonunu sağlamak için seyrek matris işlemlerinin optimizasyonu uygulanacaktır.

2) HiPU optimizasyon noktası analizi - gerekli DDR bant genişliğini katmanlar arası kademeli olarak azaltın

HiPU tasarım performansının iki önemli yönü vardır: biri MAC aritmetik biriminin kullanım oranıdır; diğeri, veri aktarım ağının MAC tarafından gerekli olan verilerle eşleşip eşleşemediğidir. Veri aktarım ağının sınırlamalarının çoğu DDR arayüzünden gelir. Bu tasarım, DDR arayüzü için özel olarak optimize edilmiştir.

HiPU'daki SRAM'ın boyut sınırlaması nedeniyle, bir özellik haritası katmanının verileri HiPU'nun SRAM'ına tam olarak yerleştirilemez. Normal hesaplama sırasının, her katmanın özellik haritası hesaplama sonuçlarını depolama için DDR'ye döndürmesi gerekir. Bu şekilde, her katmanın özellik haritası verisi bir DDR erişimine ihtiyaç duyar DDR için bant genişliği gereksinimi çok büyüktür ve ek güç tüketimi tüketilecektir.

Ekip, katmanlar arasında geçiş yaparak DDR bant genişliği gereksinimlerini azalttı. ShuffleNet darboğazını sınır belirleme olarak alarak, her darboğazın girişinden DDR'den bir özellik haritası satırı okuyun ve tüm katmanlar sırayla hesaplandıktan sonra, özellik haritasının çıktı satırı DDR'ye geri yazılır. Tüm satırlar sırayla hesaplanır. Aşağıdaki şekil, Modül C'nin kademeli hesaplama sırasını göstermektedir.

Modül-C, katmanlar arası kademeli hesaplama yöntemini benimser

3) İşlem verimliliğini artırmak için HiPU optimizasyon noktası analizi-girdi görüntü formatı dönüştürme

HiPU bir seferde paralel olarak 8 giriş kanalını hesaplar. Bununla birlikte, ağın ilk katmanının giriş görüntüsünde yalnızca 3 kanal RGB vardır, bu da HiPU'nun hesaplama verimliliğinin yalnızca 3/8 olmasına neden olur. Bu nedenle, ekibimiz giriş görüntüsü için bir dönüştürme modülü tasarladı. Conv1 çekirdeğinin genişliği 3 ise, giriş görüntüsünün kanalı 3'ten 9'a genişletilir. Son olarak, birinci katmanın işleme verimliliği 0.38'den 0.56'ya yükseltildi Dönüşüm diyagramı aşağıdaki şekilde gösterilmektedir.

Giriş görüntüsünün satır yönünde dönüştürülmesi

-

Sistem optimizasyon tasarımı ve analizi

1) Görüntü kod çözme ve evrişimli sinir ağı hesaplamalarının paralelleştirilmesi

HiPU, tasarım için yalnızca Zynq'in PL tarafı kaynaklarına dayandığından, PS tarafı kaynakları, sistem IO ile ilgili işler için serbest bırakılabilir. Ekibimiz, mevcut resmin algılama işlemini işlerken, işlemenin paralelliğini artırmak için PS tarafındaki sonraki resmi önceden okur ve kodunu çözer, böylece genel algılama kare hızını 30,3 Hz'den 50,9 Hz'e yükseltir.

Aşağıdaki şekil, görüntü kod çözme ve evrişimli sinir ağı paralelleştirmesinin şematik bir diyagramını göstermektedir.

(a) Paralelleştirme öncesi iş akışı

(b) Paralelleştirme sonrası iş akışı

Görüntü kod çözme ve evrişimli sinir ağı paralelleştirmesinin şematik diyagramı

2) PS tarafında orijinal Python kodunu hızlandırmak için C kodunu kullanın

PS tarafında zaman alan işlemi yeniden yapılandırmak için C kodunu kullanın ve Pynq çerçevesinde yeniden yapılandırılmış C kodunu çağırmak için ctypes arayüzünü kullanın: 1) PL tarafı verilerindeki güven ve bbox koordinatları için adres işaretçisini önceden hesaplayın; 2) En büyüğü bulun Güven ve karşılık gelen BBox'un koordinatları ve ardından mutlak koordinatları göreceli koordinatlara göre hesaplayın;

3) PL tarafında enerji tüketimini azaltmak için kapılı saat kullanın

Sistemin enerji tüketimini azaltmak için kapılı saat stratejisi tasarlanmıştır. HiPU bir resmi hesaplamayı bitirdiğinde, otomatik olarak saati kapatacak ve sonraki resim hesaplanmaya başladığında saati etkinleştirecektir. Bu strateji temel olarak aşağıdaki iki nedene dayanmaktadır:

Öncelikle sistemin jpg formatındaki resimleri çözme süresi sabit değildir.SD kart modeli sabit olmadığında ortalama değer 7ms-12ms arasındadır ve bazı resimler için maksimum değer 100ms'ye ulaşabilir;

İkincisi, sistemin güç tüketimi ölçüm süreci ve diğer ek ek yük, işlemci süresinin bir kısmını alacaktır ve PS ve PL, DDR bant genişliğini paylaşır, bu da 166Mhz'de HiPU kare hızının yaklaşık 50hz'ye ulaşmasıyla sonuçlanır, ancak HiPU 200Mhz'ye yükseltildiğinde sistem İşleme kare hızı yaklaşık 50 Hz'de kalır.

Yukarıdaki iki neden, HiPU işlem süresinin resim jpeg çözüm süresiyle eşleşmesine neden olur; HiPU işleme görüntü süresi görüntü çözüm süresinden daha kısa olduğunda, HiPU "boş çalışır" ve enerji harcar. Ek olarak, DDR bant genişliğini yakalama durumu için optimize etmeye devam etmek gerekir.

4

sonuç

Dünya çapında toplam 58 takım FPGA yarışma görevleri için kaydoldu ve 11 takım tasarım teslim etti (% 19 tamamlama oranı). Kazanan, UIUC, IBM ve Inspirit IoT tarafından ortaklaşa düzenlenen bir ekip olan iSmart3; ikinci ikincisi, Xian Jiaotong Üniversitesi Yapay Zeka ve Robotik Enstitüsü tarafından tasarlanan XJTU-Tripler; üçüncü ikinci ise ETH Zürih'ten bir ekip olan SystemsETHZ.

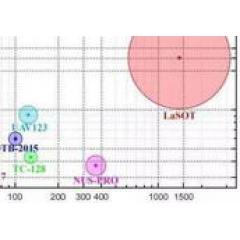

Bunların arasında XJTU-Tripler ekibi, tasarım için HLS yerine Verilog kullanan tek kazanan ekiptir. Yüksek performanslı DNN hızlandırıcısı nedeniyle, kullandığı sinir ağı aynı zamanda en büyüğüdür. Final yarışma sonuçları aşağıdaki gibidir:

DAC19 Sistem Tasarımı Yarışması Sıralaması

Kaynak karşılaştırması

Aynı ShuffleDet algoritması TX2 platformunda da kullanılmaktadır: Aşağıdaki tablo bu ikisinin analizi ve karşılaştırmasıdır. 8 bitlik nicemlemeden sonra IoU'da% 5,6'lık (% -8,3) mutlak bir kayba neden olduğu, ancak 28,87'lik (+% 131) bir kare hızında artış ve 8309J (% -46,56) enerji tüketiminde azalma sağladığı görülüyor.

TX2 ve Ultra96 FPGA platformlarında ShuffleDet performans karşılaştırması

DAC 2019 hakkında daha fazla bilgi için lütfen şu adresi ziyaret edin:

https://www.dac.com/content/2019-system-design-contest

2019 Küresel Yapay Zeka ve Robotik Zirvesi

12-14 Temmuz 2019 , Lei Feng.com ve Hong Kong Çin Üniversitesi (Shenzhen) tarafından ortaklaşa düzenlenen ve Shenzhen Yapay Zeka ve Robotik Enstitüsü tarafından ortaklaşa düzenlenen Çin Bilgisayar Federasyonu (CCF) sponsorluğunda 2019 Küresel Yapay Zeka ve Robotik Zirvesi (CCF-GAIR 2019 olarak kısaltılmıştır) Shenzhen'de resmen açılacak.

O sırada Nobel Ödülü sahibi James J. Heckman, Çinli ve yabancı akademisyenler, Dünya Zirvesi Başkanı, tanınmış Fellow ve çok sayıda ağır konuk savaşta yer alacak. Yapay zeka ve robotik bilim, üretim ve yatırım alanlarında karmaşık hayatta kalma durumunu tartışmak.

Tıklamak Orijinali okuyun , Kontrol edin: Makine öğrenimi yukarı akıştan gelen ayrımcı davranışları nasıl bastırır? Stanford AI Lab'ın en son sonuçları cevabı veriyor

-

- "Ailemdeki Çocuk" Dövüş Sanatları Xing Fei ile çıkıyor, eski kız arkadaşı Chen Xiaojun, Xiaotong'da kucaklaşmak için kamp yapıyordu.

-

- 190614 Stüdyo sıcak bar yüzme havuzu güzellik fotoğrafı, sıcak yaz havalı güzel kız en baştan çıkarıcı

-

- "TWICE" "Hisse" 190614 Jeongyeon da yola çıktı! Bu öğleden sonra Incheon Havaalanı'ndan Tayland'a hareket

-

- ABD'nin Çin'deki vergi artışına karşı çıkmak için, oyun endüstrisindeki üç dev, on yıllardır güçlerini birleştirdi.

-

- Derin takviye öğreniminin ödül mühendisliği kullanması gerekiyor mu? Berkeley AI Enstitüsü: Gerek yok