UVM'ye Dayalı Temel Bant RF Arayüz Devresinin Doğrulanması

Özet: UVM doğrulama metodolojisinin verimliliğini hedefleyen ve UVM'nin yeniden kullanılabilirliğinin özelliklerini birleştiren, temel bant radyo frekansı arayüz devresinin işlevini doğrulamak için hiyerarşik modül düzeyinde bir doğrulama platformu oluşturuldu. Doğrulama analizi, temel bant radyo frekansı arayüz donanım devresi mimarisinin UVM ortamına aktarıldığını, bu da sadece kod kapsamını ve işlev kapsamını iyileştirmekle kalmayıp, aynı zamanda doğrulama verimliliğini de büyük ölçüde geliştirdiğini göstermektedir. Aynı zamanda, donanım RTL'si DC (Design Compiler) tarafından kısıtlandıktan sonra, RF arayüz devresinin alıcı yolunun alanı 0,3 mm2 ve güç tüketimi 39 mW; RF arayüz devresinin iletim yolunun alanı 0,5 mm2 ve güç tüketimi 58 mW'dir.

TN47

Bir

10.16157 / j.issn.0258-7998.172650

Çince alıntı biçimi: Xu Fei, Qin Shuijie. UVM'ye dayalı temel bant radyo frekansı arayüz devresinin doğrulanması. Application of Electronic Technology, 2018, 44 (3): 11-14.

İngilizce alıntı biçimi: Xu Fei, Qin Shuijie. UVM'ye dayalı temel bant RF arayüz devresinin doğrulanması. Application of Electronic Technique, 2018, 44 (3): 11-14.

0 Önsöz

SoC temel bant yongalarının son derece entegre tasarımıyla, tüm Ar-Ge aşamasının% 70'ini oluşturan doğrulama döngüsü artmaya devam edecek. Temel bant yonga doğrulamasını daha verimli hale getirmek için, mevcut ana akım UVM doğrulama metodolojisi benimsenmiştir. UVM doğrulama metodolojisi, 2011 yılında Accellera tarafından resmi olarak piyasaya sürüldü. Oluşturulan doğrulama platformu yalnızca birçok kullanılabilir arayüz sağlamakla kalmaz, aynı zamanda çeşitlendirilmiş Cadence VIP, UVM ortamı için gerekli bileşenleri de sağlar. Bu nedenle, yüksek kapsama fonksiyonu doğrulaması elde edilebilir ve simülasyon doğrulama süresi büyük ölçüde azaltılabilir.

Temel bant radyo frekansı arabirim devresi, temel bant yongasını ve radyo frekansı yongasını bağlayan dijital bir seri arabirimdir. Bu tür bir dijital seri arayüz sadece donanım kaynaklarını korumakla kalmaz, aynı zamanda temel bandın, taşıyıcı birleştirme yoluyla yukarı bağlantı ve aşağı bağlantı hava arayüzlerinin daha yüksek bir tepe iletim hızına ulaşmasını sağlar. Karmaşık özelleştirme protokolü arayüzü nedeniyle, radyo frekansı arayüz devresinin işlevini hızlı ve kapsamlı bir şekilde doğrulamak için uygun bir doğrulama platformu inşa edilmelidir. Bu makale, temel bant radyo frekansı arayüz devre modülünü doğrulamak için UVM doğrulama metodolojisini kullanacaktır Doğrulama yöntemi, radyo frekansı alıcı-verici yolunun tüm işlevsel noktalarını tamamen kapsayacaktır.

1 UVM doğrulama platformu

Sistem Verilog donanım doğrulama diline dayalı UVM özelliklerine dayalı Doğrulama kapsamında, doğrulamanın net bir şekilde çalışmasını sağlamak için UVM kitaplığı aracılığıyla çeşitli doğrulama bileşenlerini çağırır. Bu UVM kitaplığı esas olarak aşağıdaki bölümleri içerir: Birincisi, hiyerarşik bir doğrulama yapısı. Temsilci esas olarak sürücüyü ve diğer modülleri entegre eder; sürücü, oluşturulan uyaranı kurallara göre DUT'un pimlerine veya içine eklemekten sorumludur; monitör, DUV'nin dahili sinyalini ve çıkışını algılar ve çeşitli izleme işlemlerini gerçekleştirir; Scoreboard, DUV değerini Modelin beklenen değeri ile karşılaştırır; Referans modeli, beklenen değeri çıkarmak için SystemVerilog tarafından oluşturulan DUT ile ilgili modeli kullanır. İkinci olarak, UVM sıralayıcı (Sıralayıcı), sürücünün işlem tipi veri paketlerini elde etmesini sağlamak için bir tahkim dizisi (Sıra) modülü sağlar. Üçüncüsü, çeşitli bileşenlerin UVM ortamında hızlı entegrasyonunu sağlamak için Fikri Mülkiyet Çekirdeği (VIP) sağlayın.

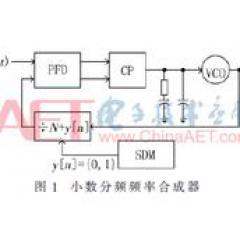

Tipik bir UVM doğrulama platformu Şekil 1'de gösterilmektedir. Doğrulama ortamında, uvm_env tüm doğrulama bileşenlerini içerir ve iki doğrulama tasarımı platforma bir veri yolu arayüzü aracılığıyla bağlanır. Yukarıdan aşağıya yapısal spesifikasyona uygun olarak, doğrulama platformu, en üst düzey env'den beş modül, iki giriş proxy modülü, bir çıkış proxy modülü, bir referans model modülü ve bir puan tablosu modülü oluşturur. Giriş aracısı modülü ilk olarak doğrulama ortamını yapılandırır ve daha sonra uyarma kaynağını sıralayıcı modülü aracılığıyla sürücü modülüne iletir Sürücü modülü, verileri arayüz aracılığıyla bağımlı alıcıya iletir ve monitör, tasarımı doğrulamak için sürücünün veri sinyalini toplayabilir. Çıkış vekil izleme modülü, doğrulama tasarımının çıkış sinyalini gerçek zamanlı olarak örnekler, toplanan sonuçları puan tablosu modülüne koyar ve doğrulamanın hata oranını azaltmak ve doğrulama riskini azaltmak için referans model modülünün çıktı bilgileri ile karşılaştırır.

2 Temel bant radyo frekansı arayüz devre modülü

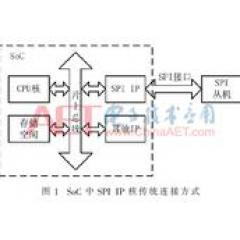

Ana bant radyo frekansı arayüz modülü, alıcı kanal modülünü ve radyo frekansı arayüzünün verici kanal modülünü içerir. Temel bant radyo frekansı arayüz modülünün mimari diyagramı Şekil 2'de gösterilmektedir. Bu radyo frekansı arabirim modülü, AXI standart veri yolu protokolünü benimser ve bağımlı adres ve veri sinyallerini X2P aktarım köprüsü aracılığıyla yapılandırma modülüne iletir. Alıcı kanalın zamanlama etkinleştirme konfigürasyonu GPIO aracılığıyla çıkarılır ve SPI, okuma ve yazma kayıtlarını konfigüre ederek harici RF çipini kontrol eder Alıcı kanal durumu, alıcı kontrol kayıt modülü tarafından konfigüre edilir ve RF alımı, konfigüre edilebilir bir TBU zaman noktasında açılır ve kapanır. Temel bant radyo frekansı arayüzü tarafından alınan veri akışı, iki FIFO tarafından ara belleğe alınır ve daha sonra, veri akışını AXI ana bilgisayarı üzerinden temel bant yongasındaki belleğe taşımak için iki DMA seti kullanılır. Gönderme yolu süreci ve alıcı yol süreci tersine çevrilir. Gönderme durumu, gönderme kontrol kaydı aracılığıyla yapılandırılır ve radyo frekansı gönderimi, yapılandırılabilir TBU zaman noktasında açılır ve kapatılır. Temel bant yonga ana bilgisayar belleğinin veri akışı, AXI veriyolundan geçer ve arabelleğe almak için 4 set DMA kullanır Sonunda radyo frekansı çipine dört FIFO gönderilir. Radyo frekansı arayüzünü alma ve gönderme sürecinde, DMA aktarım görevi tamamlandıktan sonra, bir kesme verilir ve kesme ARM işlemcisine iletilir, böylece ARM işlemcisi döngüsel olarak yanıt verir ve birden çok görevi yapılandırır. FIFO verilerini yeniden arabelleğe almak istiyorsanız, FIFO'yu temizlemeniz, yapılandırılabilir TBU zaman noktasında kaydı sıfırlamanız ve çıktı verilerini geçerli örnekleme noktasından FIFO'nun başlangıç adresine yazmanız gerekir.

Temel bant radyo frekansı arabirimi, ilgili arabirim oranını desteklemek için çok modlu ve çok bantlı bir veri arabirimi kullanır.CCMOS TDD (Tamamlayıcı Metal Oksit Yarı İletken Zaman Bölmeli Dubleks) modu, iki set 12 bit veri hattı kullanır ve veri iletimi yarım çift yönlü mod, bir saat döngüsü kullanır Çift antenli sembol verisi gönderebilir. CMOS FDD (Complementary Metal Oxide Semiconductor Frequency Division Duplex) modunda, veri aktarım hızı CMOS TDD modunun veri çıkış hızının iki katıdır. LVDS (düşük voltaj diferansiyel sinyalleme) modu veri aktarım hızı, CMOS TDD modunun veri çıkış hızının 4 katıdır.

3 Temel bant RF arayüz devreleri için UVM tabanlı bir doğrulama platformu oluşturun

3.1 Temel bant RF arayüz devresi doğrulama süreci

Temel bant radyo frekansı arayüzü, sırasıyla temel bant radyo alıcı yol modülünü ve gönderici yol modülünü doğrulamak için AXI veriyolu mekanizmasını kullanır Doğrulama işlemi Şekil 3'te gösterilmektedir. Doğrulama ortamında, yazılım arayüzü veri paketi sanal sıralayıcıya yerleştirilir ve AXI arayüzü yoluyla axi_sequencer'a iletilir Sürücü, axi_sequence tarafından üretilen uyarma sinyalini alır Bu uyarma sinyalleri, sırasıyla alıcı yolun doğrulama tasarımı ve gönderme yolunun doğrulama tasarımı üzerinde hareket eder. Aynı anda somutlaştırılan iki axi_monitor, yalnızca sürücünün RF alma ve gönderme doğrulama tasarımına veri akışını izlemekle kalmaz, aynı zamanda kayıt modelini de izler Bu kayıt modeli, RF arayüzü ile aynı veri iletim işlevini elde etmek ve veri bilgisini ölçüm cihazına koymak için MATLAB kullanır. Skor tahtası. Başka bir axi_monitor, radyo frekansı alan ve skorbord'a gönderilen kanal veri bilgilerinin iletimini izler.Kayıt modeli ve izleme ile oluşturulan veriler puan tablosuna iletildikten sonra, skorbord, simülasyonun olup olmadığını belirlemek için iki veriyi karşılaştıracaktır. anormal.

3.2 UVM'ye dayalı temel bant radyo frekansı arayüz devre doğrulama platformu

Temel bant radyo frekansı arayüz devresinin doğrulama platformu, Şekil 4'teki gibi gösterilmiştir. Test edilecek doğrulama tasarımı, esas olarak, doğrulama nesnesini ve doğrulama vektörünü arayüz aracılığıyla birbirine bağlayan bir gönderen modül ve bir alıcı modüldür ve doğrulama vektörü, test nesnesi ile aynı işlevi gerçekleştirmektir. Doğrulama ortamındaki Aracı, VIP tarafından sağlanır ve kalan bileşenlerin kendileri tarafından tasarlanması gerekir. Doğrulama ortamı, üst düzey ortam aracılığıyla iki i_axi_agents'ı somutlaştırır. Bu iki i_axi_agents, diğer doğrulama bileşenlerini içerir ve dahili sıralayıcı, sürücü ve monitör, her doğrulama bileşeninin yakından bağlanabilmesi için build_phase aracılığıyla oluşturulur. Bu iki i_axi_agent bileşen paketi, konfigüre edilmiş aktif ve pasif modların arayüz üzerindeki veri bilgisini sürmesini ve izlemesini sağlamak için sırasıyla radyo frekansı arayüzünün verici modülü ve alıcı modülü üzerinde hareket eder. O_axi_agnet somutlaştırma modülündeki monitör, test nesnesi tarafından gönderilen uyarıcı veri akışını izleyebilir ve bunu TLM arayüz mekanizması yoluyla uvm_scoreboard'a iletebilir. Aynı zamanda, Matlab tarafından kapsüllenen kayıt_modeli modeli, pasif mod tarafından işgal edilen monitör aracılığıyla gönderen ve alan model veri akışlarını izler ve izleme ile çıkarılan model veri akışı, DUV tarafından üretilen uyarma verileri bilgisi ile karşılaştırılmalıdır. Nihai karşılaştırma veri akışı bilgisi, alma ve gönderme işlemi sırasında temel bant radyo arayüzünün veri bilgilerinin eksiksiz olup olmadığını ve istatistiksel kapsama gereksinimlerinin standartlara uygun olup olmadığını belirlemek için uvm_scoreboard puan tahtası aracılığıyla çizilir.

Ana bant radyo frekansı arayüzü içindeki her kayıt modülü adresleri ve verileri APB veriyolu üzerinden iletir ve ana bilgisayar aktarım köprüsü X2P genel bir IP olarak kayıtlara kullanılabilir adres alanı tahsis eder. Bu kayıt modelleri, esas olarak RF alıcı-verici yolu için etkinleştirici bilgiler sağlamak üzere dahili olarak birçok kez başlatılabilir. DMA modülü, radyo frekansı alıcı-verici modülünün uyarı bilgisini doğru belleğe taşımak içindir Sınırlı çerçeve veri akışı hareket ettirildiğinde, bir kesinti mesajı üretilecektir Kesinti mesajı ARM işlemcisine girecek ve çekirdek, radyo frekansı alıcı-vericisini önlemek için bir talimat yayınlayacaktır. SPI modülünün tanıtımı, RF alıcı-vericinin FIFO'yu normal olarak okumasını ve yazmasını sağlar ve aynı zamanda harici RF ek kartı için mod değiştirme işlevi sağlar. Ancak ana bant radyo frekansı arayüzündeki mod anahtarı, mod kayıt modülünü kullanır. Bu kayıt modülleri, gerekli uyarımı elde etmek için RF alıcı-verici yoluna rastgele kısıtlamalar sağlamak için kullanılır.

RF alıcı-verici kanalının rasgele kısıtlama bilgilerinin, ARM işlemcisinin yazılım ortamı aracılığıyla yapılandırılması gerekir ve kısıtlama öğeleri, veri uyarımı, RF alıcı-verici kanalını sürmek için bir koşul haline gelebilir ve RF alıcı-verici modülünün normal çalışmasını kolaylaştıracak şekilde aktarım veri paketinde depolanır. Aynı zamanda, bu kısıtlama maddeleri kısıt değişkenlerini bildirirler Değişkenlerin listesi Tablo 1'de gösterilmiştir.

Axi_sequencer, tahrik kaynağını axi_driver sürücüsüne iletir ve axi_driver'ın test edilen modülü sürmek için yazılım tarafından yapılandırılması gerekir. Şekil 5, RF alıcı-verici sürücü konfigürasyon bilgisini oluşturmak için zamanlama diyagramını göstermektedir. Yazılım yapılandırma ortamı aşağıdaki gibidir: (1) Radyo frekansı yolunu başlatın, hem alma hem de gönderme yollarını açın, rx_path_mask'i 3 bit'e ve tx_path_mask'i 15 bit'e ayarlayın. Mod anahtarı burada da gerçekleştirilmelidir ve arayüzün CMOS TDD modunda mı, CMOS FDD modunda mı yoksa LVDS modunda mı çalışacağını seçmek için rx_mode ve tx_mode yazılım yapılandırması yapılmalıdır. (2) Saat frekansı, gereksinimleri karşılayan ilgili bant genişliğinin arayüz frekansını karşılamak için harici LPCU modülünü kontrol edecek şekilde yapılandırılmıştır. (3) Alma ve iletme kanalı etkinleştirme bilgisini yapılandırın, etkinleştirme, alma kanalı veri kaynağının başlangıç bilgilerini sağlar, tx_on, iletim kanalı veri kaynağının konum bilgilerini sağlar ve txnrx, RFIC simülasyon modeli için iletim kanalı etkinleştirme sinyalini sağlar. (4) Temel bant çipinin belleğinin veri göndermesini veya almasını sağlamak için DMA adresini ve DMA uzunluğunu girin.Veri akışı bilgisi elde edildiğinde, mikroişlemciye (arm) yalnızca bilgi etkinleştirildiğinde bir sonraki çerçeve veri işlemesini beklemesi için bildirimde bulunmak üzere bir kesme dmareq verilir. Etkinleştirildiğinde, tx_on ve txnrx düşük seviyeye geldiğinde, veri iletimi sona erebilir. (5) Harici radyo frekansı alt-kartının mod değiştirmesini kontrol etmek için SPI okuma ve yazma yazmaçlarını yapılandırın, bu temel bant radyo frekansı arayüz modu ile tutarlıdır.

Kayıt modeli, MATLAB tarafından kapsüllenmiş bir modeldir. Bu model, bir gönderme ve alma veri kaynağı modülü, bir veri formatı dönüştürme modülü, bir zamanlama kayıt modülü, bir saat kaynağı modülü ve bir gönderme ve alma veri kayıt modülü içerir. Gönderme ve alma veri kayıt modülünün veri akışı, skor tahtası tarafından adlandırılan bir yazma işlevi olacaktır. Bunu FIFO'da saklayın ve ardından FIFO'da depolanan veri akışını DUV'deki veri akışı ile karşılaştırmak için karşılaştırma işlevini çağırın Karşılaştırma tutarlıysa doğrulama başarılı olur; aksi takdirde doğrulama başarısız olur. Böyle bir karşılaştırma yöntemini benimsemenin nedeni, karmaşık veri karşılaştırmasında doğrulama doğruluğunun iyileştirilmesi ve referans modelin, RF arayüz devre fonksiyonunun bütünlüğünü ve güvenilirliğini analiz etmek için rasyonelleştirilmesidir.

3.3 Doğrulama sonuçları

Bu doğrulama, radyo frekansı alıcı vericinin işlev noktalarını test etmek ve her bir işlev noktasına karşılık gelen işlev kapsamını hesaplamak için örnek olarak RFIU TDD 20 M test durumunu alır.Radyo frekansı alıcı-verici modülünün işlev kapsamı% 100'dür ve radyo frekansı Alıcı ve gönderen kanalın RTL'si kod kapsamı istatistiklerini gerçekleştirir ve kod kapsamı% 100'dür. UVM doğrulaması yoluyla, puan tablosundaki veriler kayıt_modeli referans modelinin verileriyle karşılaştırılır ve monitör otomatik olarak rolü izler ve veri karşılaştırmasının tutarlılığı% 100'dür. Kalan birkaç test durumunun işlevsel kapsamı% 100'e ulaşabilir ve puan tablosunda elde edilen veri karşılaştırma derecesi% 100'dür, bu da RF arayüzü alıcı-verici modülünün işlevsel gereksinimlerinin karşılandığını gösterebilir.

Synopsys'in Tasarım Derleme aracına göre, RF arayüz devresinin RTL kodu sentezlenir ve RF alma yolunun kısıtlı alanı 0,3 mm2 ve güç tüketimi 39 mW; RF arayüz devre gönderme yolunun kısıtlı alanı 0,5 mm2 ve güç tüketimi 58 mW . Tasarım sentez raporu Şekil 6'da gösterilmektedir.

4. Sonuç

UVM, dijital IC doğrulaması için en modern metodolojidir Ön uç simülasyon platformunun uzun bir süresi olmasına rağmen, yürütme verimliliği çok yüksektir ve bu da tüm Ar-Ge'nin doğrulama süresini önemli ölçüde kısaltır. Bu makale, RF arayüz alıcı-verici modülünün işlevini gerçekleştiren ve tüm temel bant yongasının sorunsuz seri üretimine elverişli olan belirli bir aralıktaki kısıtlı alanı ve güç tüketimini kontrol eden UVM tabanlı bir temel bant RF arayüz devre doğrulama platformu oluşturmak için AXI veri yolu doğrulama bileşenlerini kullanır. Aynı zamanda, temel bant çipinin diğer modülleri üzerinde bu doğrulama mimarisinin kullanılması doğrulama verimliliğini artırabilir ve ana bant radyo frekansı arayüz devresinin UVM doğrulama platformunun önemli bir yol gösterici rol oynamasını sağlayabilir. Dijital arayüz tasarımında önemli uygulama değerine sahiptir.

Referanslar

SALAH K.A UVM tabanlı akıllı işlevsel doğrulama platformu: Konsept, artıları, eksileri ve fırsatları // Tasarım ve Test SyMposium (I-DT), 9. Uluslararası Ölü Deniz: IEEE, 2014: 94-99.

Zhang Qiang. UVM savaşı. Pekin: Makine Endüstrisi Basını, 2014.

SPEAR C. Doğrulama için sistem perdesi Synopsyns Inc., 2008: 5.

ROSENBERG S, MEAD K A. Evrensel doğrulama metodolojisini (UVM) benimsemek için pratik bir rehber ABD: Cadence Design System, 2010.

Xiong Tao, Jiang Jianhua.UVM Doğrulama Metodolojisine Dayalı Dikey Yeniden Kullanılabilirlik Araştırması Mikroelektronik ve Bilgisayar, 2016, 33 (4): 64-68.

yazar bilgileri:

Xu Fei 1, 2, Qin Shuijie 2

(1. Büyük Veri ve Bilgi Mühendisliği Okulu, Guizhou Üniversitesi, Guiyang 550025, Guizhou; 2. Optoelektronik Teknolojisi ve Guizhou Eyaleti, Guiyang 550025 Uygulaması Anahtar Laboratuvarı)