Yüksek hızlı CMOS görüntü depolama ve gerçek zamanlı görüntüleme sistemi tasarımı

Ma Lin 1, 2, Li Jinming 1, 2, Zhang Huwei 1, 2, Hou Tianxi 1, 2, Jiang Shuai 1, 2

(1. Eyalet Anahtar Elektronik Test Laboratuvarı, Kuzey Çin Üniversitesi, Taiyuan 030051, Shanxi;

2. Eğitim Bakanlığı'nın Enstrüman Bilimi ve Dinamik Test Temel Laboratuvarı, Çin Kuzey Üniversitesi, Taiyuan, Shanxi 030051)

Geniş veri hacmi, yüksek hız ve telemetri sisteminin görüntü birimini doğrudan depolayamama ve görüntüleyememe sorunlarına yönelik olarak yüksek hızlı görüntü depolama ve gerçek zamanlı görüntüleme sistemi tasarlandı. Sistem, çekirdek işlemci olarak Spartan 6 serisi alan programlanabilir geçit dizisini (FPGA) kullanır, CMOS kamera tarafından görüntü verisi çıktısını toplamak için Tam mod Kamera Bağlantısı arayüzünü kullanır ve görüntü verilerini SATA denetleyicilerinden oluşan disk dizisine yazmak için DDR3 ping-pong önbellek teknolojisini kullanır İşlenen veriler bilgisayara Gigabit Ethernet arayüzü üzerinden yüklenir; görüntü verileri, çerçeve çıkarma ve çözünürlük azaltma şeklinde 1.024 × 768 piksel VGA çözünürlük formatına dönüştürülür.Son olarak, VGA arayüzü Görüntü gerçek zamanlı olarak görüntülenir. Deneysel sonuçlar, sistemin uzun süre 2048 × 2048 piksel çözünürlük ve 150 f / s kare hızı ile yüksek hızlı görüntü verilerini depolayabildiğini ve görüntüleyebildiğini göstermektedir.

Çin Kütüphanesi Sınıflandırma Numarası: TN919.5

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.2017.06.002

Çince alıntı biçimi: Ma Lin, Li Jinming, Zhang Huwei, vb. Yüksek hızlı CMOS görüntü depolama ve gerçek zamanlı görüntüleme sistemi tasarımı Elektronik teknoloji uygulaması, 2017, 43 (6): 7-10, 14.

İngilizce alıntı biçimi: Ma Lin, Li Jinming, Zhang Huwei, ve diğerleri.Yüksek hızlı CMOS görüntü depolama ve gerçek zamanlı görüntüleme sistemi tasarımı.Elektronik Tekniğin Uygulanması, 2017, 43 (6): 7-10, 14.

0 Önsöz

Havacılıkta görüntü izleme alanında, yüksek çözünürlüklü, yüksek kare hızlı endüstriyel kameralar çok çeşitli uygulamalara sahiptir.Yüksek hızlı uçakların uçuş tutumunu etkin bir şekilde yakalayabilir ve son olarak, çalışma hızını, ivmesini vb. Çıkarmak için görüntüyü bilgisayar aracılığıyla analiz edip işleyebilirler. Önemli parametreler. Endüstriyel kamera çözünürlüğünün ve kare hızının sürekli iyileştirilmesiyle, özellikle insanlı uzay uçuşu testi alanında, görüntü depolama sistemleri için gereksinimler gittikçe artmaktadır, depolama sistemleri karmaşık çalışma koşullarıyla başa çıkabilmelidir. Nand Flash ve mekanik sabit sürücüler gibi geleneksel depolama ortamları, küçük kapasite, karmaşık çalışma ve zayıf anti-parazit yeteneği gibi eksikliklere sahiptir.SD katı hal sürücüleri, büyük kapasiteleri, yüksek hızları ve iyi çevresel özellikleri nedeniyle bilimsel araştırmalarda, havacılık ve askeri testlerde kullanılır. Ve diğer alanlarda geniş uygulama olanakları vardır.

Bu aşamada, geleneksel Flash esas olarak görüntü verilerini toplamak için kullanılır. Veri depolama için dokümanlar ve Flash dizilerinin kullanılması, okuma ve yazma hızını belirli bir dereceye kadar iyileştirmiştir, ancak karmaşık arayüz işlemleri ve zayıf kararlılık gibi dezavantajlara sahiptir. Literatür, görüntü verilerini gerçek zamanlı olarak görüntülemek için bir çerçeve yakalayıcı kullanır, bu da sistemin hacmini ve karmaşıklığını artırır ve görüntünün çözünürlüğü yüksek değildir. Bu belge, FPGA kullanarak sistem işlevlerini geliştirir ve yüksek hızlı görüntüleri depolamak için bir depolama dizisi oluşturmak için 4 SSD katı hal sabit disk kullanır.Orijinal görüntü verileri, uçak kurtarıldıktan sonra okunabilir ve görüntü verileri, çerçeve çıkarma ve azaltılmış çözünürlük şeklinde işlenir. Gerçek zamanlı görüntüleme, telemetri verileri döndürüldüğünde bant genişliği işgalini azaltmak için görüntü verilerinin büyük kapasiteli, yüksek hızlı depolamasını ve gerçek zamanlı gösterimini gerçekleştirir ve taşınabilirliğe sahiptir.

1 Sistemin genel tasarımı

Sistem tasarımının genel blok şeması Şekil 1'de gösterilmektedir. Sistem, Point Gray tarafından üretilen GZL-CL-41C6 model yüksek hızlı gri tonlamalı kamerayı seçer, Kamera Bağlantısı arayüzü aracılığıyla görüntü verilerini ve senkronizasyon sinyallerini gönderir ve seri bağlantı noktası üzerinden kamera kontrol komutlarını alır.Görüntü çözünürlüğü 2.048 × 2.048 piksel ve kare hızı 150'dir. f / s, piksel biçimi 8 bittir. Kamera tarafından oluşturulan veri miktarı yaklaşık 600 MB / sn olduğundan ve SATA2.0 arabirimli tek bir katı hal sürücüsünün yazma hızı yaklaşık 180 MB / sn olduğundan, depolama için bir RAID0 dizisi oluşturmak için 4 katı hal sürücüsü kullanılır. Sistem, endüstriyel kamera tarafından yüksek hızlı görüntü verisi çıktısını toplar ve verileri FPGA'ya gönderir ve iki kanala böler. Bir kanal DDR3 önbelleğinde paralel olarak depolanır ve yarıiletken sürücünün tüm sütununda saklanır; diğer kanal biçimlendirilir ve DDR3 önbelleğinde depolanır ve ardından VGA'dan geçirilir Arayüz, görüntü verilerini gerçek zamanlı olarak görüntüler.

2 Sistem donanım devre tasarımı

2.1 Görüntü alma modülü

Sistemin ön uç endüstriyel kamerası, piksel verilerini, yani bir seferde 8 piksel veriyi çıkarmak için 8 dokunma modunu kullanır, bu nedenle Tam mod Kamera Bağlantısı arayüz devresini kullanır. Tam modda, Camera Link arabirimi, 3 veri arabirimi yongası, bir kamera kontrol yongası ve bir seri iletişim yongası gerektiren iki konektör kullanır. Arayüz yongası, Camera Link kablosu tarafından iletilen LVDS diferansiyel sinyalini, FPGA'nın doğrudan işleyebileceği bir TTL seviyesi sinyaline dönüştürür.

Kamera ile FPGA arasındaki bağlantının şematik diyagramı Şekil 2'de gösterilmektedir. Sistem, veri alma yongası olarak TI tarafından üretilen DS90CR288A'yı, kontrol yongası olarak DS90LV-047ATM'yi ve seri iletişim yongası olarak DS90LV019TM'yi seçer. Bunların arasında D0 ~ D23 veri sinyalleri, FVAL, LVAL, DVAL senkronizasyon sinyalleridir, CC1 ~ CC4 kamera kontrol sinyalleridir, SerTC ve SerTFG seri iletişim sinyalleridir.

2.2 VGA sürücü devresi

FPGA'nın çıkışı 3,3 V'luk bir seviye sinyalidir ve VGA arayüzünün gerektirdiği giriş sinyali 0 ~ 0,714 V'lik bir analog sinyaldir, bu nedenle VGA ekran gereksinimlerini karşılamak için FPGA'nın çıkış sinyali D / A'ya dönüştürülerek 0 ~ elde edilmelidir. 0,714 V analog sinyal girişi. Sistem, VGA sürücüsünü uygulamak için ADI tarafından üretilen video dönüştürme yongası ADV7123'ü kullanır Kamera tarafından görüntü verisi çıkışı gri tonlamalı bir görüntü olduğundan, üç kanaldan biri R, G ve B FPGA'ya bağlanır ve diğer ikisi topraklanır. Bu tasarımda, FPGA çıkışı kırmızı giriş bağlantı noktasına bağlanır ve kullanılmayan yeşil ve mavi analog sinyaller 37,5 terminal direncine bağlanır.

2.3 Gigabit Ethernet arayüz devresi

Sistem, Gigabit Ethernet veri iletimini gerçekleştirmek için Realtek tarafından üretilen Ethernet alıcı-vericisi RTL8211EG'yi kullanır. Bağlantı katmanı, aktarım katmanı ve ağ katmanı UDP / IP protokolünü kullanır ve FPGA tarafından uygulanır. RTL8211EG ve FPGA arasındaki devre bağlantısının şematik diyagramı Şekil 3'te gösterilmektedir. RTL8211EG, esas olarak MAC katmanını ve Ethernet'in PHY katmanını bağlamak için kullanılan GMII arabirimi aracılığıyla FPGA ile bağlantılıdır. Veri aktarımı için Gigabit Ethernet kullanırken, arayüz saati 125 MHz'dir. Bunlar arasında, alıcı saat RTL8211EG'nin E_RXC'si tarafından sağlanır; gönderme saati, FPGA'nın E_GTXC'si tarafından sağlanır ve hem alma hem de gönderme verileri, saatin yükselen kenarında örneklenir.

3 Sistem yazılım tasarımı ve simülasyonu

3.1 Görüntü gerçek zamanlı görüntüleme modülü

Sistem kamerasının çıkardığı görüntü 2048 × 2048 piksel çözünürlüğe ve 150 f / s kare hızına sahiptir.Hem çözünürlük hem de kare hızı, genel VGA arayüz monitörünün görüntü formatını aştığından, çözünürlüğü azaltmak için çerçeve örnekleme kullanılabilir. Görüntüyü oranlı bir şekilde görüntüleyin.

3.1.1 Görüntü sıkıştırma biriminin tasarımı

Sistem, görüntüyü Şekil 4'te gösterildiği gibi 2.048 × 2.048 piksellik orijinal çözünürlükle küçültür, 3 × 3 aralığındaki 9 piksel veriyi 1 piksel veriye sentezler ve sonunda 682 × 682 piksel çözünürlük elde eder. Resmi biçimlendirin. Görüntüdeki gürültü sinyalinin etkisini azaltmak için sentez için medyan 9 piksel veri alma yöntemi kullanılmaktadır.

FPGA programlamasında, algoritmayı uygulamak için 9 FIFO kullanılır ve uygulama yöntemi Şekil 5'te gösterilmiştir. Her FIFO'nun boyutu 1024 × 8 bittir ve 3 sıra piksel verisi 9 FIFO aracılığıyla arabelleğe alınır. Bunlar arasında, sırasıyla ilk satırın birinci, ikinci ve üçüncü verilerini depolamak için önce FIFO1, FIFO2 ve FIFO3'ü kullanın ve ardından ilk satırın 4., 5. ve 6. verilerini ilk satır saklanana kadar saklayın; daha sonra kullanın FIFO4, FIFO5 ve FIFO6 ikinci veri satırını aynı şekilde arabelleğe alır ve FIFO7, FIFO8 ve FIFO9 üçüncü veri satırını arabelleğe alır. İlk üç veri satırı arabelleğe alındıktan sonra, 4., 5. ve 6. veri sıralarını depolamak için başka 9 FIFO kullanılır ve ilk FIFO grubu ile bir ping-pong arabellek yapısı oluşturur. Bu şekilde, her bir FIFO grubu, bir döngüde işlenecek 9 piksel veriyi okuyabilir ve bu 9 verinin medyan değerini çıkarabilir.

N'nin tek sayı olduğu medyan işlemler için, N 9 ise, gerekli karşılaştırma sayısı 36 kattır FPGA paralel işlemenin avantajlarını birleştirerek ve 36 karşılaştırıcıyı aynı anda kullanarak maksimum işlem hızı elde edilebilir. Ek olarak, VGA monitörün çözünürlüğü 1024 × 768 piksel ve işlenen görüntü çözünürlüğü 682 × 682 pikseldir, bu nedenle görüntü monitörün merkezinde görüntülenmelidir.VGA sürücü ekranı gerçekleştirildiğinde, diğer pikseller 0 ile doldurulabilir, yani Siyah görüntü.

3.1.2 Çerçeve çıkarma tampon modülü

Kamera çıktı görüntüsünün kare hızı 150 f / s olduğundan ve yaygın olarak kullanılan VGA çözünürlük formatının kare hızı genellikle 75 Hz'nin altında olduğundan, VGA arayüzünün çözünürlüğü ile eşleşmek için kamera görüntüsü çerçevelenir ve arabelleğe alınır ve her iki karede bir kare çıkarılır. Çerçeveler sıralı olarak iki DDR3 yongasında saklanır ve son olarak 1024 × 768 @ 75 formatında VGA çözünürlüğü ile görüntülenir.

Çerçeve çiziminin zamanlama diyagramı Şekil 6'da gösterilmektedir. Kamera çerçevesi senkronizasyon sinyali FVAL, çerçeve kontrol sinyali F_Control'ü elde etmek için 4'e bölünür ve ardından sıfırlama sinyali üretilirken F_Control'ün kenarı ile bir FVAL yükselen kenar sayacı CNT'ye bölünür. F_Control düşük olduğunda, CNT 1 olan çerçeve görüntüsü tampon 1'de saklanır; F_Control yüksek olduğunda, CNT 1 olan çerçeve görüntüsü arabellek 2'de saklanır. Okuma tamponu, yazma tamponunun tersidir Tampon 2'deki veriler F_Control düşük olduğunda okunur; tampon 1'deki veriler F_Control yüksek olduğunda okunur.

Program tasarımı sırasında, herhangi bir çözünürlük ve kare hızının görüntü formatı dönüşümünü elde etmek için görüntü çözünürlüğü, görüntü ölçekleme faktörü, görüntü kare hızı ve kare hızı katsayısı gibi temel parametreleri makro olarak tanımlamak için Verilog HDL dilinde sözdizimini tanımlayın, böylece Model değişikliklerini ve sistem geçişini kamera ve izleyin.

3.2 Görüntü depolama modülü

Sistem, SATA2.0 denetleyicisinin fiziksel katmanını gerçekleştirmek için Spartan6-T serisi FPGA'daki GTP yüksek hızlı seri alıcı-vericiye dayanır ve bağlantı katmanının, iletim katmanının ve komut katmanının gelişimini gerçekleştirmek ve sonunda SATA2'yi gerçekleştirmek için Verilog HDL dilini kullanır. 0 protokollü DMA aktarımı.

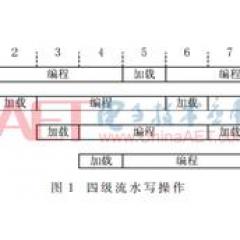

Görüntü depolama gerçekleştirilirken, görüntü toplama modülü tarafından toplanan veriler ilk olarak asenkron FIFO aracılığıyla dönüştürülür.Sistem, DDR3 belleğini kontrol etmek için FPGA'daki MCB (Bellek Denetleyici Bloğu) sabit çekirdeğini kullanır. Bant genişliğini en üst düzeye çıkarmak için kullanıcı portu Bit genişliği 128 bit olarak seçilir, bu nedenle Camera Link arayüzünün 64 bit genişliğindeki verisini 128 bit genişliğinde veriye dönüştürmek ve ardından verileri veri dağıtım modülüne girmek gerekir. Veri dağıtım modülü süreci Şekil 7'de gösterilmektedir. Sistem tarafından kullanılan DDR3 bellek modeli, 512 MB kapasiteli MT41J256M16'dır.Üst ve alt yarım sayfalara bölünmüştür.Veriler, ardışık düzen şeklinde 256 MB birimlerde iki DDR3 diliminde depolanır.

Sistem tarafından kullanılan SATA denetleyicisinin adresleme modu mantıksal blok adreslemedir ve her mantıksal bloğun boyutu 512 B'dir. Depolama bant genişliği kullanımını en üst düzeye çıkarmak için, yazma burst okuma ve yazma kontrol portu cmd_bl'nin bit genişliğinin 18 bit, maksimum okuma ve yazma derinliğinin 262144 olduğu ve bir seferde 262144 × 512 B okuyup yazabildiği, yani 128 olan burst okuma ve yazma modu kullanılır. MB veri. Sabit disk depolama veri tahsis akış şeması Şekil 8'de gösterilmektedir. DDR belleğinin her yarım sayfası, 128 MB'lık birimler halinde tekrar bloklara bölünmüştür. SATA denetleyicisi 0 ~ SATA denetleyicisi 4, komutlara göre sırasıyla DDR3_0 ve DDR3_1'deki verileri okur ve Katı hal sürücüde boru hattıyla saklanır.

4 Sistem testi

Sistem işlevinin doğruluğunu onaylamak için, sistem depolama modülü ve ekran modülü sırasıyla test edilmiştir. Test için Samsung'un 750 EVO katı hal sabit sürücüsünü kullanın, denetleyici sabit disk verilerini okurken veya yazarken, SATA denetleyici veri bağlantı noktasına bir tetikleme sinyali ekleyin, 1 GB veri dolduğunda veri akışını ve süresini kaydedin, okuma ve yazma hesaplayın Hızlandırın, aynı anda sayacı temizleyin ve ardından hız bilgisini seri port modülü aracılığıyla ana bilgisayara gönderin. Sistem depolama modülünün okuma ve yazma hızı testi Şekil 9 ve Şekil 10'da gösterilmektedir.

Kamera görüntüsünü test görüntüsü olarak ayarlamak için Camera Link seri iletişim çipi aracılığıyla komutlar gönderin. Kamera test görüntüsünün gri değeri, aynı satırda kademeli olarak azalır ve bu, görüntü veri aktarım sürecini net bir şekilde yansıtabilir ve her pikselin bitişik verilerine göre görüntü aktarım hatasının oluşup oluşmadığını yargılayabilir. Hem ana bilgisayar tarafından geri okunan görüntü hem de gerçek zamanlı olarak görüntülenen görüntü iyi bir şekilde görüntülenir ve piksel hatası veya yanlış hizalama yoktur.

5. Sonuç

Bu makale, esas olarak sistem görüntü arayüz modülü, VGA sürücü devresi ve görüntü okuma modülü gibi donanım devrelerini içeren yüksek hızlı bir CMOS görüntü depolama ve gerçek zamanlı görüntüleme sistemi tasarlar.Aynı zamanda, görüntü görüntüleme modülü ve depolama modülü yazılımı da tasarlanmıştır. Okuma ve yazma hızı testi ve görüntü gösterme testinden sonra, sistemin gerçek zamanlı olarak 2048 × 2048 piksel çözünürlük ve 150 f / s kare hızı ile yüksek hızlı görüntüleri saklayıp görüntüleyebildiği, yüksek taşınabilirlik ve pratikliğe sahip olduğu görülmüştür. değer.

Referanslar

Han Shuai. Endüstriyel kameralara dayalı görüntü toplama ve oynatma sistemi üzerine araştırma. Taiyuan: Çin Kuzey Üniversitesi, 2015.

Zhang Huizhen, Zhou Yan, Wang Cheng. NAND Flash'a dayalı gömülü büyük ölçekli veri depolama mekanizması. Journal of Huazhong University of Science and Technology (Natural Science Edition), 2017, 45 (1): 46-51.

Xu Yonggang, Ren Guoqiang, Wu Qinzhang, vb. NAND Flash görüntü kayıt sistemi düşük seviyeli yazma kontrol teknolojisi Optoelektronik Mühendisliği, 2012, 39 (9): 138-144.

Ma Zhigang, Liu Wenyi, Ling Wei.PCI ve LVDS'ye dayalı yüksek hızlı veri depolama sistemi tasarımı.Elektronik Teknoloji Uygulaması, 2014, 40 (4): 80-83.

BARRERA E, RUIZ M, SANZ D, vd. F1exRI0, Camera Link ve EPICS'e dayalı gerçek zamanlı görüntü alma ve işleme sistemleri için test yatağı. Fusion Engineering and Design, 2014, 89 (5): 633-637.

Liu Wei. SATA arabirimli çift sabit disk kontrol teknolojisinin araştırılması ve uygulanması Taiyuan: Çin Kuzey Üniversitesi, 2016.

Wu Weixue. FPGA tabanlı görüntü toplama ve işleme sistemi tasarımı. Guangzhou: Güney Çin Teknoloji Üniversitesi, 2015.

Li Feifei, Liu Weining, Wang Yanhua Geliştirilmiş medyan filtre algoritması ve FPGA üzerinde hızlı uygulaması Bilgisayar Mühendisliği, 2009, 35 (14): 175-177.

-

- Cowan 2017 AI araştırma raporunu anlamak için bir makale: AI pazarı 2020'de 400 milyar ABD dolarına ulaşacak

-

- Hey, alkol için savaş, altın yengeçler ye, Dandan Meilin "Ace Agent 2" yi Çin Basın Konferansına getiriyor.

-

- Boğulmayı ve darbeyi önleyen hayat kurtaran okul çantaları, ilkokul anaokulları için "eksiksiz" tir | Titanyum hava patlaması modelleri