Yüksek hassasiyetli SAR analogdan dijitale dönüştürücüler için örtüşme önleyici filtreleme hususları

Nesnelerin İnterneti ve bulut bilişim hayatın bir parçası haline geldiğinde ve endüstri medyası, en ileri teknoloji ve optimize edilmiş tasarımın kullanılmasıyla heyecanlanmaya başladığında, eski elektronik bileşenler ilerlemelerini durdurmadılar. Bir örnek, artık saniyede bir mega örneği (MSPS) aşan bir hızda 32 bit çözünürlüğe ulaşabilen ve geleneksel metroloji karşılaştırma testlerini kolayca geçebilen analogdan dijitale dönüştürücüdür.

Bu yüksek hassasiyetli dönüştürücüler 16 bitten daha yüksek çözünürlükler görüntüleyebilir, karşılaştırılabilir statik ve dinamik özellikler sağlayabilir ve enstrümantasyon ve büyük ölçekli genel edinim sistemlerinde (test, ekipman sertifikasyonu), profesyonel sistemlerde (tıbbi uygulamalar ve spektroskopi dijital görüntüleme) vb. Özel alana ek olarak, birçok proses kontrol uygulamasına, programlanabilir kontrolörlere, büyük ölçekli motor kontrolüne, güç iletimi ve dağıtımına girmişlerdir. Şu anda, birkaç ADC mimarisi doğruluk açısından karşılaştırılabilir; farklı ihtiyaçlara göre, özel seçim analogdan dijitale dönüştürme, ardışık yaklaşım kaydı (SAR) ve - ilkesine bağlıdır. MSPS oranında, bu mimariler sırasıyla en yüksek 24 bit veya daha fazla çözünürlük 24 bit veya daha fazladır ve 32 bit çözünürlük birkaç yüz kSPS hızında desteklenir. Bu çözünürlük ve doğruluk seviyeleriyle karşılaşıldığında, bu dönüştürücüler tarafından sağlanan kullanışlı dinamik aralık, 100 dBFS (tam ölçek) sihirli bariyerini kolayca aşabilir.Kullanıcılar için asıl zorluk, sayısallaştırılacak sinyaller için analog koşullandırma devreleri tasarlamaktır ve İlgili kenar yumuşatma filtresinin tasarımının iki yönü vardır. Geçtiğimiz yirmi yılda, örnekleme hızı ve filtreleme teknolojisi büyük ölçüde geliştirildi.Artık performans ve karmaşıklık arasında daha iyi bir denge elde etmek için analog ve dijital filtreleri birleştirebiliriz.

Şekil 1, veri toplama sistemleri için uygun bu tür bölümün tipik bir örneğini göstermektedir. Diferansiyel veya diferansiyel olmayan sinyali (amplifikasyon, ölçekleme, adaptasyon ve seviye dönüştürme, vb.) Ayarladıktan sonra, ikincisi, Nyquist kriterini karşılamak için sayısallaştırmadan önce filtrelenir. ADC'nin yüksek hızda örnekleme hızına göre, edinim sisteminin özelliklerini karşılamak için ek dijital filtreleme kullanılır.

Ultra geniş giriş dinamik aralığı için artan talep nedeniyle, yukarıda bahsedilen uygulamaların çoğu en gelişmiş yüksek çözünürlüklü ADC'leri kullanır. Dinamik aralık arttıkça, sistem performansının iyileşmesi beklenir, analog düzenleme zinciri azalır, tıkanıklık, enerji tüketimi ve hatta malzeme maliyetleri azalır.

Yüksek hızda örnekleme ve faydaları

Ultra hızlı yüksek çözünürlüklü analogdan dijitale kodlayıcıların ortaya çıkmasından önce, dinamik aralık sorunu genellikle aşağıdaki yöntemlerle çözüldü: hızlı programlanabilir kazanç yükselticileri, daha hızlı karşılaştırıcılar ve / veya birkaç ADC'yi paralel hale getirme ve son olarak uygun dijital işleme modüllerini ekleme, Güçlü sinyallerin sayısallaştırılmasını gerçekleştirmek için gürültü seviyesine yakın küçük sinyalleri ayırt edin. Bu eski ve şimdi modası geçmiş mimarilerde, bunu yapmak, geliştirilmesi zor ve doğrusallık, bant genişliği ve örnekleme frekansı açısından sınırlı karmaşık devreler getirecektir. Günümüzün alternatifi, yüksek hızda örnekleme amacına ulaşmak için daha ekonomik bir modern ADC'nin yüksek örnekleme oranını kullanmaktır. Sinyalin, Nyquist teoreminin gerektirdiği minimumdan daha yüksek bir FSE oranında örneklenmesiyle, kazanç işlemi, kodlayıcının sinyal-gürültü oranının işlenmesi ve artırılmasıyla gerçekleştirilebilir, böylece etkili bitlerin sayısı arttırılabilir. Aslında, niceleme gürültüsü ve termal gürültü, Nyquist bandı ve ötesine eşit olarak dağılan beyaz gürültüye asimile edilir. Yüksek hızda örneklemeden sonra, kullanışlı frekans bandı filtreleme ile sınırlandırılır ve kesinlikle gerekli minimum örnekleme hızında (veya 2 × BW) ve Şekil 2'de gösterildiği gibi, frekans bandı her bir oktav azaltıldığında gürültü enerjisi 3 dB azalacaktır. Başka bir deyişle, 4'lük bir yüksek hızda örnekleme faktörü, teorik olarak sinyal-gürültü oranını 6dB artıran en ideal olanıdır; başka bir deyişle, Denklem 1'de gösterildiği gibi bir bit ekler:

Şekil 1. Tipik ölçüm sinyal zinciri.

Şekil 2. Bir dijital decimation filtresi ekleyerek spektral gürültü yoğunluğunun karşılaştırılması.

Kısacası, yüksek hızda örneklemenin iki avantajı vardır, biri sinyal-gürültü oranını iyileştirebilmesi, diğeri ise ADC'den önce bulunan örtüşme önleme analog filtresinin gereksinimlerini rahatlatabilmesidir.

Kenar yumuşatma filtreleri: bölüm ikilemi

İdeal olarak, ADC ile ilgili filtreler, özellikle spektrum örtüşme problemini çözmekten sorumlu olanlar, doğruluklarına kıyasla olabildiğince düz bir genlik yanıt bant genişliğine sahip olmalıdır ve bant dışı zayıflamaları da dinamik aralıklarını karşılamalıdır. İddia. Geçiş bölgesi genellikle mümkün olduğu kadar dik olmalıdır. Bu nedenle, bu örtüşme önleyici düşük geçişli filtrelerin belirli özellikleri vardır ve parazit görüntüleri, gürültüyü ve diğer sahte sesleri ortadan kaldırabilmelidir. Uygulamaya bağlı olarak, faz cevabına özel dikkat gösterilmeli ve aşırı faz kaymaları telafi edilmelidir. Temel öneriler olarak kabul edilen birçok öneri olmasına rağmen, bu önerileri belirtilen 24 bit veya 32 bit dönüştürücülerin gereksinimleriyle birleştirmek istiyorsanız ve bu dönüştürücülerin integral doğrusal olmama hatası yalnızca birkaç LSB ve diğer Benzer statik ve dinamik parametreler, bazı önerilerin uygulanması son derece zordur.

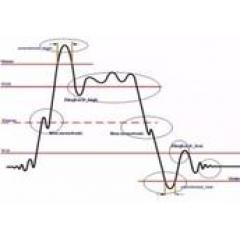

Daha önce belirtildiği gibi, yüksek hızda örnekleme burada çok önemlidir çünkü sadece sinyal-gürültü oranını iyileştirmez, aynı zamanda analog örtüşme önleme filtre özellikleri ve kesme frekansı için gereksinimleri de gevşetir. Şekil 3'te gösterildiği gibi, yüksek hızda örnekleme dağılımı, -3 dB koşulu altında kesme frekansı ile durdurma bandının başlangıcı arasındaki geçiş bandındadır.

Şekil 3. Yüksek hızda örnekleme dağılımı, -3 dB koşulu altında kesme frekansı ile durdurma bandının başlangıcı arasındaki geçiş bandıdır.

En son teknoloji, son yıllarda önemli ölçüde iyileştirilen yüksek hassasiyetli SAR ADC dönüşüm oranlarını mümkün kılmıştır.Şu anda, 18 bit çözünürlükle, bu dönüşüm oranları 1 MSPS ile 15 MSPS arasındadır. Buna karşılık, aynı çözünürlüğe sahip geniş bantlı - ADC'lerin oranı neredeyse bir kat daha düşüktür, göze çarpan gecikme sorunları vardır ve geçiş bandı dalgalanması, veri toplama sistemlerinde, diğer ölçüm cihazlarında vb. Kullanılamayacak kadar yüksektir. uygulama. Temel olarak, genel ölçüm doğruluğu, statik (dc) ve dinamik (ac) parametrelerle ilgili olan ikincisinin özelliklerini belirler.Bu nedenle, bu sistemlerdeki dönüştürücüler ve bunlara eşlik eden analog koşullandırma devreleri, spesifikasyonlardaki en üst gereksinimleri karşılamalıdır. .

Bu özellikler arasında ofset, kazanç ve ilgili kayma hataları, integral doğrusal olmama (INL) ve diferansiyel (DNL) hataları ile sinyal-gürültü oranı (SNR), harmonik bozulma ve yapay ses (sahte dinamik aralık yok) gibi ortak özellikler bulunur. (SFDR)). SAR ADC, bu parametrelerin bazılarında açık rekabet avantajına (INL) ve aynı zamanda geçici yanıt, analog giriş aşırı yükü ve sıfır gecikmeye sahiptir; bu, çoklu giriş sistemlerinin veya edinme tetikleyicilerinin tek modda çalışması için bir garanti sağlar.

Aksine, LTC2512 ve LTC2500-32 haricinde, çoğu SAR ADC'si dijital filtreler içermez, bu nedenle operasyonları bazı kaçınılmaz dijital düşük geçişli filtreleme tarafından engellenmez veya kısıtlanmaz, aksi takdirde hesaplama doğruluğu, bant geçiş dalgalanması olacaktır. , Zayıflatma durdurma bandı bastırma, yayılma süresi ve güç tüketimi dengelenir. Çoğu durumda, kullanıcılar bu - dönüştürücülerin dahili filtre katsayısı değerlerini kontrol edemezler ve bununla idare etmek zorundadırlar.

LTC2378-20: Piyasadaki ilk 20 bit SAR ADC

Performans yarışmasında, 2014 yılında, Doğrusal Teknoloji (şimdi ADI'nin bir parçası), müşterilere rekabeti yenen 20 bit çözünürlük ve gerçek doğrusallığa sahip ilk ardışık yaklaşım ADC'yi tanıttı. Ben hazırlıksız yakalandım. LTC2378-20, MSPS'ye yakın diğer tüm rakip ürünlerde hala kendi avantajlarını koruyan mükemmel bir dönüştürücüdür.

LTC2378'in eski bir arkadaşı olan AD4020, 1,8 MSPS'de 10 V tepeden tepeye diferansiyel sinyalleri sayısallaştırabilen ADI'nin ilk 20-bit SAR ADC'sidir. Düşük gürültü, düşük güç tüketimi ve LTC2378'in tüm özelliklerini bir araya getirir: dinamik sıkıştırma, kenetleme devresi, şarj aktarımı telafisi ve düşük güçlü hassas amplifikatörlerin (yüksek empedans modu) vb. Kullanımını destekler. 1,8 V güç kaynağı kullanıldığında, güç tüketimi 1,8 MSPS'de yalnızca 15 mW'dir. 350 ns'lik rekor dönüştürme süresi, edinim süresini uzatmayı veya verileri okumayı kolaylaştırır. AD40xx ailesinin diğer 16-bit ila 18-bit üyeleriyle aynı olan 10-pin MSOP veya 10-pin QFN olarak paketlenmiştir. 40 ° C ila 125 ° C sıcaklık aralığında, özellikleri ve çalışması tamamen garanti edilmektedir.

LTC2378-20 ve AD4020'nin örnekleme oranları sırasıyla 1 MSPS ve 1,8 MSPS'dir, bu da özellikle ses frekans bantlarında veya daha yüksek frekans bantlarında yüksek hızda örnekleme için önemli olanaklar sunar. Bu nedenle, harici bir FPGA veya DSP'ye özelleştirilmiş bir decimation filtresi kurulmalıdır. Daha önce bahsedildiği gibi, gerekirse gecikmesini en aza indirmek için ikincisi atlanabilir. Bu birincil örnekleme oranı değerlerine dayanarak, 0 kHz ila 25 kHz frekans bandı dikkate alındığında, karşılık gelen yüksek hızda örnekleme faktörü yaklaşık 16 veya 32'dir ve işleme kazancı 12 dB ila 18 dB'dir.Aynı zamanda, Nyquist teoremini sıkı bir şekilde izleyerek rutin işlemleri basitleştirir Koşullar altında kenar yumuşatma alçak geçiren filtre.

ADC'den DSP'ye bağlantı: her şey seri

Son yıllarda, yarı iletken endüstrisi ve tasarımcı çevreleri, bileşenlerin boyutunu açıkça küçültme, yuva pimlerini gerçekten ince yapma ve ayrıca SPI veriyoluna, senkron seri porta vb. Bağlanması gereken neredeyse tüm seri dijital girişleri veya çıkışları ayarlama eğiliminde olmuştur. Sorun şu ki, bu dönüştürücüler ADC'nin çeşitli işlevsel seçeneklerini örneklemek ve kontrol etmek için bir seri arayüz bırakmıyor. Spesifikasyonlarına göre, bu seri arayüzler SPI veya DSP seri portları ile uyumludur, ancak durum böyle değildir. En iyi ihtimalle, saat sinyalinin ritmini ayarlamaktan sorumlu, cihazdan veri çıkarmak veya yapılandırma sırasında verileri enjekte etmek için kullanılan kaydırma yazmacını gizlerler. Tüm bu SAR ADC'ler gibi, LTC2378-20 ve AD4020, nominal örnekleme hızında 20 bitlik birimler halinde verileri kurtarmak için frekansta seri saat (SCK) gerektirir. Veri okuma aşaması kesinlikle edinme süresi (yaklaşık 300 ns) ile sınırlı olduğundan, dönüştürme süresi boyunca, harici erişim sırasındaki dijital etkinlik tamamen sessiz hale getirilmeli ve tahsis edilen süre içinde 1 MSPS örnekleme oranı kullanılmalıdır Tüm bitleri örneklemeden kurtarmak için saat frekansı 60MHz'in üzerinde olmalıdır. Bu tür bir saat frekansı veya alıcı tarafında uygulanacak olan zaman belirtimi üretilecek olsun, bu ADC'den veri toplamaktan sorumlu kontrolör üzerindeki arayüz için katı bir sınırlamadır. LTC2378-20, minimum 64 MHz'lik bir SCK sinyal frekansı gerektirir; bu, Blackfin işlemci ailesinin bazı üyeleri dışında, maksimum frekansı 50 MHz'nin biraz üzerinde olan senkronize seri bağlantı noktası (SPORT) ile donatılmış herhangi bir genel amaçlı mikro denetleyiciye veya DSP'ye bağlanamayacağı anlamına gelir. , ADSP-BF533 ve ADSP-BF561 gibi hız 90 Mbps'ye ulaşabilir. Bu nedenle, bazı insanlar düşük titreşimli saat oluşturma devresi ile donatılmış büyük bir CPLD veya FPGA kullanma ihtiyacından endişe duyuyor. Seri çıkışlı SAR ADC'lerin çoğu dijital arabirimi, Şekil 4'te gösterildiği gibi, aşağı yukarı aynı zamanlama ve mantık sinyal modellerine sahiptir. SDI konfigürasyon girişi için, kademeli moda ek olarak, çok daha düşük bir frekans gereksinimi de vardır. ADC örnekleme döneminin eşdeğer tam döngü süresi (2)

Bu nedenle, maksimum örnekleme sıklığı tanımlanmıştır ve bileşimi şöyledir:

(3)

Çıkış verilerinin okuma hızı tarafından kendisi ayarlanır, burada,

(4) tsck = 1 / Fsck

Şekil 4. AD4020'nin zamanlama diyagramı.

Neyse ki, AD4020, 325 ns'lik ultra kısa bir dönüştürme süresine, 1 MSPS'lik bir örnekleme hızına ve 675 ns'lik bir örnekleme süresine sahiptir.Buna dayanarak, seri veri okuma frekansı 33 MHz'den düşüktür ve DSP seri bağlantı noktasıyla (SHARC? ADSP-21479) eşdeğerdir ve güç tüketimi de çok düşüktür.

Ultra düşük güçlü çok kanallı bir sistem

İşletme modu seçiminde enerji tüketimi, doğruluk ve esneklik nedenleriyle ve ayrıca ticari nedenlerle, bu uygulamalarda FPGA tabanlı çözümler dikkate alınamaz. Bu 20 bitlik ADC'lerden gelen seri çıktıyı işlemek ve optimum ondalık ayırma filtresini uygulamak için yalnızca DSP kayan noktalı işlemciler kullanılabilir.

Günümüzde, çok sayıda kanaldan aynı anda örnekleme yapabilen birçok veri toplama sistemi vardır. Bu, birçok ADC'nin paralel olarak çalışmasına ve aynı denetleyici tarafından kontrol edilmesine neden olur; bu, aynı zamanda verileri toplamaktan ve sonraki analizler için bellekte depolamaktan da sorumludur.

SHARC ADSP-21479 veya hızlı versiyonu ADSP-21469 ve ADSP-21489 (450 MHz saat frekansı) gibi yüksek performanslı SAR ADC'ler ile inşa edilen sistem sadece pratik ve uygulanabilir değil, aynı zamanda performans, geliştirme süresi, enerji tüketimi ve kompaktlık açısından da. Olağanüstü. Bu işlemciler, senkron seri arayüzler, farklı saat sinyallerinin oluşturulması ve tetikleme dönüşümü dahil olmak üzere 8 analogdan dijitale kanalı desteklemek için gereken tüm işlevlere ve çevre birimlerine sahiptir. Tüm SHARC işlemcileri arasında ADSP-21479, düşük sızıntılı 65nm CMOS işlemiyle üretilen tek 32/40 bit kayan noktalı DSP'dir.Avantajı, sızıntıyı veya durgun akımı büyük ölçüde azaltabilmesi ve bağlantı sıcaklığının neredeyse üssel olmasıdır. Seviye gelişimi. İşlemci ve çevre birimlerinin frekansının ve faaliyetinin bir fonksiyonu olan dinamik akım, standart veya hızlı CMOS işlemlerinde üretilen işlemcilerinkinden de daha düşüktür. Dezavantajı, geleneksel versiyonla karşılaştırıldığında, maksimum CPU frekansının yaklaşık% 30 -% 40 oranında azaltılmış olması, ancak bu tür uygulamaların ihtiyaçlarını karşılamak için yine de yeterli olmasıdır.

ADSP-21479, senkron olarak çalışan 8 harici seri vericiden eşzamanlı olarak sinyal akışlarını, saat ve senkronizasyon sinyallerini alabilen Seri Giriş Bağlantı Noktası (SIP) adı verilen özel bir modül dahil olmak üzere çeşitli çevre birimleriyle donatılmıştır. Aslında, AD4020'ye benzer 8 ADC doğrudan bu arayüze bağlanabilir, böylece işlemciye bağlanabilir. Şekil 5'te gösterildiği gibi, 8 kanalın kendi IDP_SCK saati, IDP_FS senkronizasyonu ve IDP_DAT giriş sinyalleri vardır.Seri durumdan çıkarıldıklarında, verileri otomatik olarak 32 bitlik, 8 kelimelik FIFO belleğine çoklanacak ve ardından 64 bit DMA verilerini iletecektir. Paket veya CPU tarafından gerçekleştirilen okuma işlemi, SHARC dahili RAM'ine aktarılır. DMA aktarım işleminde, SIP, otomatik ping-pong modunda çalışan bir çift indeksli DMA kanalı tarafından sunulur. Ek olarak, ADSP-21479 ayrıca dahili veya harici kaynaklardan (TCXO) bağımsız saat ve senkronizasyon sinyal çiftleri oluşturabilen dört hassas saat üreteci (düşük titreşim için, PCG olarak kısaltılmıştır) ile donatılmıştır. Bu uyarıların frekansı, periyodu, darbe genişliği ve fazı, 20 bitlik bir dahili frekans bölücü programlanarak elde edilebilir. Her bir PCGx üretim birimi, bir çift AD4020 dönüştürücüsü tarafından paylaşılan bir çift CLK / FS sinyali sağlar, ancak dönüşüm aşamasında saatin sessize alınması gerekir, bu nedenle SCK saatini oluşturmak için IDP_FS sinyalini ve IDP_SCK sinyalini birleştirmek için bir mantık geçidi gerekir. Şekil 5'teki zamanlama diyagramı, tconv dönüşüm süresi geçtikten sonra, örnekleme frekansında 1 MSPS'nin sihirli bariyerini korumak için mevcut örnekten 33.3 MHz hızında 20 bitlik verinin mümkün olduğunca çabuk okunması gerektiğini göstermektedir. Yaklaşık 600 ns sonra, veriler SIP tamponlarından birine aktarılır Bu zamanda, IDP_FS veya CNV sinyali, AD4020'nin yeni bir dönüştürme işlemi gerçekleştirmesini sağlamak için yeni bir dönüştürme döngüsünü başlatmak için kullanılabilir. İkincisinin maksimum dönüştürme süresi, CNV sinyalinin darbe genişliğine, yani 12 IDP_SCK saat döngüsüne veya 360 ns'ye karşılık gelen 325 ns'ye ulaşır. Kısaca, Şekil 5'teki zamanlama diyagramında gösterildiği gibi, tam bir tarama döngüsü 32 IDP_SCK sinyal döngüsü gerektirir ve toplam süre 960 ns'dir, bu nedenle maksimum örnekleme hızı 1.040 MSPS'dir.

Benzer şekilde, ADC LTC2378-20, ADSP-21489 ile ilişkilendirilebilir çünkü 50 MHz'e kadar çevresel saat frekanslarında çalışabilir.Bu durumda, örnekleme hızı Tablo 1'de gösterildiği gibi 900 kSPS'dir. Ne yazık ki, ikincisinin hareketsiz besleme akımı (Iddint) veya kaçak akımı dinamik akımdan çok daha yüksektir, bu da bu konfigürasyonun toplam güç tüketimini kabul edilemez bir seviyeye kadar mevcut gücü aşar.

Decimation filtreleme

Bu dönüştürücülerin aşırı örnekleme modunda kullanıldığını varsayarsak, gerekli hesaplama gücü ve güç tüketimi açısından DSP üzerindeki etkiyi en aza indirmek için yukarıdaki gereksinimleri karşılayabilen ve hedef frekans bandı için özelleştirilmiş bir dekimasyon filtresi sağlamak gerekir. Şu anda, örnekleme oranını değiştirmek için kullanılan program, bir interpolatör ve bir dijital desimator ile uygulanabilen standart bir dijital sinyal işleme işlemi haline gelmiştir. Faz yanıtının doğrusallığı dikkate alındığında, düşük geçişli dekimasyon filtresi, sonlu bir dürtü yanıtı (FIR) topolojisi kullanır ve verimlilik gereksinimlerine göre farklı topolojiler kullanılabilir:

Decimation için özel doğrudan veya optimize edilmiş FIR filtresi

Kademeli çoklu oranlı FIR filtresi (1/2 frekans bandı)

Çok fazlı FIR filtresi

Hem FIR hem de IIR tipi çok fazlı filtreler, decimation veya interpolasyon filtrelerinin en etkili uygulamalarından biridir. Bununla birlikte, geleneksel dijital işleme şemaları, kesmeden önce filtreleme gerektirir. Bu varsayım altında, 1 / M dekimasyon filtresi, düşük geçişli bir filtreden ve ardından örnekleme frekansı bozulmasından oluşur (Şekil 6a). Spektrum örtüşmesini önlemek için sinyali önceden filtreleyin ve ardından örnekleri periyodik olarak M-1 oranında ortadan kaldırın. Bununla birlikte, bu dekimasyon filtrelerinin geleneksel FIR veya diğer yapılarla doğrudan uygulanması, kaynakları israf etme sorununa sahiptir, çünkü reddedilen numuneler onlarca veya hatta yüzlerce kümülatif çarpmanın (MAC) sonucudur. Birkaç filtre kümesine ayrıştırılmış bir çok fazlı filtre veya dekimasyon için optimize edilmiş bir filtre kullanmak, belirli özelliklere (Şekil 6b'de gösterildiği gibi) dayalı olarak verimli bir filtre oluşturabilir.

FIR filtreleme için özel bir SIMD mimarisi ve donanım hızlandırıcı ve dijital sinyal işleme için optimize edilmiş bir komut seti ile SHARC ADSP-21479, özellikle bu tip filtreleri uygulamak için uygundur. Her SHARC işlem birimi, 266 MHz CPU frekansında saniyede 533 sabit nokta veya kayan nokta MAC hesaplaması gerçekleştirebilen 32/40 bit çarpan toplayıcıya sahiptir. Bununla birlikte, önemli gecikmelerin olduğu bazı uygulamalar için (oda eşitleme veya ses efektleri), çekirdeği FIR, IIR ve FFT filtreleme gibi yoğun ve sürekli çarpma işlemlerinden kurtarmak için bilgi işlem gücünü artırmak ve bunları gerçekleştirmek için özel donanım hızlandırıcıları kullanmak gerekir. Operasyon. Bu şekilde kullanıcılar, karmaşık koleksiyonları gerçekleştirmek için karmaşık algoritmalar gerektiren hesaplamalar için CPU'yu kullanmaya tamamen kendi başlarına karar verebilirler. FIR filtresi özel hızlandırıcı, verileri ve katsayıları depolamak için özel bir yerel belleğe sahiptir ve aşağıdaki özelliklere sahiptir:

Şekil 5. 8 adet 20-bit 1 MSPS SAR ADC'yi seriyi kaldırma yoluyla SHARC DSP'ye bağlayın; DMA verileri DSP içinde RA'ya aktarılır

Şekiller 6a ve 6b Çok fazlı bir şema kullanan geleneksel ondimasyon filtreleri ve decimation filtreleri.

IEEE-754 sabit noktalı veya kayan noktalı 32 bit aritmetik formatı destekler

Paralel olarak çalışan dört kümülatif çarpma birimi vardır

Tek oranlı ve çok oranlı işleme modlarını destekleyin (ondalık veya enterpolasyon)

Basit bir yineleme, toplam 1024 katsayıya kadar 32 FIR filtresini işleyebilir.ADSP-21479'un hızlandırıcısının saat hızı, CPU CCLK saat frekansının yarısı olan, yani 133 MHz olan sistem saatinin veya PCLK çevre biriminin hızıyla aynıdır. Buna dayanarak, toplam bilgi işlem gücü 533 MAC / sn'dir. Hızlandırıcı, talimatların yürütülmesini gerektirmez; işlemleri, belirli kayıtların yapılandırmasıyla belirlenir ve verileri dahili ve / veya harici bellekler arasında taşımak için tamamen DMA aktarımlarına dayanır.

Açıktır ki, hızlandırıcı, çok oranlı filtre uygulamasını (ara değerleme veya ondalık ayırma) optimal bir şekilde gerçekleştirebilir. Basit desimasyon filtresi, M giriş sinyalleri için yalnızca bir çıkış sonucu sağladığından, çıkış hızı, giriş hızından 1 / M kat daha düşüktür. Bu optimize edilmiş FIR filtresinin uygulanması, karmaşık bir çok fazlı filtre bankası kullanmaz, çünkü ikincisi, uygulanması çok karmaşık olan çok sayıda bellek işaretçisi gerektirir; tam tersine, çözüm sadece M-1 örneklerinin çıktısını beklemeye alır. Bu hesaplamaları yapmaktan kaçının ve yalnızca yararlı örnekler üreten verileri hesaplayın. Bu, israfı ortadan kaldırır ve sonuç olarak, işlem sayısı M-1 oranıyla azaltılır - bu örnekte 15 - böylece CPU döngülerini büyük ölçüde kurtarır. Bununla birlikte, böyle bir ondalık oran ve bu kadar kısa bir hesaplama penceresi altında, hızlandırıcı iki hesaplama birimine sahip bir çekirdek kadar etkili değildir ve DMA kanalı, bir filtreden diğerine sinyal iletimi sırasında yeniden programlanır. Olumsuz etkilere neden olur. SISD modunda bir bilgi işlem birimi ile uygulanırsa, bu tür filtrenin CCLK döngüleri açısından maliyeti şu şekilde ifade edilebilir:

FIR_Decim_Cycles = N + 2 × M + 19 (5)

N, filtrenin katsayılarının sayısıdır ve M, ondalık oranıdır.

Bu dekimasyon filtresinin bir yinelemesinin uygulama maliyeti, 0 kHz ila 24 kHz frekans aralığında FIR filtresi koşulunda (kaynaktan montajcıya 21k) yaklaşık 150 döngüdür, dalgalanma özelliği ± 0,00001 dB'dir, 62,500 SPS'de örnekleme Hızla, bant dışı zayıflama -130 dB'dir. Bu filtrenin 97 katsayısı vardır (32-bit FP IEEE-754 formatında nicelenmiştir) ve yanıtı MATLAB® Filter Designer ile yapılan Şekil 7'de gösterilmektedir. Bağlı SIP veya ADC'nin her bir aktif kanalı için yanıt, örnekleme frekansında DMA kesinti örneğinde tekrarlanır.

Şekil 7. Decimation filtresinin filtre yanıtı.

Gerçek zamanlı ve DSP yükleri için, filtreleme işlemi, 9,375,053 CCLK döngüsünü temsil eden 62,5 kSPS'lik bir frekansta tekrarlanırken, 8 ADC dönüşüm kanalının tekrarlama frekansı 8 kattan biraz daha fazladır, çünkü her filtrenin bellek işaretçisi değeri SHARC'ta saklanır. Veri adresi oluşturucusunda hızlı bir şekilde kaydedebilir ve geri yükleyebilirsiniz. Bu, SISD modunda bir SHARC DSP için saniyede 80 milyon yürütme döngüsüne (veya 80 MIPS) eşdeğerdir SIMD modunda, iki işleme birimi paralel çalıştığı için bu değerin yarısıdır. Yukarıda bahsedilen iki modda, bu 8 desimator FIR filtresi ADSP-21479'u sırasıyla% 30 ve% 15 oranlarında ve 266 MHz saat frekansında işgal eder.

Güç tüketimi

Dönüştürücünün güç tüketimi, teknik özelliklerinden kolayca ve doğru bir şekilde hesaplanabilse de, işlemcinin güç tüketimi için hesaplama formülü birden çok parametre içerdiğinden işlemcinin güç tüketimi çok daha zordur ve gerçek zamanlı koşullar ve çalışma modları değişiklik gösterir. Bunda büyük etkisi var. Burada ayrıntılı bir açıklama olmamasına rağmen, okuyucular ADSP-214xx ve ADSP-21479 işlemcilerinin her bir bileşeninin güç tüketimi tahminiyle ilgili talimatları, işlevsel modülün etkinliğini, durgun akım bağlantı sıcaklığını ve güç kaynağını dikkate alan ilgili teknik notlarda kolayca bulabilirler. Gerilim değeri, kullanılan giriş ve çıkış pinlerinin sayısı, çeşitli harici frekanslar ve kapasitif yükler. Şekil 5'teki fonksiyonel açıklamaya göre, DSP ve ADC'nin çeşitli kombinasyonları için, bu tür bir dekimasyon filtreleme uygulamasında DSP'nin aktivitesine karşılık gelen güç tüketimi verilmiştir. Dört veya sekiz ADC'li bu ilgili DSP varyantları için, güç tüketiminin fonksiyonel kapasiteye, giriş / çıkışların sayısına, işlemcinin hesaplama gücüne ve ADC'nin genel performansına göre belirlenmesi gerekir. Ultra düşük hareketsiz akımla, çekirdek olarak ADSP-21479 ve sekiz SAR ADC kümesiyle oluşturulan çözüm, yalnızca en düşük güç tüketimine sahip çözüm olmakla kalmaz, aynı zamanda çok sayıda filtre algoritması seçeneği ve diğer dijital işlevlerin yanı sıra genel performans sağlar. Muhteşem.

Bu çok kanallı veri toplama sistemi (DAQ) örneği ayrıca FPGA'ların dijital sinyal işleme görevlerini uygulamak için gerekli olmadığını kanıtlar Kayan noktalı DSP, özellikle güç tüketimi oldukça söz konusu olduğunda, yüksek hassasiyetli SAR ADC'ler için daha uygundur.

-

- Yüzyıllardır miras kalan özel Shandong çok tahıllı kreplerin tarifi ve üretimi! Ayda 8.000 yuan kazanmayı öğrenin

-

- Popovich'in vizyonu gerçekten zehirli! Eski Rockets ile karşılaştırıldığında, eski Mahmuzların hepsi "hurda"

-

- Hayal gücü her şeyi değiştirir: termodinamiğin üç yasası, E = mc² ve yıldızlararası seyahatin yolu vb.