SABL tabanlı savunma diferansiyel güç analizi kaydırma yazmacının tasarımı

Qian Haoyu, Wang Pengjun, Ding Dailu, Zhang Yuejun

(Devreler ve Sistemler Enstitüsü, Ningbo Üniversitesi, Ningbo, Zhejiang 315211)

Geleneksel kaydıran yazmaç prensibinin ve Duyu Yükseltici Tabanlı Mantık (SABL) devresinin araştırılmasıyla, diferansiyel güç analizine karşı savunma yapabilen bir kaydırma yazmacı tasarım şeması önerilmiştir. Bu şema, önce SABL devresine dayalı bir temizleme ve ayarlama D flip-flopu tasarlamak için ana-bağımlı tetikleme modunu benimser; daha sonra çok bitli bir kaydırma yazmaç devresini uygulamak için flip-flop ve SABL mantık geçidini kullanır. Spectre simülasyon doğrulaması, tasarlanan kaydırma yazmacının mantık fonksiyonunun doğru olduğunu gösterir.Çeşitli PVT kombinasyonları altında, NED% 2,66'dan düşük ve NSD% 0,63'ten düşüktür, bu da diferansiyel güç analizi performansına karşı önemli bir savunmaya sahiptir.

SABL; savunma diferansiyel güç analizi; kaydırma yazmacı; bilgi güvenliği

Çin Kütüphanesi Sınıflandırma Numarası: TN918.4

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.2017.02.008

Çince alıntı biçimi: Qian Haoyu, Wang Pengjun, Ding Dailu, ve diğerleri.SABL'ye dayalı savunma diferansiyel güç analizi için kaydırma yazmacının tasarımı.Elektronik Teknoloji Uygulaması, 2017, 43 (2): 40-43.

İngilizce alıntı biçimi: Qian Haoyu, Wang Pengjun, Ding Dailu ve diğerleri.SABL'ye dayalı dirençli diferansiyel güç analizi kaydırma yazmacının tasarımı.Elektronik Tekniğin Uygulanması, 2017, 43 (2): 40-43.

0 Önsöz

Bilgi güvenliği teknolojisinin gelişmesiyle birlikte, ana bileşenleri kriptografik çiplere sahip taşınabilir cihazlar yaygın bir şekilde kullanılmaktadır. Bununla birlikte, kripto çip, enerji tüketimi, elektromanyetik radyasyon ve çalışma süresi gibi şifreleme algoritmasını çalıştırırken işlenen verilerin kendisiyle ilgili çeşitli fiziksel bilgileri sızdıracaktır. Bu fiziksel bilgiler, bir saldırgan tarafından anahtarı çalmak için şifreleme çipinde bir Yan Kanal Saldırısı (SCA) gerçekleştirmek için kullanılabilir. Diferansiyel Güç Analizi (DPA), kripto yongalarının etkinliğini büyük ölçüde azaltan yan kanal saldırılarında basit ve verimli bir saldırı yöntemidir. Son yıllarda bilim adamları, çift voltajlı tek raylı dinamik mantık (Çift voltajlı Tek raylı Dinamik Mantık, DSDL), maske tabanlı çift raylı ön şarj mantığı (Maskeli Çift Raylı Ön Şarj Mantığı) gibi DPA saldırılarına karşı çeşitli savunma önerdiler. , MDPL) ve Sense Amplifier Based Logic (SABL) vb. Simetrik bir aşağı çekme ağının olmaması nedeniyle, DSDL değerlendirme hızı yavaştır; literatür, giriş sinyalleri arasında bir gecikme farkı olduğunda, MDPL'nin DPA saldırılarına karşı savunmada zayıf performansa sahip olduğuna işaret etmektedir. SABL, DPA saldırılarına karşı savunmada hızlı çalışma hızı ve iyi performans özelliklerine sahip olduğu için, DPA saldırılarına karşı savunma için giderek yaygın bir yöntem haline geldi.

Kaydırma kayıtları, mantıksal işlemler gerçekleştiren veya bilgi depolayan bileşenlerdir ve dijital şifreleme sistemlerinde yaygın olarak kullanılır. Araştırmalar, vardiya yazmacının şifreleme sisteminde önemli enerji tüketen bileşenlerden biri olduğunu göstermiştir.Aynı zamanda, verileri yalnızca saat kenarı geldiğinde işlediği için, diğer bileşenlere kıyasla, çalışma zamanlaması değişiklikleri nispeten sabittir ve tanımlanması kolaydır.Bu nedenle, diferansiyel güç tüketiminde Analizde, enerji tüketimi genellikle geleneksel kripto çipini kırmak için bir analiz noktası olarak kullanılır. Bunun ışığında, bu makale SABL devresinin özelliklerini her saat döngüsünde sabit bir güç tüketimi değeri ile birleştirir ve DPA saldırılarına karşı savunma yapabilen bir kaydırma yazmacı tasarımı önerir. İlk olarak, statik tamamlayıcı CMOS devresinin güç tüketimi özelliklerini, SABL devresinin çalışma prensibini ve sabit güç tüketimi özelliklerini analiz edin; ardından sıfırlamayı tasarlayın ve SABL devresinin özelliklerine göre D flip-flopunu ayarlayın ve ardından çok bitli bir kaydırmalı yazmaç devresi oluşturmak için SABL mantık geçidini ve D flip-flopunu kullanın Son olarak, TSMC 65 nm CMOS süreci kapsamında, tasarlanan kaydıran yazmaç mantık fonksiyonunun doğruluğu ve DPA saldırılarına karşı savunma performansı Spectre aracı simülasyonu ile doğrulanmaktadır.

1 SABL devresi

Şu anda çoğu dijital entegre devre tasarımı, statik tamamlayıcı CMOS mantık hücreleri tarafından gerçekleştirilmektedir.Toplam güç tüketimi, denklem (1) 'de gösterildiği gibi kaçak güç Pleak, dinamik güç Pdyn ve kısa devre gücü Pshort'tan oluşur:

Bunlar arasında Ptotal CMOS mantığının toplam güç tüketimi, Pleak kaçak akımın neden olduğu güç tüketimi, Pdyn yük kondansatörünün şarj edilip boşaltılmasından kaynaklanan güç tüketimidir ve Pshort ise devre açıldığı andaki kısa devre akımının neden olduğu güç tüketimidir. Genellikle Pleak ve Pshort çok küçüktür ve CMOS mantık hücrelerinin güç tüketimi üzerinde en büyük etkiye Pdyn sahiptir. Literatürden, güç kaynağının yük kapasitansını yalnızca çıkış sinyali 0 1 geçişi olduğunda şarj edeceği görülebilir. 0 0, 1 0 ve 1 1 şeklindeki üç geçişte devre dinamik güç üretmez. Tüketim. Bu nedenle, statik tamamlayıcı CMOS mantığının güç tüketimi, işlediği verilerle ilgilidir ve bu, saldırganların geleneksel kriptografik cihazlara DPA saldırıları başlatması için bir dönüm noktası haline gelmiştir.

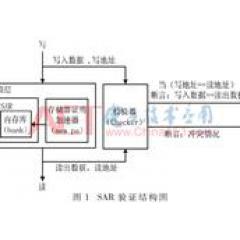

Statik tamamlayıcı CMOS mantığının eksiklikleri göz önüne alındığında, Kris Tiri ilk olarak 2002'de sabit güç tüketimine sahip SABL devresini önerdi. Bir ön şarj tüpü, bir diferansiyel ağ, bir çapraz bağlanmış invertör, normal olarak açık bir tüp ve bir değerlendirme tüpünden oluşur.Diferansiyel ağ, mantık işlevine göre diferansiyel aşağı açılır ağ (Diferansiyel Aşağı Çekme Ağı, DPDN) ve diferansiyel açılır ağa bölünmüştür. Ağ (Diferansiyel Çekme Ağı, DPUN). DPDN ve DPUN'dan oluşan P-tipi SABL birim devresinden oluşan N-tipi SABL ünite devresinin yapısı Şekil 1'de gösterilmektedir.

N-tipi SABL devresinin çıkış sinyalinin iki bitişik saat döngüsüne geçişini örnek olarak alarak, SABL devresinin sabit güç tüketimi özellikleri analiz edilmiş ve sonuçlar Tablo 1'de gösterilmiştir. Bunlar arasında, devrenin çift ray çıkış sinyali dışarıdadır. N'inci veya n + 1 saat çevriminde ne olursa olsun, devre ön şarj aşamasına girdiğinde, çift ray çıkışı yüksek bir seviyeye önceden yüklenir; devre değerlendirme aşamasında çalışırken, çift ray tamamlayıcı sinyaller çıkarır. Tablo 1'deki verilerin analizi, iki bitişik saat döngüsünde, devrenin çıkış sinyalinin 0 1 bir geçişe sahip olduğunu, yani SABL devresinin sabit bir sinyal geçiş oranına sahip olduğunu göstermektedir. Aynı zamanda, diferansiyel aşağı çekme ağı nedeniyle, SABL devresindeki tüm düğümler, şarj paylaşımının neden olduğu dinamik güç tüketimi farklılıkları olasılığını ortadan kaldıran tam bir şarj ve deşarj sürecine sahiptir. Literatürden, devrenin güç tüketiminin düğüm sinyal atlama oranıyla orantılı olduğu bilinmektedir, bu nedenle N-tipi SABL devresinin enerji tüketimi her saat için sabit bir değerdir. P-tipi SABL devresinin çalışma süreci, N-tipi SABL devresininkine benzer ve aynı zamanda sabit güç tüketimi özelliğine sahiptir, bu nedenle SABL devresi DPA saldırılarına karşı etkili bir şekilde savunma yapabilir.

SABL devre tasarımına dayanan iki temel mantık kapısı devresi ve semboller Şekil 2'de gösterilmektedir. Temel mantık kapıları, belirli mantık işlevlerine sahip devreleri gerçekleştirmek için kullanılabilir.

2 SABL devresine dayalı kaydırma yazmacı tasarımı

Dijital şifreleme sisteminde, vardiya kaydı, şifreleme sisteminin güvenliğini etkileyen, dengesiz enerji tüketen bir bileşendir. Saldırı teknolojisinin gelişmesiyle birlikte, DPA saldırılarına karşı savunma yapabilen bir şifreleme sistemi, vardiya kaydının güvenliği için daha yüksek gereksinimler ortaya koymaktadır.

2.1 D flip-flopunu temizleme ve ayarlama tasarımı

SABL devresine dayalı bir D flip-flop durum denklemi formül (2) ve formül (3) 'te gösterilmiştir:

2.2 Çok bitli kaydıran yazmaç tasarımı

Kaydırma yazmacı, sola kaydırma, sağa kaydırma ve birleştirme ve birleştirme işlevlerine sahip bir kayıttır ve bir saat sinyalinin eylemi altında belirli işlevleri gerçekleştirir. Sol kayma, kayıt defterindeki verilerin yüksekten alta kayması anlamına gelirken, sağa kaydırma bunun tersidir. Giriş ve çıkış birleştirme, verilerin kayıtlara paralel olarak girilmesi ve bir sonraki saat döngüsünde paralel olarak çıkılması anlamına gelir. SABL devresinin çalışma prensibini birleştirerek, DPA saldırılarına karşı savunma yapabilen bir kaydırma yazmacı tasarımı önerilmiş ve çalışma durumu Tablo 2'de gösterilmiştir.

3 Deneysel sonuçlar ve analiz

TSMC 65 nm COMS işlem cihazı parametreleri altında, SABL devresine dayalı olarak yukarıda bahsedilen 4 bitlik kaydırma yazmacı devresini simüle etmek için Spectre aracını kullanın.Simülasyon dalga formu, çalışma frekansının 100 MHz olduğu ve devrenin çıkış sinyalinin karşılaştırıldığı Şekil 5'te gösterilmektedir. Giriş sinyalinden bir saat döngüsü geciktirme. Eğer clk = 0 ise, vardiya yazmacının çıkış terminali yüksek seviyeye önceden şarj edilir; aksi takdirde, clk = 1 olduğunda devre, C = 1 olduğunda temizleme ve ayar fonksiyonunu gerçekleştirir; Ren = 1 olduğunda, diğeri kullanır Etkinleştirme sinyali geçersiz olduğunda, devre sağa kaydırma işlevini gerçekleştirir; Len = 1 ve diğer etkinleştirme sinyalleri geçersiz olduğunda devre, sola kaydırma işlevini gerçekleştirir; Den = 1 ve diğer etkinleştirme sinyalleri geçersiz olduğunda, devre içeri ve dışarı birleştirme işlevini gerçekleştirir. Şekil 5'deki simüle edilmiş dalga formunu analiz ederek, tasarlanan devrenin doğru mantık fonksiyonuna sahip olduğunu görebiliriz.

Farklı saat döngülerindeki güç tüketimi enerjisindeki fark, kaydırma yazmacı devresinin DPA saldırı performansını karakterize etmek için kullanılır Spectre simülasyon sonucu Şekil 6'da gösterilmiştir. Bu makalede tasarlanan kaydırma yazmacının farklı saat çevrimlerinde tutarlı bir güç tüketimi eğrisine sahip olduğu, sola kaydırma, sağa kaydırma ve birleştirme giriş / çıkış işlevlerine sahip olduğu ve önemli sabit güç tüketimi performansına sahip olduğu ve etkili olabileceği şekilden görülebilir. DPA saldırılarına karşı zemin savunması.

Normalleştirilmiş Enerji Sapması (NED) ve Normalleştirilmiş Standart Sapma (NSD), genellikle devrelerin DPA saldırılarına karşı performansını ölçmek için kullanılan iki göstergedir. Tanımları şunlardır:

Bunlar arasında E, devrenin tek bir saat döngüsündeki güç tüketimidir, Emax, farklı saat döngülerinde devrenin maksimum güç tüketimidir, Emin, farklı saat döngülerinde devrenin minimum güç tüketimidir ve E, devrenin farklı saat döngülerindeki güç tüketimidir. Standart sapma, birden fazla saat döngüsüne sahip bir devrenin ortalama güç tüketimidir. Şekil 7, bu makalede tasarlanan 4 bitlik kaydıran yazıcının karşılaştırma sonucunu ve ilgili literatürün sabit performansını göstermektedir. PVT (Proses Voltaj Sıcaklığı), devre imalatı ve çalışması sırasında karşılaşılabilecek proses açısı, voltaj ve sıcaklıktır. Şekil 7'deki verilerden, bu makalede önerilen kaydırma yazmacı devresinin, çeşitli PVT kombinasyonları altında% 2,66'dan daha az NED ve% 0,63'ten daha az NSD'ye sahip olduğu görülebilir.Kompozit yazmaç sistemi ile karşılaştırıldığında, 4-bit kaydırma yazmacı sırasıyla NED ve NSD'de etkilidir. % 92.29 ve% 94.27 azaltıldı ve savunma diferansiyel güç analizinde olağanüstü performansını kanıtladı.

4. Sonuç

DPA saldırıları pratikte basit, verimli ve uygulanabilir olduğundan, şifreleme sisteminin güvenliğini ciddi şekilde tehdit ederler. Bu makalede, ana-bağımlı tetikleme modu ve SABL devresini sabit güç tüketimi özellikleriyle birleştirerek, savunma diferansiyel güç analizi performansına sahip bir kaydırma yazmacı tasarım şeması önerilmiştir. TSMC 65 nm CMOS sürecini kullanan Spectre simülasyon sonuçları, tasarımın doğru mantık fonksiyonuna sahip olduğunu gösterir.Farklı PVT kombinasyonları altında, NED% 2,66'dan ve NSD% 0,63'ten düşüktür, bu da diferansiyel güç analizine etkin bir şekilde direnebilir.

Referanslar

CHONG K S, Ne K Z L, HO W G, ve diğerleri.Diferansiyel güç analizine karşı koymak: şifrelenmiş verileri devre hücrelerinden gizlemek // IEEE Uluslararası Elektron Cihazları ve Katı Hal Devreleri Konferansı. 2015: 297-300.

ABDI O, JAHANIAN A. Güç analizi saldırısı için yeni bir nano ölçekli diferansiyel mantık stili // IEEE Elektrik Mühendisliği Konferansı. 2015: 584-588.

TANG W, JIA S, WANG Y. Şarj paylaşım mekanizmasına dayalı çift voltajlı tek raylı dinamik DPA dirençli mantık // IEEE Uluslararası Elektron Cihazları ve Katı Hal Devreleri Konferansı. 2015: 483-486.

POPP T, MANGARD S. Maskeli çift raylı ön şarj mantığı: Yönlendirme Kısıtlamaları Olmadan DPA Direnci // Kriptografik Donanım ve Gömülü Sistemler Uluslararası Çalıştayı. 2005: 172-186.

Hao Lipeng, Wang Pengjun, Zhang Yuejun, Diferansiyel enerji saldırısına dirençli JK parmak arası terliklerin tasarımı. Journal of Circuits and Systems, 2012 (6): 117-123.

Yu Jingchao, Yan Yingjian, Wu Xuetao, ve diğerleri.Güç saldırılarına karşı mantık devreleri üzerine araştırma.Microelectronics, 2015 (4): 497-501.

Yan Shi. Dijital Elektronik Teknolojisinin Temelleri. 5. Baskı. Beijing: Higher Education Press, 2006.

JAN M R, ANANTHA C, BORIVOJE N. Digital Integrated Circuits: Circuits, Systems and Designs. 2nd Edition. Beijing: Electronic Industry Press, 2008.

TIRI K, AKMAL M, Verbauwhede I. Akıllı kartlarda diferansiyel güç analizine dayanmak için sinyalden bağımsız güç tüketimine sahip dinamik ve diferansiyel bir CMOS mantığı // Avrupa Katı Hal Devreleri Konferansı. 2002: 403-406.

Liu Zeyi, Gao Neng, Tu Chenyang ve diğerleri.Enerji analizi saldırılarına karşı birleşik kayıt sistemi. Chinese Journal of Cryptography, 2014 (5): 411-421.

-

- Li Xiaofeng'in "Tracking" i, çarpıcı dönüşümün ardından Busan Film Festivali yarışma birimi "Girl Nezha" için kısa listeye alındı.

-

- Yolda "Teacher Cang" yazan bir USB flash sürücü gördüm, onu almak ister misin? | Tek Boynuzlu At Hacker Yang Qing ile röportaj

-

- Etkiye bakın Derin dağlarda ve eski ormanlarda geçen 26 yılın ardından, "Chongqing'deki ilk zirvenin" giderek daha iyi hale geldiğini izledi.