H-Ağacı ve 14 nm işlem altında saat ağına dayalı hibrit saat ağacının araştırılması ve uygulanması

Gao Hua, Li Hui

(Bilgi Bilimi ve Teknolojisi Okulu, Çin Bilim ve Teknoloji Üniversitesi, Hefei 230026, Anhui)

Dijital entegre devrelerin tasarımında, saat sinyali, veri iletimi için mihenk taşıdır.Dijital çip içerisinde en yüksek dönüşüm frekansına ve en uzun kablolama mesafesine sahip sinyal olarak, saat sinyali de dijital çipin güç tüketiminin önemli bir parçasıdır. Dijital çipin güç tüketimini, işlevini ve kararlılığını optimize etmek için, saat ağacı GF14 nm işlemi altında optimize edilmiştir ve H-Ağacı ile saat örgüsünü birleştiren bir hibrit saat ağacı yapısının tasarım yöntemi önerilmiştir. Omurga düzeni, genel saat ağacının performansını ve dengesini optimize eder. Simülasyon sonuçları, hibrit saat ağacı yapısının, saat ağacının performansını önemli ölçüde artırabildiğini, kablo uzunluğunu, saat eğriliğini ve yayılma gecikmesini etkili bir şekilde azaltabildiğini ve PVT gibi çevresel parametrelerin etkisini azaltabildiğini göstermektedir.

14 nm; saat ağacı sentezi; saat ağı; H-Ağacı

Çin Kütüphanesi Sınıflandırma Numarası: TN47

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.171805

Çince alıntı biçimi: Gao Hua, Li Hui. 14 nm proses altında H-Ağacı ve saat örgüsüne dayalı hibrit saat ağacının araştırılması ve uygulanması.Elektronik Teknoloji Uygulaması, 2017, 43 (11): 34-37, 42.

İngilizce alıntı biçimi: Gao Hua, Li Hui. 14 nm teknolojisine dayalı H-Ağacı ve saat örgüsü karışık saat ağacının araştırılması ve gerçekleştirilmesi.Elektronik Tekniğin Uygulanması, 2017, 43 (11): 34-37, 42.

0 Önsöz

Yarı iletken üretim teknolojisinin sürekli gelişmesiyle birlikte dijital çiplerin çalışma frekansı önemli ölçüde arttı ve çip güç tüketimi de arttı. Dijital sistemin "kalbi" olarak, saat sinyali dijital sistemin işlevi, performansı ve kararlılığında belirleyici bir rol oynar. Bu nedenle, saat sinyalinin özellikleri ve saat ağacının düzeni tasarımcıların dikkatini çekmiştir.Saat sinyalinin yayılma gecikmesi (Saat Gecikmesi) ve saat çarpıklığı (Saat Kayması) nasıl azaltılır ve PVT (İşlem, voltaj, sıcaklık) ortamı nasıl azaltılır Değişkenlerin ve güç tüketiminin etkisi, günümüzün saat ağacı tasarımının konusu haline geldi. Buna ek olarak, bugün üretim teknolojisinin hızla gelişmesiyle birlikte, teknolojinin gelişmesi kaçınılmaz olarak dijital IC'nin tasarım yöntemi için yeni gereksinimler ortaya koyacaktır.Geleneksel saat ağacı yapısı ve sürücü hücre kütüphanesi artık yeni teknolojinin getirdiği yüksek gereksinimleri karşılamıyor. Gelişmiş üretim süreci GF14 nm altındaki H-Ağacı ve saat örgüsüne dayanan hibrit saat ağacı tasarımı, belirli bir uygulanabilirlik ve araştırma değerine sahiptir.

Bu aşamada, dijital IC'ler için ana akım saat ağacı yapıları arasında H-Ağacı, X-Ağacı, dengeli-Ağaç ve saat ağı bulunur.H-Tree'nin merkez noktasından her bir yaprak düğümüne olan mesafe teorik olarak eşittir, bu nedenle küçük bir saat sapmasına sahiptir. avantaj. Bununla birlikte, kayıt düzeni üzerinde katı gereksinimleri vardır ve kablolama zordur; saat örgüsünün saat ağacının uzunluğu kısadır, bu nedenle saat gecikmesi küçüktür, ancak saat sapmasını garanti etmek zordur. İki saat ağaç yapısının avantajlarından tam olarak yararlanmak, saat sinyalinin yayılma gecikmesini ve sapmasını azaltmak ve çevresel faktörlerin etkisini azaltmak için, bu makale H-Tree'nin hibrit saat ağacı yapısını ve GF14 nm sürecini temel alan saat ağını inceler.

1 H-Ağacı ve saat ağına dayalı saat ağacı yapısı

Fiziksel tasarımda saat sinyalinin yayılmasına saat ağacı denir Saat ağacının başlangıç noktasına kök düğüm (Kök pini) denir Saat sinyali, bir dizi dağıtılmış düğümden kaydın saat girişine ve bu saat sinyali yayılmasının sonuna geçer. Yaprak iğnesi denir. Saat sinyali kök düğümden başlar ve sonunda adım adım eklenen sürücü (Tampon) aracılığıyla yaprak düğümüne ulaşır ve böylece tüm saat ağacını oluşturur.

H-Ağacı ve saat örgüsüne dayanan hibrit saat ağacının mantıksal yapısı esas olarak üç bölümden oluşur: Üst-H, saat örgüsü ve Yerel-H. Top-H, Üst Seviyedeki H-Tree yapısıdır; saat ağı, saat sinyallerini eşit şekilde yayan ve Top-H ve Local-H'yi birbirine bağlayan bir köprü görevi gören bir ağdır; Local-H, esas olarak şurada oluşan yerel bir H-Ağacıdır Her modülün içinde, karşılık gelen yaprak düğüm gerçek kayıttır. Spesifik mantıksal yapı aşağıdaki gibidir:

(1) Top-H bölümünde, saat sinyali kök düğümden başlar, yonga düzeyinde sürücü TMAC boyunca yayılır ve saat sinyalini modül birimine eşit mesafeli olarak aktarır. Genel TMAC, yatay TMAC'ın TMACH olarak adlandırıldığı ve dikey TMAC'nin TMACV olarak adlandırıldığı bir H-Ağacı yapısında dağıtılır. En üstteki H-Ağacının son seviye sürücüsüne MBUF adı verilir ve MBUF çıktısı aslında saat sinyalinin gerçek çıktısıdır. Saat ağı ile bağlantıyı tamamlamak için, aynı seviyedeki MBUF'nin çıkış ucunu shortBar adı verilen aynı kabloya bağlayın;

(2) Saat ağı aşamasında, modülün ve güç kaynağı ağının düzenine göre, örgü ağ çipin üst metal katmanına kapatılır.Gürültü çapraz konuşma ve çevresel faktörlerin saat sinyali üzerindeki etkisini azaltmak için, dikey ağ ve yatay ağ dönüşümlü olarak güç kaynağı ve zemine yerleştirilir. Çizginin etrafında

(3) Yerel-H bölümünde, ilk olarak, örgü tamponunun, saat ağının konumuna, yani modül içindeki H-Ağacının kök düğümüne göre her bir modülün içine makul şekilde yerleştirilmesi gerekir. Mesh tamponu, yakınlık ilkesine göre ankraj pimi aracılığıyla saat ağına bağlanır; Öte yandan, yerel H-Tree mimarisini daha iyi oluşturmak için, modülün dahili kayıtlarının mantık seviyesine göre Küme şeklinde simetrik olarak dağıtılması gerekir ve mesh tamponunun çıktısı, Yerel saat ağacının başlangıcı, saat ağacı sentezini gerçekleştirir.

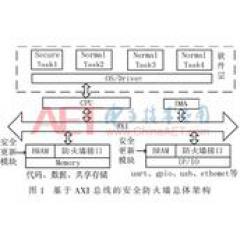

Özetle, saat sinyali kök düğümden başlar, Top-H boyunca eşit mesafeli çipin saat örgü ağına yayılır ve daha sonra ağ üzerindeki çapa pimi aracılığıyla modülün içindeki örgü tamponuna yayılır ve son olarak örgü tamponu yerel saat ağacı olarak kullanılır. Kök düğüm, çeşitli sürücü seviyeleri aracılığıyla son kayıt birimine yayılır. H-Ağacı ve saat ağına dayalı hibrit saat ağacının mantıksal yapısı Şekil 1'de gösterilmektedir.

2 Karışık saat ağacının tasarım yöntemi ve gerçekleştirilmesi

Aşağıda, H-Ağacı ve saat ağına dayalı bir hibrit saat ağacının belirli bir uygulama durumu açıklanmaktadır. Bu tasarım, GF14 nm süreci altındaki bir GPU çipidir.GF14 nm süreci şu anda Global Foundary tarafından geliştirilen dünyanın önde gelen üretim sürecidir. Çipin alanı yaklaşık 22 mm × 16 mm, yonganın ana frekansı 1.3 GHz ve H-Ağacı ve saat ağına dayalı hibrit saat ağacı yapısı benimsenmiştir.Saat ofsetinin 80 ps'nin altında kontrol edilmesi ve yayılma gecikmesinin 350 ps'den az olması gerekir.

Mantıksal yapıdan farklı olarak, hibrit saat ağacı tasarım yönteminin fiziksel uygulaması iki uygulama aşamasına ayrılmıştır: saat omurgası ve saat ağı. Saat omurgası aşaması esas olarak H-Tree'nin, yani modülün içindeki çip seviyesinde H-Ağacı ve H-Ağacı'nın inşasını gerçekleştirir.Çip seviyesindeki H-Ağacı TMAC ile uygulanmalıdır.Modül içindeki H-Ağacı ilk önce dahili kayıtları yerleştirmelidir. Kısıtlayın ve ardından kök düğüm olarak ağ tamponlu H-Ağacı yapın; saat ağı, esas olarak saat ağının düzenini, bağlantı pimlerinin ayarını ve yerel modül sürücülerinin (Ağ tamponu) yerleşimini tamamlar.

2.1 Saat Sırtının Tasarımı

2.1.1 Top-H'nin Tasarımı ve Uygulanması

Saat omurgasının tasarımı, modülün içindeki çip seviyesini ve H-Ağacı içerir. GFXCLK saat sinyalini bir örnek olarak alırsak, GFXCLK sinyal kaynağı çip saat modülünün PLL biriminden üretilir ve PLL, Dijital Frekans Sentezleyici (DFS) aracılığıyla kararlı bir frekans saat çıkışı üretir. Çip düzeyindeki H-Ağacı, saat kök düğümünden başlar, önce dikey omurga boyunca yayılır ve yatay omurgayı tüm düzeylerde TMACV'den geçirir. Dikey omurgadaki sürücü TMACV ve yatay omurgadaki sürücü TMACH'dir. Saat omurgasının genel yapısı Şekil 2'de gösterilmektedir.

Yatay omurganın avantajı, GFXCLK sinyalini ilgili modüllere eşit bir şekilde yayabilmesi ve yatay sargı kaynaklarını büyük ölçüde kurtarmasıdır. Yatay omurganın yerleşim özelliği, aynı omurganın TMACH'sinin aynı yatay çizgi üzerine yerleştirilmesi gerektiğidir, böylece TMACH'a dayalı H-Ağacı yatay yönde kablolanacaktır. Yatay omurganın yaprak düğümü MBUF olarak adlandırılır, yani MBUF, H-Tree'nin yonga seviyesindeki son sürücüsüdür ve MBUF çıkışı, her modül tarafından okunan gerçek GFXCLK sinyalidir. Yatay omurga tasarımındaki zorluk, TMACH'in düzeninde ve yerleşiminde yatmaktadır.Çip mantık seviyesinin karmaşıklığı ve çok sayıda kapı devresi nedeniyle, TMACH'yi herhangi bir modülün içine yerleştirmek, mevcut modülün kablolama sıkışıklığı ve zamanlaması üzerinde olumsuz bir etkiye sahip olacaktır. TAMCH yerleştirmeden önce, GFXCLK saatle ilgili modüllerin yerleşim planlamasına odaklanmak gerekir. Çipin tamamında GFXCLK saati ile ilgili 60 modül bulunmaktadır.Bu 60 modül farklı sıralara dağılmıştır.Her sıraya kablolama zorluğu yüksek modüller ve düşük kablolama zorluğu olan modüller dönüşümlü olarak yerleştirilir ve son olarak TMACH kablolama zorluğuna yerleştirilir. Küçük modülün içinde. Bu, TMACH'in tüm çipin bloğu ve zamanlaması üzerindeki etkisini en aza indirebilir. Yatay omurganın spesifik yapısı Şekil 3'te gösterilmektedir.

2.1.2 Local-H Tasarımı ve Uygulaması

Modül içindeki saat ağacı için H-Tree yapısı da benimsenmiştir. H-ağacının kök düğümüne örgü tamponu adı verilir ve ağ tamponu saat ağına yakın yerleştirilir. H-Tree'nin modül içindeki genel saat ofsetini ve yayılma gecikmesini en aza indirmek için, IC Complier 2'de create_bound ve create_rp_group, birim yerleştirme işlemi sırasında belirli alanlara ve tüm belirli alanlara aynı mantık seviyesinin kayıtlarını yerleştirmek için kullanılır. Modül içerisinde yarı simetrik bir dağılım vardır.

create_rp_group-name GFXCLKgroup1-satırlar 10-sütun 3

add_to_rp_group GFXCLKgroup1-hücreleri

create_bound -name GFXCLKbound1-boyutlar {103} -tip sabit

Şekil 4, yonga içindeki bir modülün yerel saat ağacını göstermektedir.Modül içinde 9 saat ağı vardır ve bitişik saat ağları arasındaki mesafe 200 m'dir.GFXCLK saat sinyali, 9 saat ağından modüle verilir ve yerel H- yapılır. Ağaç, saat ağacının mantık seviyesi 18 seviyedir.

2.2 Saat Ağının Tasarımı

Saat ağı, saat sinyalinin hibrit saat ağacı yapısında eşit olarak yayılmasında rol oynar. Saat ağı Hmesh ve Vmesh'e bölünmüştür. Hmesh yataydır ve M10 zemine yerleştirilir; Vmesh dikeydir ve M11 zemine yerleştirilir. Örgü yayılma işlemi sırasında saat sinyalinin sinyal ve gürültü karmasını azaltmak için, Vmesh güç kaynağı ile toprak arasına yerleştirilir. Aynı zamanda, saat örgüsünün olası IR Düşüşü ve EM problemlerini bastırmak için, kablolama planlaması sırasında ağ genişletilir.Her ağın genişliği 0,96 m ve ağ ile bitişik güç topraklama teli arasındaki mesafe 1,928 m'dir. Yüksek seviyeli metalin daha iyi zamanlama özellikleri nedeniyle, yalnızca M10 ve M11 katmanları, gereksiz sargı kaynaklarını işgal etmeyen saat ağıyla eşit şekilde kaplanır. Çip seviyesindeki saat ağı Şekil 5'te gösterilmektedir.

2.3 Saat ağı ve omurga kombinasyonu

Saat ağı ve saat omurgasının yerleşim planlamasını tamamladıktan sonra, tam bir saat ağacı yapısı oluşturmak için ağı ve omurgayı bağlamanız gerekir. Saat omurgasının son sürücüsü, MBUF'nin çıkışlarını GFXCLK'nin "çıkış çubuğu" ile aynı yatay çizgiye bağlamak için shortBar kullanan MBUF'dir. Daha sonra shortBar M11 katmanının Vmesh'ine bağlanır, yani GFXCLK sinyali dikey mesh ağına yayılır Vmesh, M10 katmanının Hmesh ağını sürmeye devam eder, böylece saat sinyali saat ağı boyunca eşit olarak dağıtılır. GFXCLK saat sinyalini her bir modüle dahil etmek için, ankraj piminin Hmesh'in ucuna bağlanması gerekir ve ankraj piminin diğer ucunun, dahili H-Tree'nin kök düğümü olan mesh tamponuna bağlanması ve böylece tüm saat ağını çalıştırması gerekir. Spesifik bağlantı ilişkisi Şekil 6'da gösterilmektedir.

Saat ağacı yapısının performansını test etmek için örnek olarak GPU'daki gp_tsd modülünü alın. Gp_tsd modülü GPU'daki kontrol verisi işleme modülüdür ve modül GFCLK saatini içerir. GFCLK'nin gp_tsd modülünde uygulanması Şekil 7'de gösterilmektedir. Örgü tamponunun konumunu daha iyi sunmak için, Şekil 7 sadece saat ağacının ilk 5 seviyesinin şeklini gösterir.

PrimeTime'da, H-Ağacı ve saat ağını temel alan yukarıdaki saat ağı, geriye doğru açıklamalı ve tüm saat ağının gecikme ve çarpıklığı analiz ediliyor.Son olarak, Şekil 8'de gösterildiği gibi, GFXCLK'nin çarpıklığı 54 ps'dir ve gecikme 320 ps'dir. Tasarım gereksinimleri.

Aynı zamanda, H-Ağacı ve saat ağına dayalı saat ağı, kısa kablolama mesafesi ve az sayıda saat sürücüsü özelliklerine sahiptir, bu da dijital yongaların güç tüketimini etkili bir şekilde azaltır. Bu tasarım, güç tüketimi analizi için Synopsys'in PrimetimePX ürününü kullanır ve Şekil 9 ve Şekil 10'da gösterildiği gibi saat ağacı optimizasyonundan önce ve sonra güç tüketimi analizi histogramını elde etmek için grafik arayüzün Güç Analizi Sürücüsünü Göster seçeneğini kullanır.

Optimizasyondan sonra modülün toplam gücünün yaklaşık% 2,53 azaldığı yukarıdaki histogramdan görülebilmektedir. Statik güç tüketimi, yani Kaçak Güç, 0.0117 W olup, toplam güç tüketiminin% 3.78'ini oluşturur; Dinamik güç tüketimi, yani Anahtar Gücü ve Dahili Güç sırasıyla 0.2145 W ve 0.0825 W olup, toplam güç tüketiminin% 96.22'sini oluşturur; Yaklaşık 0.3087 W.

3 özet

Bu makale, H-Ağacı ve saat ağına dayalı bir hibrit saat ağacı yapısı önermektedir.Saat yapısının uygulanması iki bölüme ayrılmıştır: saat omurgası ve saat ağı Saat omurgası, modülün içindeki H-Ağacı'nın yonga seviyesini ve yapısını içerir. Mesh, çipin içinde eşit olarak dağıtılır ve çip seviyesi ile modülün dahili saat ağacı arasındaki bağlantıdan sorumludur. Deney, GF14 nm işlemi altında GPU içindeki GFXCLK hibrit saat ağacının tasarımını verir.PrimineTime ve PTPX arka açıklama ve analizinden sonra, hibrit saat ağacının iyi bir saat sapması ve saat gecikmesine sahip olduğunu ve saat ağacı kablolamasını önemli ölçüde azalttığını kanıtlar. Uzunluk ayrıca çipin genel güç tüketimini de etkili bir şekilde azaltır.

Referanslar

BAKOGLU H B. VLSI.1990 için devreler, ara bağlantılar ve paketleme.

CHEN P H, MALKANI S, PENG C M. Dinamik diyot, düşürme ve jumper yerleştirme ile anten probleminin düzeltilmesi Proc Quality Electronic Design.2000.

BAKOĞLU H B, WALKER J T, MEINDL J D. ULSI ve WSI devrelerinde azaltılmış saat sapması için simetrik bir saat dağıtım ağacı ve optimize edilmiş yüksek hızlı ara bağlantılarProc.IEEE Int.Conf. Computer Design.1986.

Dai Hongwei, Guo Wei, Han Zeyao, vb. Düşük güçlü bir SoC yongası için saat yönetimi stratejisi Mikroelektronik ve Bilgisayar, 2005 (3).

Chen Feifei, Wang Zhenyu, Yan Wei.Kılçık saat yapısının hızlı gerçekleştirme yöntemi Mikroelektronik ve Bilgisayar, 2014 (2).

Ji Rong, Zeng Xianjun, Chen Liang, vb. Senkron Dijital Sistemin Saat Dağıtımı ve Eğik Telafi Teknolojisi Üzerine Araştırma, Bilgisayar Mühendisliği ve Bilimi, 2009 (3).

Qianlu, Lin Pingfen ASIC arka uç tasarımında saat çarpıklığı ve saat ağacı sentezi Yarıiletken Teknolojisi, 2008 (6).

Hu Jingzhen, Tang Changwen, Min Hao. Derin mikron altı dijital entegre devrelerin otomatik tasarım metodolojisi Mikroelektronik, 2002 (4).