Faz kilitli döngüye dayalı yüksek hızlı osiloskopun eşdeğer örnekleme sisteminin tasarımı

Cha Tianyi 1, Chen Shengqi 2, Ge Junyao 3

(1. Changshu Orta Okulu, Jiangsu Eyaleti, Suzhou 215500, Jiangsu; 2. Elektrik Mühendisliği ve Uygulamalı Elektronik Teknolojisi Bölümü, Tsinghua Üniversitesi, Pekin 100084;

3. İletişim ve Bilgi Mühendisliği Okulu, Nanjing Posta ve Telekomünikasyon Üniversitesi, Nanjing 210023, Çin)

Fraksiyonel frekansa bölünmüş faz kilitli döngü yongası ADF4351'i örnekleme saati üreteci olarak kullanarak, eşit hassasiyetli frekans ölçümü için FPGA kullanarak, fark frekansı yönteminin ardışık eşdeğer örnekleme ilkesini kullanarak, 160 GS / s'lik en yüksek eşdeğer örnekleme hızına sahip yüksek hızlı bir osiloskop tasarlandı. Örnekleme sistemi. Aynı zamanda, saat dağıtıcısı ve dijital gecikme hattı aracılığıyla alternatif örnekleme saatleri üretilir ve sistemin en yüksek gerçek zamanlı örnekleme hızının 1 GS / s'ye ulaşması için en yüksek örnekleme hızı 250 MS / s olan 4 adet 8-bit ADC kullanılır. Düşük titreşimli saat kaynağı nedeniyle, sistem DC'den 500 MHz'e kadar tasarım bant genişliği içinde iyi bir gürültü performansı sağlar ve sinyal-gürültü oranı DDS teknolojisine dayalı eşdeğer örnekleme sisteminden daha iyidir.

Çin Kütüphanesi Sınıflandırma Numarası: TN911.8; TM935.38

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.2017.05.023

Çince alıntı biçimi: Zha Tianyi, Chen Shengqi, Ge Junyao.Faz kilitli döngüye dayalı yüksek hızlı osiloskop için eşdeğer örnekleme sisteminin tasarımı.Elektronik Teknoloji Uygulaması, 2017, 43 (5): 94-97.

İngilizce alıntı biçimi: Zha Tianyi, Chen Shengqi, Ge Junyao.PLL'ye dayalı yüksek hızlı osiloskop için eşdeğer örnekleme sisteminin tasarımı.Elektronik Tekniğin Uygulanması, 2017, 43 (5): 94-97.

0 Önsöz

Yüksek hızlı osiloskopların uygulanması için, fraksiyonel frekanslı faz kilitli döngü teknolojisine dayalı bir diferansiyel frekans eşdeğer örnekleme sistemi tasarlanmıştır.En yüksek eşdeğer örnekleme oranı, ölçülen sinyal frekansının artmasıyla artar. Zamanın doğuştan bir avantajı vardır. DDS (Direct Digital Synthesizer) teknolojisine dayalı ana akım eşdeğer örnekleme şemasıyla karşılaştırıldığında, fark frekansı yöntemi yüksek frekanslarda daha iyi güvenilirliğe sahiptir. Aynı zamanda sistem, periyodik ve periyodik olmayan sinyalleri toplama performansını hesaba katarak, zamanlı alternatif örnekleme yoluyla gerçek zamanlı örnekleme oranını iyileştirir.

1 Sistem tasarım şeması

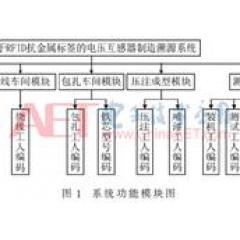

1.1 Sistem prensibi blok şeması

Şekil 1'de gösterildiği gibi, örnekleme sistemi esas olarak FPGA'daki çevresel devrelerden ve dijital devrelerden oluşur. Sistem eşdeğer örnekleme yaptığında, tetikleme devresi ve frekans bölücü devresi, frekans ölçümü için bir kare dalga üretir Sinyal frekansı eşit hassasiyetli frekans ölçüm modülü tarafından ölçüldükten sonra, NIOS II yazılım çekirdeğinde yerleşik olan program gerekli frekansı hesaplar. Örnekleme saat frekansı bundan daha yüksektir ve Faz Kilitli Döngü (PLL) modülü örnekleme saatini oluşturmak için kontrol edilir. Bundan sonra, ADC, örnekleme saatinin sürdüğü sinyal alımını tamamlar.Veri tampon modülü tarafından veri alındıktan sonra, ikincil örnekleme, tamsayı örnekleme modülünde ve ondalık örnekleme modülünde tamamlanır, aynı periyotta fazla örnekleme noktaları gerektiği gibi atılır ve eşdeğer örnekleme düzeltilir Oran hatası. Son olarak, örneklenen veriler RAM'de depolanır ve osiloskobun insan-bilgisayar etkileşimi kısmına aktarılır.

Sistem, zaman alternatifli örnekleme gerçekleştirirken, saat dağıtım modülü, PLL modülünün saat çıkışını 4 kanala yayar ve 3 kanalı 1/4, 2/4, 3/4 saat döngüleri ile geciktirmek için dijital gecikme hattını kullanır ve Gecikmesiz olan birlikte, sırayla 90 ° ile farklı fazlara sahip dört alternatif örnekleme saati oluşturur ve dört 250 MS / s 8-bit ADC yongasını çalıştırır, AD94811 GS / s örnekleme hızı ile alternatif örnekleme elde eder.

1.2 Sistem teorisi analizi

1.2.1 Sıralı eşdeğer örneklemeye ulaşmak için fark frekansı yönteminin prensip analizi

Periyodik sinyaldeki farklı fazların noktaları her döngüde tekrar tekrar görünecektir.Bu nedenle, döngüdeki her örnekleme noktasının göreceli konumu T kadar hareket ettiği sürece, sıralı eşdeğer örnekleme tamamlanabilir ve periyodik sinyal geri yüklenebilir. Ardışık eşdeğer örnekleme için fark frekansı yöntemini kullanırken, önce periyodik sinyalin frekansını f ölçün ve ardından f / n-f frekanslı bir örnekleme saati fclk oluşturun. İkisi arasındaki süre T farklı olduğundan, örnekleme noktasının periyot içindeki göreceli konumu, periyot her geçtiğinde T kadar hareket eder. Son örnekleme noktası, ilk örnekleme noktasına göre bir sinyal döngüsü kaydırıldığında, tam bir döngünün örneklemesi tamamlanır.

Bu sistemin analog bant genişliği DC ila 500 MHz olduğundan, ADC örnekleme saat aralığı 20-250 MHz'dir ve analog bant genişliği örnekleme saat aralığını aştığından, farklı frekans çarpma / bölme katsayıları n seçmek gerekir (bkz. Tablo 1). Ne zaman < 1'de, tamsayı örnekleme modülünün, n: 1 oranına göre örnekleme dizisini alt örneklemesi ve aynı dönemdeki fazlalık örnekleme noktalarını atması gerekir.

Bu nedenle, nihai sistemin eşdeğer örnekleme oranı:

Bu sistemde f'den beri < < f, dolayısıyla denklem (3) şu şekilde yaklaştırılabilir:

Denklemden (4), frekans çözünürlüğü f olan bir sistem için, n değeri sabit olduğunda sistemin en yüksek eşdeğer örnekleme hızının f2 ile orantılı olduğu görülebilir. Bu nedenle, bu eşdeğer örnekleme yöntemi, yüksek frekanslı sinyalleri örneklemek için çok uygundur Yeterince küçük bir f oluşturabildiği sürece, n değeri büyük olduğunda düşük hızlı bir ADC ile yeterince yüksek bir eşdeğer örnekleme oranı elde edilebilir.

1.2.2 Örnekleme saati seğirmesinin sistemin dikey doğruluğu üzerindeki etkisi

Saat titreşimi, yüksek hızlı örnekleme sistemlerinin örnekleme doğruluğuna büyük bir sınırlama getirir. F frekansına sahip tam genlikli bir sinüzoidal sinyal girildiğinde, yalnızca saat titreşiminin neden olduğu sistem sinyal-gürültü oranının üst sınırı aşağıdaki formülle tahmin edilebilir:

Mevcut fark frekans yöntemi eşdeğer örnekleme, çoğunlukla yüksek frekanslarda zayıf gürültü performansına sahip olan DDS teknolojisine dayanmaktadır. Örnek olarak yüksek performanslı DDS cihazı AD9854 alınırsa, saat üreteci olarak kullanıldığında tipik rms seğirmesi 25 ps'dir. Denklem (7) yerine, sistemin dikey çözünürlüğünün 500 MHz'de 3,38 bit veya daha azıyla sınırlı olacağı görülebilir. . Saat kalitesini iyileştirmek için, bu sistem örnekleme saatini oluşturmak için PLL yongası ADF4351'i kullanır.Tipik ortalama karekök titreşimi sadece 0,4 ps'dir. Hesaplama, titreşimin neden olduğu etkin bit sayısının üst sınırının 9,34 bit olduğunu gösterir. Bu artık 8 bitlik dikey çözünürlüklü bir osiloskop için geçerli değildir. Tekrar bir darboğaz haline gelin.

1.2.3 Sistem zaman tabanı ayarlama yönteminin analizi

Test sırasında, bu sistem dalga biçimini görüntülemek için 800 yatay çözünürlüğe sahip bir ekran kullanır ve yatay yönü 1, 2 ve 5'lik adımlarla 500 ps / div 500 ms / div olan 10 ölçek bölümüne (böl) bölünür. Aralık dahilinde 28 zaman bazlı vites ayarlayın. Sistem dalga biçimini gösterdiğinde, her örnekleme noktası bir piksele karşılık gelir ve zaman tabanı dişli t (s / div) ile eşdeğer örnekleme hızı fs arasındaki ilişki aşağıdaki gibidir:

Burada m, ölçek bölümlerinin sayısıdır ve P, ekranın yatay çözünürlüğüdür.

Formül (8) 'den, sistem zaman tabanı t ile sistem eşdeğer örnekleme hızı fs arasında bire bir uyuşma olduğu görülebilir. Zaman temelli dişli en küçük 500 ps / div'e ayarlandığında, sistem 160 GS / s'lik en yüksek eşdeğer örnekleme hızına ulaşır. Sistemin eşdeğer örnekleme oranı, örnekleme saat frekansı tarafından belirlenir Bu nedenle, sistem zaman temel dişlisini ayarlamak, kullanıcı tarafından seçilen zaman temel dişlisine göre örnekleme saat frekansını doğru bir şekilde ayarlamaktır. Spesifik olarak, denklemler (1), (3) ve (8) birleştirilerek, zaman temel vites ve sinyal frekansının hesaplanması için gereken örnekleme saat frekansı formülü elde edilebilir:

FRAC parametrelerinin yuvarlanması nedeniyle (bkz. Bölüm 2.1), sistem tarafından üretilen gerçek örnekleme saati frekansı her zaman hesaplanan değerden biraz daha yüksektir ve maksimum fark, sistemin frekans adımıdır. Bu nedenle, fraksiyonel örnekleme modülünün, örnekleme hızı sapmasını düzeltmek için örneklenen verileri tekrar K: 1 oranında örneklemesi gerekir.

2 Sistem yazılım tasarımı

2.1 ADF4351 otomatik konfigürasyon makine tasarımı

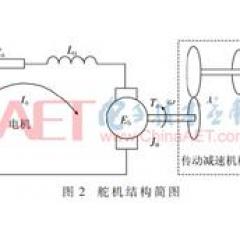

Otomatik yapılandırma makinesi açıldığında, önce ADF4351'i başlatır. Faz algılama döngü frekansı fPFD'yi 10 MHz'lik giriş referans saat frekansına eşit olacak şekilde yapılandırın ve faz kilitli döngüyü çıkış bölücüsünden önce kapanacak şekilde ayarlayın. Bu anda, ADF4351 içindeki faz kilitli döngü yapısı Şekil 2'de gösterilmektedir.

Bunlar arasında, döngü N bölücünün frekans bölme oranı NRF'si üç parametre tarafından belirlenir: INT, FRAC ve MOD. Mümkün olan en yüksek frekans çözünürlüğünü elde etmek için, kesirli modül MOD, maksimum 4095 değerine ayarlanmıştır. Çıkış frekansı bölücünün frekans bölme oranı NOUT, Tablo 2'de gösterildiği gibi çıkış frekansı aralığı tarafından belirlenir.

Nihai çıkış frekansı aşağıdaki formülle hesaplanabilir:

Başlatma tamamlandıktan sonra, otomatik konfigürasyon makinesi eşdeğer örnekleme saatinin üretimini kontrol etmekten sorumludur. İş akışı aşağıdaki gibidir: İlk olarak, örnekleme saatinin frekans çarpma / bölme oranını n belirlemek için giriş sinyali frekansına göre Tablo 1'e bakın. Ardından, denklem (9) 'a göre gerekli örnekleme saat frekansını hesaplayın ve çıkış bölücünün frekans bölme oranını belirlemek için Tablo 2'ye bakın; ardından, denklem (11)' den NRF'yi hesaplayın ve INT değerini elde etmek için NRF'yi yuvarlayın. NRF'nin kesirli kısmı MOD ile çarpılır, yuvarlanır ve ardından FRAC değerini elde etmek için 1 ile eklenir; daha sonra ADF4351 yazmacına INT, FRAC ve MOD yazın, ADF4351 çıkış frekansını otomatik olarak yeniden kilitler ve günceller; son olarak, bu 3 parametreyi ayarlayın Gerçek örnekleme saat frekansını hesaplamak için denklemi (11) yeniden ikame etmek ve kesirli örnekleme oranını hesaplamak için denklem (10) ile ikame etmek.

2.2 Sistem yazılımı iş akışı

Sistem, başlatma sırasında alternatif örnekleme saati çarpıklık kalibrasyonu gerçekleştirir. İlk olarak, ön uç girişini 1 MHz kalibrasyon sinüs dalgasına ayarlayın ve örnekleme saat frekansını 250 MHz'e ayarlayın. 1 ns, 2 ns ve 3 ns gecikme kelimelerini sırasıyla üç programlanabilir gecikme satırına SY89297 yazın. Son olarak, bu temelde, elde edilen sinüs dalgası standart dalga formu ile en yüksek uyuma sahip olana ve kalibrasyon tamamlanana kadar üç yonganın gecikme kelimelerine sürekli olarak ince ayar yapın. Başlatma tamamlandıktan sonra, sistem kullanıcı girdisini bekler ve giriş sinyalinin frekansı değişir ve örnekleme saatini güncellemek için ADF4351 otomatik yapılandırma makinesi zamanında başlatılır. Sistem yazılım süreci Şekil 3'te gösterilmektedir.

3 Sistem donanımı tasarımı

3.1 Kesirli frekans PLL'ye dayalı örnekleme saat kaynağının tasarımı

Bu sistemin örnekleme saat üreteci, PLL yongası ADF4351 ve çevresel devreden oluşur, Şekil 4'e bakın. PLL'nin referans saat kaynağı, 10 MHz frekanslı kristal osilatör TCXO'dur. Şarj pompası çıkışı CPOUT ile VCO ayarlama terminali Vtune arasına yerleştirilen harici filtre döngüsü, birinci dereceden pasif RC filtreleme kullanılarak ADIsim simülasyon yazılımı tarafından tasarlanmıştır, tasarım döngüsü bant genişliği 10 kHz'dir ve faz marjı 45 ° 'dir.

3.2 Zaman alternatifli örnekleme saati dağıtım modülü tasarımı

Modül, bir saat dağıtım yongası AD9510 ve 3 dijital gecikme hattı yongası SY89297 içerir. Gecikme hattının minimum gecikme adımı 5 ps'ye kadar düşüktür.Her saatin gecikme değerinin ince ayarıyla, PCB kablolama gecikmesinin neden olduğu saat sapması daha iyi ortadan kaldırılabilir ve alternatif örnekleme hatası azaltılabilir. Ancak çipin maksimum programlanabilir gecikmesi yalnızca 5 ns'dir, bu nedenle alternatif örnekleme yapıldığında, örnekleme saati en yüksek 250 MHz'e sabitlenir, böylece saat periyodu programlanabilir maksimum gecikmeden daha azdır. Daha düşük örnekleme oranı, FPGA'daki tamsayı örnekleme modülü tarafından örnekleme dizisinin alt örneklemesiyle elde edilir. Şekil 5, şematik bir diyagramdır.

3.3 Tetikleyici ve frekans bölme devresi tasarımı

Tasarımın basitleştirilmesi için sistemin frekans ölçümü için kullandığı tetik sinyali doğrudan ADC giriş sinyalinden alınır ve AC kuplaj sonrası DAC tarafından tetikleme seviyesi çıkışı ile karşılaştırılır.Karşılaştırma sonrası oluşan kare dalga SY89876'ya bölünür ve işlem için FPGA'ya gönderilir. Hassas frekans ölçümü. ADC giriş sinyali bir diferansiyel sinyal olduğundan, AD8009 yüksek hızlı işlemsel amplifikatör tarafından oluşturulan diferansiyel tek uçlu bir dönüştürücü, tetikleme devresinin ölçülen sinyal üzerindeki etkisini azaltmak için sinyal alımı için eklenir. Karşılaştırıcı, frekans bölücü ve FPGA arasındaki arayüz, iletim bant genişliğini artırmak ve dönüş oranını azaltmak ve analog devredeki paraziti azaltmak için LVDS seviyesi olarak tasarlanmıştır. Karşılaştırıcının çıkış aşamasının VCCO'su, LVDS seviyesine uyum sağlamak için 2,5 V güç kaynağına bağlanır. Şekil 6, devrenin şematik bir diyagramıdır.

4 Sistem performans doğrulaması

1 Vp-p genliği ve 1 MHz ila 500 MHz adımı olan bir sinüs dalgası tarama sinyali girin Zaman tabanı 500 ps / div'e ayarlanmıştır ve eşdeğer örnekleme hızı FPGA'dan Signal-TapII yazılımı aracılığıyla okunur. Çalışma bant genişliğinde ölçülen eşdeğer örnekleme oranı her zaman 160 GS / s'den biraz daha yüksektir Ondalık örnekleme modülü ile ayarlamadan sonra, dalga biçimi distorsiyonu% 1'den azdır.

1 MHz frekansı ve 1 Vp-p genliği olan bir sinüs sinyali girin.Zamanlı alternatif örnekleme modu açıldıktan sonra, gerçek zamanlı örnekleme hızı 1 GS / s'ye ulaşır, osiloskop terminalinde görüntülenen dalga şekli distorsiyonu% 1'den az ve ikinci harmonik bileşen 37 dB, tasarım gereksinimlerini karşılar.

5. Sonuç

Bu tasarımda, örnekleme saatini oluşturmak için bir kesirli frekans PLL cihazı kullanılır ve eşdeğer örnekleme, zaman alternatifli örnekleme ile başarılı bir şekilde birleştirilir ve yüksek frekanslı periyodik sinyaller işlenirken yüksek eşdeğer bir örnekleme oranı elde edilir.

Referanslar

Zhang Junyu, Ma Xubiao. Osiloskop örneklemesi için eşdeğer örnekleme sisteminin tasarımı ve uygulaması Chengdu: Çin Elektronik Bilimi ve Teknolojisi Üniversitesi, 2014.

Yi Min, Su Shujing, Ji Wei, vb. FPGA'ya dayalı yüksek hızlı zaman alternatifli örnekleme sistemi. Elektronik Teknoloji Uygulaması, 2015, 41 (1): 71-74.

Liu Ruihua, He Ming, Qiao Longfei, vb. DDS teknolojisine dayalı yüksek hızlı eşdeğer örnekleme osiloskopunun tasarımı Laboratuvar araştırması ve keşfi, 2011, 30 (9): 58-62.

ADI Şirketi Uygulama Notu: AN-501: Açıklık Belirsizliği ve ADC Sistem Performansı. (2013-11-05). Http: //ec.eepw.com.cn/center/showdocument/userid/39925/id/4157 .

Wang Ji'an, Li Zhaoji. Yüksek hızlı ve yüksek hassasiyetli ADC entegre devrelerinin araştırılması ve tasarımı Chengdu: Çin Elektronik Bilim ve Teknoloji Üniversitesi, 2008.

ADI company.AD9854 veri sayfası. (2016-11-01) .http: //www.analog.com/media/en/technical-documentation/data-sheets/AD9854.pdf.

ADI şirketi. ADF4351 veri sayfası. (2012-05-01) .http: //www.analog.com/media/cn/technical-documentation/data-sheets/ADF4351_CN.pdf.

MICROCHIP company.SY89297U veri sayfası. (2015-11-11) .http: //ww1.microchip.com/down-loads/en/DeviceDoc/sy89297u.pdf.

TI company.LMH7322 veri sayfası. (2013-03-01) .http: //www.ti.com/cn/lit/gpn/lmh7322.

-

- Apollo buzdağının ucunu açıklamayı planlıyor: Baidu, CES Asia'da otonom sürüşe hangi başarıları getirdi?

-

- "Küresel Fırtına" her türlü meteorolojik felaketin görsel-işitsel şöleni sunuyor, takdir etmek için güçlü bir kalbe ihtiyacınız var

-

- "Yunusların Memleketi" Qinzhou, konukları yüksek hızlı biletlerde% 50 indirimli olarak Hunan'dan Guangxi'ye davet ediyor

-

- Bir kediye tokat atıp "erkek" gibi et yemek ister misin? Şu "Monster Hunter World" çevresine bir göz atın