HPS ve FPGA tabanlı görüntü sıkıştırma algılama kodlama ve kod çözme sistemi

Weng Tianyang1, Zhuang Yu1, Yu Wei2, Liu Yunfei1

(1. Bilgi Bilimi ve Teknolojisi Okulu, Nanjing Ormancılık Üniversitesi, Nanjing 210037, Jiangsu; 2. Mühendislik Eğitim Merkezi, Nantong Üniversitesi, Nantong, Jiangsu 226019)

Görüntü kodlama ve yeniden yapılandırma sisteminin gerçek ihtiyaçlarına yönelik olarak, HPS ve FPGA tabanlı bir görüntü işleme sistemi tasarlanmıştır. Sistem gerçek zamanlı görüntü alma, sıkıştırma, iletim ve yeniden yapılandırma gerçekleştirir. Sistem, DE1-SoC geliştirme kartını kullanır, FPGA'da D5M kamera, SDRAM ve VGA'nın IP çekirdeklerini tasarlar, QSYS'de IP çekirdeğini bağlamak için AXI ve Avalon veriyolunu kullanır ve HPS'de (CS) görüntü sıkıştırma algılamasını gerçekleştirmek için Linux C programlamasını kullanır. ) Kodlama ve iletme, sıkıştırılmış verileri MATLAB üst bilgisayarında alma ve görüntü yeniden yapılandırmasını gerçekleştirme, FPGA kaynak kullanımını ve tasarım karmaşıklığını azaltma. Sonuçlar, sistemin rastgele doğal görüntülerin işlenmesini gerçekleştirebildiğini, görüntü sıkıştırma oranının yaklaşık% 8, PSNR'nin yaklaşık 41 dB olduğunu, uygulamanın esnek olduğunu, taşınabilirliğin güçlü olduğunu ve gerçek projelerin ihtiyaçlarını karşılayabileceğini gösteriyor.

HPS; sıkıştırılmış algılama; FPGA; görüntü işleme; PSNR

Çin Kütüphanesi Sınıflandırma Numarası: TP274.2

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.2017.05.022

Çince alıntı biçimi: Weng Tianyang, Zhuang Yu, Yu Wei, vb. HPS ve FPGA'ya Dayalı Görüntü Sıkıştırılmış Algılama Kodlama ve Kod Çözme Sistemi Elektronik Teknoloji Uygulaması, 2017, 43 (5): 90-93.

İngilizce alıntı biçimi: Weng Tianyang, Zhuang Yu, Yu Wei, ve diğerleri HPS ve FPGA tabanlı görüntü sıkıştırılmış algılama kodlama ve yeniden yapılandırma sistemi.Elektronik Tekniğin Uygulanması, 2017, 43 (5): 90-93.

0 Önsöz

Dijital görüntü, günümüz toplumundaki en önemli bilgi medyalarından biridir, ancak büyük miktardaki verileri, görüntülerin depolanmasını, iletilmesini ve işlenmesini büyük ölçüde sınırlar.Bu sorunu çözmek için görüntü sıkıştırma teknolojisi ortaya çıktı. Sıkıştırılmış Algılama (Sıkıştırılmış Algılama) teorisi, 2006 yılında ilgili araştırmalara dayanarak DONOHO D L, CANDES E ve diğerleri tarafından resmi olarak önerildi. Sıkıştırılmış algılamanın temel fikri, sinyal belirli bir ortogonal dönüşüm temelinde seyrek bir gösterime sahip olduğunda veya belirli bir alanda seyrek bir sinyale dönüştürülebildiğinde, Nyquist örnekleme oranından çok daha düşük bir örnekleme oranının kullanılabileceğidir. Örnekleme gerçekleştirilir ve orijinal sinyal, Shannon'ın örnekleme teoreminin sınırlamasını kıran, bozulma olmaksızın son derece düşük örnekleme değerinden yeniden oluşturulur. Bu teori bir kez oluşturulduktan sonra sinyal işleme, iletişim ve tıbbi görüntüleme teknolojisi alanında yüksek derecede ilgi görmüştür ve önemli bir pratik öneme sahiptir.

Sıkıştırılmış algılamanın uygulanmasına ilişkin mevcut literatürlerin çoğu, uzun bir geliştirme döngüsü, yüksek bakım maliyeti ve zayıf esnekliğe sahip donanım tarafından uygulanmaktadır. Bu makale, Terasicin DE1-SoC geliştirme platformuna dayalı bir yazılım ve donanım kombinasyonunu benimser, FPGA ve HPS, FPGA edinimi ve gösterimi kombinasyonunu kullanarak bir görüntü kamerası edinme, sıkıştırılmış algılama kodlama sıkıştırma, iletim ve yeniden yapılandırma sistemi tasarladı, HPS, karmaşık algoritmalar nedeniyle çok fazla FPGA kaynağı tüketmekten kaçınmak için işlemeyi, iş bölümünü ve işbirliğini kontrol eder. Bu sistem, hızlı işlem hızı, güçlü taşınabilirlik ve esnek uygulama özelliklerine sahiptir.

1 Sistemin genel tasarımı

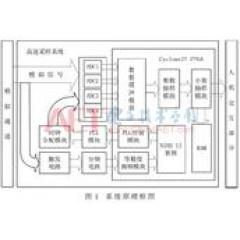

Sistemin temel blok diyagramı Şekil 1'deki gibi gösterilmiştir. Sistemin çalışma süreci şu şekildedir: Görüntü toplama modülünün FPGA'sı, I2C veriyolu aracılığıyla canlı resimleri toplamak için D5M kamerayı kontrol eder ve verileri çerçeve arabelleği aracılığıyla SDRAM'a iletir.Kare okuyucu, SDRAM'deki verileri okur ve VGA kontrolü aracılığıyla gerçek zamanlı olarak görüntülenebilir. Çekim resmi ekranda; FPGA, Avalon-st veriyolu aracılığıyla her IP çekirdeğine bağlanır ve daha sonra HPS yazılım tasarımı, görüntü verilerini sıkıştırmalı algılama kodlama yöntemiyle sıkıştırmak için kullanılır ve VIP denetleyicisi, Hafif HPS'den FPGA'ya veri yolu üzerinden dahili FPGA'ya erişmek için kullanılır. IP çekirdeği, çeşitli donanım modüllerinin çalışmasını kontrol eder; HPS'deki sıkıştırılmış veriler, gönderme ve alma için seri bağlantı noktası aracılığıyla ZigBee'ye iletilir ve son olarak, terminal ana bilgisayarı, ZigBee tarafından alınan verileri seri bağlantı noktası üzerinden alır ve görüntüyü yeniden yapılandırmak için eşlenik gradyan algoritmasını kullanır. Görüntüyü geri yükleyin. Bu sistem, görüntü elde etme, sıkıştırma, iletme ve restorasyon işlevlerini tamamen gerçekleştirmektedir. Görüntünün ayrıntılarına bağlı olarak, görüntünün geri yüklenen tepe sinyal-gürültü oranının PSNR'si de farklı olacaktır Deneyde yakalanan normal görüntüye göre, geri yüklenen PSNR yaklaşık 41 dB'dir ve sıkıştırma oranı yaklaşık% 8'dir.

2 FPGA donanım sistemi tasarımı

2.1 Görüntü alma bölümünün donanım tasarımı

Görüntü toplama sistemindeki kamera, Youjing Technology tarafından sağlanan TRDB-D5M modülünü kullanır.D5M IP çekirdek tasarım bölümü, I2C yapılandırma modülü, CMOS yakalama kontrol modülü ve Bayer2RGB renk alanı dönüştürme modülünden oluşur. Blok diyagram Şekil 2'de gösterilmiştir. .

I2C veriyolu başlatma sinyalini gönderdiğinde, veri hattı SDATA, adresleme baytları ve veri baytları dahil olmak üzere verileri iletmeye başlar. CMOS yakalama kontrolü, 3 senkronizasyon sinyali tarafından kontrol edilen orijinal veri akışını yakalar.FVAL (çerçeve geçerli sinyal) ve LVAL (hat geçerli sinyal) her ikisi de yüksek seviyeye ayarlandığında, her piksel saat sinyal darbesine bir bit veri eşlik eder Çıktı.

Görüntü toplama bölümünde, Çerçeve Tampon IP çekirdek kısmı da eklenir Bu tamponun ana işlevi, D5M'nin çıkışı ile SDRAM'deki okuma arasındaki veri hızı uyumsuzluğu sorununu çözmektir. Bu arabellek eksikse, SDRAM'deki veriler paket kaybına ve eksik verilere maruz kalacaktır.

2.2 Görüntü görüntüleme parçasının donanım tasarımı

Görüntü görüntüleme bölümü temel olarak iki işlevi yerine getirir: biri gerçek zamanlı olarak çekilen görüntülerin görüntülenmesi, diğeri ise yakalanan görüntülerin görüntülenmesi. SDRAM'a erişirken, farklı depolama alanları bu iki görüntü modu arasında geçiş yapar. Çerçeve okuyucu 1, SDRAM'daki verileri okur ve gerçek zamanlı yakalanan görüntüyü gösteren VGA1'e iletir ve görüntülenen görüntü çözünürlüğü 640 × 480'dir. Çerçeve okuyucu 2 tarafından okunan veriler ve arka plan oluşturucudan gelen veriler alfa karıştırıcısına gönderilir, böylece VGA2'de görüntülenen sonuç iki katmana sahip olur, ilk katman 1280 × 1024 çözünürlüklü renk çubuğu arka planıdır. Tüm görüntü ekranını kaplayan ikinci katman, görüntü ekranının sol üst köşesinde bulunan yakalanan görüntüdür. Yakalama komutunu aldıktan sonra ekranı değiştirin.

2.3 Qsys sistem yapısı

SoC FPGA sisteminin tasarımı, sistem donanımının mimarisini tanımlamalıdır. Oluşturmak için Qaurtus II entegre SoC / SOPC tasarım aracı Qsys'i kullanın Qsys'de, HPS ve FPGA çevre birimlerinin planlanması gerekir. HPS'nin çevre birimleri geliştirme panosunun donanımına göre ayarlanırken, FPGA çevre birimlerini ayarlamanın yolu IP çekirdeği eklemektir.Burada, özel gereksinimleri karşılamak için kendinden tanımlı bir IP modülü eklemeniz ve son olarak donanım ve yazılım geliştirme için ilgili gereksinimleri üretmeniz gerekir. Dosyalar kapsamlı bir şekilde derlenmiştir.

FPGA-HPS ve HPS-FPGA Köprüleri, FPGA ile HPS arasında geniş bant ve yüksek hızlı aktarım kanallarıdır. Hafif HPS-FPGA daha düşük hızlı bir kontrol kanalıdır.Bu tasarım, bu kanalı HPS ve FPGA arasında veri aktarımı için kullanacaktır. Bu tasarım için gerekli donanım çevre birimleri ARM sert çekirdekli işlemci, SDRAM, UART seri bağlantı noktası, faz kilitli döngü, çerçeve arabelleği, 2 çerçeve okuyucu, 2 VGA, Avalon-st veriyolu, arka plan oluşturucu, özel D5M içerir IP çekirdeği, düğmeler, anahtarlar, alfa karıştırıcı vb. Daha sonra saat, sıfırlama, CPU veri yolu ve talimat veriyolu ile modül arasındaki bağlantı dahil olmak üzere her modül arasında bağlantı kurun. Qsys sisteminin genel donanım konfigürasyonu Şekil 3'te gösterilmektedir.

3 HPS yazılım sistemi tasarımı

3.1 Sıkıştırılmış Algılama Kodlaması

Sıkıştırılmış algılama 2006 gibi erken bir tarihte önerildi. Sıkıştırılmış algılamanın en büyük atılımı, örnekleme için Nyquist teoremine dayanmamasıdır.Belirli bir dönüşüm alanında seyrek olması ve ideal olarak sinyal bilgilerinin çoğunu çok düşük bir örnekleme hızında tutması gerekir. Yeniden yapılandırma sırasında, bir optimizasyon problemi çözülerek sıkıştırılmış verilerden orijinal sinyal yeniden oluşturulabilir. Bu tasarımda, sıkıştırmalı kodlama esas olarak üç bölüme ayrılmıştır: hızlı DCT dönüşümü, niceleme ve Z taramasının örnekleme yöntemleri.

Hızlı DCT dönüşümü seyrek dönüşüm için kullanılır.Kodlamadan önce, RGB görüntüsü YCbCr görüntüsüne dönüştürülür ve ardından görüntü soldan sağa ve yukarıdan aşağıya sırayla 8 × 8 veri bloklarına bölünür. RGB-YCbCr'nin dönüşüm formülü aşağıdaki gibidir:

Sonraki kodlamayı kolaylaştırmak için, Y sinyali bileşeni 128'den çıkarılır ve. Çünkü parlaklık sinyali, krominans sinyalinden daha önemlidir. DCT dönüşümünün gerçekleştirilme süreci şu şekildedir: Önce görüntüyü 8 × 8 veri bloklarına bölün ve ardından FDCT gerçekleştirin. DCT dönüşümünden sonra, görüntü verileri uzamsal alandan frekans alanına dönüştürülür. 8 × 8 matrisinin sol üst köşesi yüksek frekanslı bileşendir ve sağ alt köşesi düşük frekanslı bileşendir. Niceleme, 64 DCT katsayılarının küçültülmesi ve yuvarlanması işlemidir. Görsel efekt üzerinde çok az etkisi olan ve verileri sıkıştırma amacına ulaşan bazı bilgileri atar.

Veri matrisi DCT dönüşümünden geçtikten sonra, uzaysal alandan frekans alanına dönüştürülür ve frekans, sol üst köşeden sağ alt köşeye doğru kademeli olarak artar. Nicemlemeden sonra, sıfır olmayan sayılar genellikle matrisin sol üst köşesinde yoğunlaşır ve 0 sağ alt köşede yoğunlaşır ve DC bileşeni AC bileşeninden çok daha büyüktür. Zig-Zag tarama dizisi, sol üst köşeden başlayıp sağ alt köşeye zikzak taramadan başlayarak nicelenmiş katsayıları depolar, iki boyutlu dizi tek boyutlu bir diziye dönüştürülür ve sıfır değerli bileşenler sürekli görünür.Tarama yolu Şekil 4'te gösterilmiştir. Son olarak, sıkıştırmalı kodlama için sıkıştırılmış algılama kullanılır.

3.2 VIP kontrol tasarımı

HPS'de VIP kontrolünün ana işlevi, IP çekirdeğinin parametrelerini ayarlamak ve IP çekirdeğinin çalışma durumunu kontrol etmektir. VIP kontrol kısmının tasarım akış şeması Şekil 5'te gösterilmektedir.

IP çekirdeğinin başlangıç durumu, D5M, çerçeve arabelleği, çerçeve okuyucu 1 ve VGA denetleyici 1'i çalışmak üzere ayarlamak ve çerçeve okuma boyutunu 640 × 480 olarak ayarlamaktır. Ana bilgisayardan yakalama komutunu aldıktan sonra, anahtarı girin Durum, yukarıdaki IP çekirdeğini kapatın, çerçeve okuyucu 2'yi, arka plan oluşturucuyu, alfa karıştırıcıyı, VGA denetleyici 2'yi başlatın ve çerçeve okuma boyutunu 640 × 480 olarak ayarlayın. Verileri ana bilgisayardan sıkıştırmak için komut aldıktan sonra, sıkıştırılmış algılama sıkıştırma kodlama modülü veri sıkıştırması için harekete geçirilecektir Tamamlandıktan sonra, seri bağlantı noktası verileri ZigBee yoluyla terminale gönderecektir.

4 Sistem hata ayıklama ve doğrulama

Bu tasarımda, ana bilgisayar arayüzü MATLAB aracılığıyla tasarlanmıştır.Arayüz, parametrelerin ayarlanmasını ve yakalama komutlarının, sıkıştırma komutlarının ve kurtarma komutu düğmelerinin tasarımını içerir. Yakalama ve sıkıştırma komutları, almak için seri bağlantı noktası aracılığıyla HPS'ye gönderilir ve VIP denetleyicisi, Bir dizi eylem ve yeniden yapılandırma talimatı, geri yüklenen görüntüyü yeniden oluşturmak için MATLAB'da eşlenik gradyan algoritmasını çalıştırmak ve son olarak görüntüyü PC'ye kaydetmek içindir. Üst bilgisayar arayüzü Şekil 6'da gösterilmektedir.

Bu tasarım, DE1-SoC geliştirme kartını kullanır ve Quartus15.0 geliştirme platformundaki her mantık modülünü tasarlamak için Verilog HDL'yi kullanır. Bu görüntü işleme modülünün, Tablo 1'de gösterildiği gibi FPGA içindeki ana mantık kaynaklarını işgal ettiği doğrulanmıştır.

Şekil 1'deki sistem blok şemasına göre test edin ve doğrulayın. Sistem kararlı ve güvenilir bir performansa ve güçlü taşınabilirliğe sahiptir.Bilgisayar terminali ana bilgisayar yazılımının karşılık gelen çalışması altında, kamera çekimi, yakalama, veri sıkıştırma ve görüntüleri geri yükleme işlevlerini gerçekleştirebilir ve terminalde sağlam olan monitörde çekim resmini net bir şekilde görüntüleyebilir. Orijinal görüntü ve sıkıştırmadan sonra geri yüklenen görüntü yerel olarak kaydedilir. Şekil 7, görüntü sıkıştırma ve yeniden yapılandırmanın bir karşılaştırma diyagramıdır. Şekil 7 (a), kamera tarafından alınan orijinal görüntüdür ve Şekil 7 (b), bu sistem tarafından sıkıştırılan ve restore edilen görüntüdür. Saksı yapraklarındaki solmuş alanlar, sıkıştırılmış algılama ile restore edildikten sonra hala açıkça görülebilir. . Karşılaştırma tablosundan bu tasarım şemasının daha iyi sonuçlar elde ettiği ve görüntü edinme, sıkıştırma, iletme ve yeniden yapılandırmanın gerçekten ve sistematik olarak gerçekleştirildiği görülebilir.

5. Sonuç

Bu makale, görüntü elde etme, görüntü işleme ve görüntü aktarımını entegre eden bir sistemi incelemektedir.Yazılım ve donanımı birleştiren bir tasarım şeması benimsemektedir.Ana platform olarak DE1-SoC geliştirme kartı ile görüntü elde etme, Depolama ve sıkıştırılmış algılama kodlama işlevi. PC tarafında, ana bilgisayar arayüzünü tasarlamak ve nihayet arayüzde gerçek zamanlı olarak görüntülenebilen görüntü verilerinin kod çözümünü tamamlamak için MATLAB kullanın. Sistem tarafından geri kazanılan görüntünün en yüksek sinyal-gürültü oranı yaklaşık 41 dB ve sıkıştırma oranı% 8'dir Esnek uygulama, güçlü taşınabilirlik ve güçlü uygulanabilirliğe sahiptir ve görüntü aktarımı için pratik önemi vardır.

Referanslar

DONOHO D L. Sıkıştırılmış algılama IEEE Trans. On Information Theory, 2006, 52 (4): 1289-1306.

CANDES E, ROMBERG J, TAO T. Sağlam belirsizlik ilkeleri: Oldukça eksik frekans bilgisinden kesin sinyal yeniden oluşturma IEEE Aktarım Bilgi Teorisi, 2006, 52 (4): 489-509.

CANDES E J. Compressive sampling. Proc. Of International Congress of Mathematicians. Madrid, İspanya, 2006: 1433-1452.

Pan Rong, Liu Yu, Hou Zhengxin, vb. Yerel DCT Katsayılarına Dayalı Görüntü Sıkıştırılmış Algılama Kodlama ve Yeniden Yapılandırma Acta Automatica Sinica, 2011 (6): 674-681.

Jin Jian, Gu Yuantao, Mei Shunliang Sıkıştırılmış örnekleme teknolojisi ve uygulaması Elektronik ve Bilgi Teknolojileri Dergisi, 2010, 32 (2): 470-475.

Liu Jiying, Zhu Jubo. Düşük veri hızlı radar örnekleme ve sıkıştırılmış algılamaya dayalı görüntüleme yöntemi Bilgisayar Mühendisliği ve Bilimi, 2012, 24 (5): 646-651.

Ma Lingling, Liu Yunfei, Gu Minming, vb Uzaktan Dijital Görüntü İzleme Sisteminin FPGA Uygulaması Elektronik Teknoloji Uygulaması, 2015, 39 (6): 70-73.

Yang Yu, Jia Yongxing, Rong Chuanzhen.STM32F407'ye dayalı görüntü alma ve aktarım sisteminin tasarımı ve uygulaması. Mikrobilgisayar ve Uygulama, 2015, 34 (8): 26-28.

Nie Yongjun, Xu Guanghui, Zheng Guojian ve diğerleri.Altera SoC FPGA'ya dayalı görüntü edinme sisteminin tasarımı.Tek çipli mikro bilgisayar ve gömülü sistem uygulaması, 2016 (4): 56-59.

CANDES E J. Sınırlandırılmış izometri özelliği ve sıkıştırılmış algılama için etkileri Comptes Rendus Mathematique, 2008, 346 (9-10): 589-692.

Jiao Licheng, Yang Shuyuan, Liu Fang, vb. Sıkıştırılmış Algılamanın İncelenmesi ve Beklentisi Açta Electronica Sinica, 2011 (7): 1651-1662.

Pan Rong. Yerel DCT katsayılarına dayalı olarak görüntü sıkıştırma algılama kodlama ve yeniden yapılandırma Açta Automatica Sinica, 2011, 37 (6): 674-681.

-

- "Küresel Fırtına" her türlü meteorolojik felaketin görsel-işitsel şöleni sunuyor, takdir etmek için güçlü bir kalbe ihtiyacınız var

-

- "Yunusların Memleketi" Qinzhou, konukları yüksek hızlı biletlerde% 50 indirimli olarak Hunan'dan Guangxi'ye davet ediyor

-

- Bir kediye tokat atıp "erkek" gibi et yemek ister misin? Şu "Monster Hunter World" çevresine bir göz atın

-

- Hem dahili hem de harici onarımlar için pahalı değildir. 4 bin yuan gradyan uygun maliyetli makineler arasından seçim yapabilirsiniz