Kapaksız LDO yapısını kullanan bir yonga üstü kapasitans tahmin yöntemi

Yarı iletken endüstrisinin sürekli gelişmesiyle birlikte, SOC yongalarının işleme işlevleri artmaya devam ediyor ve SOC yongalarının daha zengin bir çevresel kontrol arabirimine ve iletişim arabirimine sahip olmasını gerektiriyor.Paketleme, kalıplar ve maliyet gibi kısıtlamalar nedeniyle yonga yalnızca sınırlı pim kaynaklarına sahiptir. Güç ve toprak pimleri, pim kaynaklarının önemli bir bölümünü kaplar. STM32 serisi yongalar gibi, yonga üzerinde LDO yöntemini kullanmak bazı güç pinlerinden tasarruf edecek ve pin kaynaklarını artıracaktır.

Güç uygulamaları ve finansal işlemler gibi endüstriyel kontrol alanlarında, bilgi güvenliğini sağlayan şifreleme çipleri geniş bir uygulama alanına sahiptir. Bu tür bir yonga için, çekirdek güç kaynağı, temel güvenlik şifreleme algoritmasının, veri güvenliğine büyük bir tehdit oluşturan güce ve yere yapılan müdahaleci saldırılardan korunmasını sağlamak için dahili güç kaynağını kullanmalıdır. Bu nedenle, çekirdeğe güç sağlamak için yonga üzerinde LDO yöntemi kullanılmalıdır.

Dijital çekirdeğe güç veren çip üzerindeki LDO'nun yük özellikleri aşağıdaki gibidir: (1) Ortalama güç tüketimi, dijital devrenin çalışma frekansı ile orantılıdır; (2) En yüksek güç tüketimi, saat çevirme kenarında meydana gelir ve güç tüketimi, diğer aşamalarda çok küçüktür ve güç tüketimi, Nanosaniye mertebesinde. Bu nedenle, yonga üzerindeki LDO'nun nanosaniye seviyesindeki yük değişikliklerine yanıt verme kabiliyetine sahip olması gerekir ve bant genişliğinin gigahertz'e kadar ulaşması gerekir ki bu güç tüketimi ve alan kısıtlamaları altında elde edilmesi zordur ve yeterli yonga üstü filtre kapasitörleri paralel bağlanmalıdır. Tasarım sürecinde dijital kod PR için dondurulduktan sonra dijital devrenin güç tüketimi simüle edilir ve ardından çip üstü filtre kondansatörünün boyutu belirlenir ve filtre kondansatörü takıldıktan sonra müteakip doğrulama işlemi tamamlanır. Önceki tasarım deneyimine göre, çip üzerindeki filtre kapasitörleri genellikle çip alanının% 10 ila% 20'sini kaplayan birkaç nanofarad seviyesine ulaşır.Böyle geniş bir alan, çipin düzenini değiştirecek ve tasarım sürecinin yeniden yinelenmesini sağlayacaktır. Ciddi durumlarda, birkaç aylık bir gecikmeye neden olacak ve bu da projenin kontrol edilebilirliği üzerinde büyük bir etkiye sahip olacaktır.

Yukarıdaki sorunlara yanıt olarak, bu makale LDO'ları kullanan yonga üstü kapasitörlerin bir tahmin yöntemi önermektedir.Projenin kod ön ucunun tasarım aşamasında güç tüketimi analizi ve tahmin yöntemleri tanıtılmış ve yonga üstü filtre kapasitörünün boyutu önceden değerlendirilmiş ve kapasitör çip düzenine dahil edilmiştir. , Yukarıdaki yinelemeyi önlemek ve proje döngüsünü azaltmak için. Bu yöntem kullanılarak mükemmel çip performansına sahip bir çip başarıyla tasarlandı.

1 Çip üstü LDO ve filtre kapasitörünün çalışma prensibi

Şekil 1, bir LDO ana devresini ve bir filtre kapasitörünü Cdcp'yi gösterir; burada Cdcp, çip üstü kapasitördür ve p2, çipin IOPAD'ına çekilmeyen ve doğrudan çip çekirdeğine güç sağlayan çıkış voltajıdır. Bu LDO'nun çıkış voltajı:

Bunların arasında VREF, çip üzerinde referans voltaj kaynağıdır. Yük, dijital devrenin güç tüketimidir ve tipik dalga şekli Şekil 2'de gösterilmektedir.

Çip üzerinde LDO üzerinde p1, p2, p3 kutupları vardır, bu da LDO'nun tepki hızını sınırlar. Bu kutupların etkisi hesaba katıldığında, op amfinin nanosaniye aksaklıklara yanıt verebilmesi için 10 GHz GBW ve 10 GV / s SR'ye ulaşması gerekmektedir.Bu performansa ulaşmak için op amfinin güç tüketimi dayanılmazdır. Bu nedenle, nanosaniye seviyesinde geçici güç tüketimini işlemek için bir çip üzerinde filtre kapasitörüne ihtiyaç vardır ve çip üzerinde LDO, yanıt hızında yüzlerce nanosaniye sırasındaki ortalama güç tüketimi değişikliğini işlemekten sorumludur. Aşağıda özellikle tasarım ölçeğine, uygulanan işlem kitaplığına, devre çalışma frekansına ve tasarımın ön aşamasındaki diğer bilgilere dayalı olarak güç artışlarına yanıt olarak yonga üstü filtre kapasitörünün tasarım süreci açıklanmaktadır.Aynı zamanda, işleme göre yonga düzeni ve tasarımı verilmektedir. Test sonuçları.

2 Çip üstü filtre kondansatörünün tahmin yöntemi

Normal tasarım sürecindeki güç tüketim istatistikleri yöntemine göre, çip üstü filtre kondansatörü üzerinde en büyük etkiye sahip olan dijital devrenin güç tüketimi, ağırlıklı olarak entegre dijital devrenin güç tüketimini ve belleğin güç tüketimini kapsamaktadır.Bu nedenle iki bölüm ayrı ayrı açıklanmaktadır.

2.1 Entegre dijital devre güç tüketimi

Dijital kod tasarımı dondurulduktan sonra dijital devrenin geçit sayısının GateCount değeri, çipin entegre sonucuna göre tahmin edilebilir. Dijital kodla tasarlanan işlem kütüphanesini araştırarak, standart birimin güç tüketimi verileri bulunur Genel format Şekil 3'te gösterilmektedir ve bunun temsili anlamı, farklı giriş sinyali dönüştürme sürelerine karşılık gelen standart birimin dahili güç tüketimidir.

Şunu göz önünde bulundurarak: güç P = U × I, şarj miktarı Q = I × t, güç tüketimi W = P × t = U × I × t, şarj türetilebilir: Q = W / U.

Şekil 3'teki verilere bakarak, saat kenarı her döndüğünde tek bir standart hücrenin neden olduğu dahili yük Qinternal'daki değişikliği doğrudan hesaplamak mümkündür.

Şekil 3'teki sonuçlara göre, en kısa giriş sinyali dönüştürme süresi ve en küçük yük kapasitansı ile, saat kenarı çevirme başına tüketilen şarj miktarı yaklaşık 0,001463 p / 1,2 = 1,216 fC'dir.

Entegre dijital devrenin güç tüketiminin bir diğer kısmı, çıkış her değiştiğinde dijital devrenin güç tüketimi olarak tanımlanan anahtarlama güç tüketimidir. Bu doğrudan yük kapasitansının boyutuyla ilgilidir. Hesaplama formülü:

Dijital bir devrenin anahtarlama güç tüketimini tahmin etmek için, çalışma frekansını, çalışma voltajını ve yük kapasitansını bilmeniz gerekir. Çalışma frekansı ve çalışma voltajı bilinmektedir ve yük kapasitansının tahmin edilmesi gerekmektedir.

Tek bir standart birimin çıkış yükü esas olarak iki bölümden oluşur, bir bölüm sonraki aşamaya bağlanan kapıların sayısıdır (Fanout) ve diğer bölüm bağlantının parazitik kapasitansıdır. Standart hücrenin giriş kapasitansı, dijital kod tasarım işlem kitaplığında bulunabilir Şekil 4'te gösterildiği gibi, giriş kapasitansı yaklaşık 0.9 fF'dir Fanout = 10 ise, tek bir standart hücrenin çıkış yükü 9 fF'dir.

Telin parazitik kapasitansı, telin uzunluğu ile ilgilidir ve telin yük kapasitansı, Şekil 4'te gösterildiği gibi işlem kitaplığındaki veriler aranarak elde edilebilir. Bu örnekte, 1 milyon geçitlik bir ölçek verilmiştir ve birim kapasitans 0.1382 fF'dir.Fan çıkışı 4 ise, yük kapasitansı 0.1382 fF × 70 = 9.674 fF'dir.

Şekil 4'te verilen ilgili bilgilere göre, dijital devrenin entegre sonucu ile tahmin edilen ortalama yayılma, yonganın kapı sayısı, yonganın çevirme hızı ve diğer bilgiler dijital devrenin anahtarlama güç tüketimini tahmin etmek için kullanılabilir ve böylece saat artışı elde edilebilir. Düşen kenar tarafından tüketilen Qswitch şarj miktarı artı standart ünitenin dahili dönüşü tarafından tüketilen Qinternal şarj miktarı, dijital devre tarafından tüketilen Qdig = Qswitch + Qinternal toplam şarj miktarını elde eder.

Projenin ilk aşamasında dijital devrenin ölçeğinin 600.000 kapı olacağı tahmin edilmektedir.Dijital araçların istatistiklerine göre ortalama çıkış 2, dijital devrenin devir hızı yaklaşık% 25'dir. Yukarıdaki yönteme göre, ortalama bağlantı kapasitansı Cwire = 3.455 fF ve yük kapısı devresinin giriş kapasitansı 1 fF × 2 = 2 fF'dir.

Bu nedenle, Qinternal ~ 1.216 fC × 600.000 × 25% = 0.185 nC; Qswitch ~ (3.255 fF + 2 fF) × 1.2 × 600000 ×% 25 = 0.98 nC, her saat dönüşü için Q = 1.165 nC şarj miktarı gereklidir.

2.2 Bellek devresi güç tüketiminin tahmini

Şekil 5, tipik bir RAM belleğinin güç tüketimi verileridir ve genellikle ortalama güç tüketimi biçiminde verilir.Aslında, RAM'in güç tüketimi davranışı, dijital devrelerin güç tüketimi davranışıyla tutarlıdır, bu nedenle her çevirme için tüketilen şarj miktarına dönüştürülmesi gerekir. .

Yazma modunda, RAM'in maksimum güç tüketimi 37 A / MHz'ye ulaşır.Yazma modunda, RAM yaklaşık olarak tüm güç tüketiminin saatin yükselen kenarında gerçekleştiğini ve bu aşamada çekilen gücün Qram = 37 A / MHz × 10-6Hz × 1 saniye = 37 pC.

RAM'in okuma modunda güç tüketimi, yazma modunda RAM'in güç tüketiminden daha azdır ve aynı saat kenarının okuma ve yazma modları aynı anda gerçekleşmeyeceğinden, okuma ve yazma modundaki güç bilgileri artık hesaplanmaz.

2.3 Çip üstü filtre kapasitörünün tahmini

Saat dönüşü başına dijital devre tarafından tüketilen şarj miktarı Qdig = 1.165 nC'dir ve her saat dönüşü için yonga üzerinde bellek RAM tarafından tüketilen şarj miktarı Qram = 37 pC'dir, bu nedenle saat dönüşü başına dijital devre tarafından tüketilen toplam şarj miktarı Qtot = 1.165 nC + 37'dir pF = 1.202 nC.

Nihai Signoff standardına göre, geçici voltajın Vdropu% 20 × Vnorm'dur, bu nedenle toplam yonga üstü filtre kapasitörünün hesaplanması aşağıdaki gibidir:

Bu nedenle, projenin ilk aşamasında, çip dışı kapasitörler olmayan bir LDO yapısına sahip bir çip üzerinde sistem için çip üzerinde filtre kapasitörünün en az 5 nF'ye ihtiyacı olduğu tahmin edilebilir. Bu kapasitörün alanı oldukça fazladır ve 5 nF kapasitörün konumu çipin yerleşim aşamasında eklenmelidir; ayrıca filtre kapasitörünün boyutu belirlendiğinden, LDO'nun performansı optimize edilebilir ve tasarlanabilir ki bu da oldukça ileri düzeydedir. LDO geliştirme süreci.

3 Örnekte çip üzerinde filtre kapasitör tahmin yönteminin uygulanması

Yukarıdaki yöntem, bir SOC yongasında başarıyla uygulandı, projenin başlangıcında dijital devre tasarımı ile yakın işbirliği yaptı ve erken sonuçlara dayanarak, gerekli yonga üstü filtre kapasitör boyutunun 5 nF olduğu tahmin edildi ve bu, yonga üzerindeki LDO'yu tamamlamak için bir yük olarak kullanıldı Devre tasarım çalışması tamamlanır ve ardından Şekil 6'da gösterildiği gibi tüm çip yerleşim çalışması tamamlanır.

Dijital ve arka uç işlemleri bittikten sonra, güç kaynağı voltajını doğrulamak için araç tarafından çıkarılan güç tüketimi bilgilerini kullanın. Şekil 7'de gösterildiği gibi, en büyük güç tüketimi artışını çıkarın, güç tüketimi artışının şarj miktarını analiz edin ve güç kaynağında meydana gelen voltaj düşüşünün gereksinimleri karşılayıp karşılamadığını doğrulayın. Bu artış altında tüketilen şarj miktarı 0,84 nC'dir ve 5 nF kapasitörün neden olduğu voltaj düşüşü% 16,8 olup tasarım gereksinimlerini karşılar.

Şekil 8, çip üzerinde LDO'dan sonra tüm çipin güç kaynağı voltajının dalga şeklini ve dijital devre tam hızda çalışırken filtre kondansatörünü göstermektedir.Çipin tasarım kurallarını karşılayan her durumda giriş voltajı değişiminin% -18.3 olarak kontrol edildiği görülebilir ve Kondansatör boyutu tasarlanmamıştır ve çok fazla yonga alanı kaplamaz.

Bu tasarım sürecini kullanarak, arka uç düzeni değiştirilmemiştir ve proje, diğer benzer projelere kıyasla yaklaşık 2 aylık tasarım süresinden tasarruf sağlar.

4 Çip testi

Bu yonga, 40 nm'lik bir süreç altında bantlanmıştır ve yonganın düzeni Şekil 6'da gösterilmektedir. Çip test edilmiştir ve tüm çalışma ortamlarında normal olarak çalışır Şekil 9, çipin güç kaynağı voltajının test sonuçlarını gösterir.Güç kaynağı voltajının kararlı çalıştığı görülebilir.Güç kaynağı dalgalanması, hafif ve ağır yüklerin anahtarlanması altında ± 60 mV içindedir. Tasarım gereksinimlerini karşılayın.

5. Sonuç

Entegre devre SOC yongasının PIN pin kaynaklarının sınırlandırılması ve güvenlik saldırısı korumasının dikkate alınması açısından, çekirdeğe güç sağlamak için bir yonga üzerinde LDO ve bir yonga üzerinde filtre kapasitörünün kullanılması gerekmektedir. Bu yazıda verilen tasarım süreci ve tahmin yöntemi ile çip tasarımı ve dijital devre tasarımının ilk aşamasında eş zamanlı olarak çip üzerinde filtre kondansatörünün boyutu tahmin edilebilir ve aynı anda LDO tasarım optimizasyonu tamamlanabilir ve çip yerleşim tasarımına önceden başlanabilir. , Daha sonraki dönemde aşırı kapasitans nedeniyle tekrarlanan yinelemelerin sayısını önlemek ve proje geliştirme döngüsünü kaydetmek. Tasarım süreci 40 nm'lik bir süreç altında başarıyla uygulandı ve çip testi sonuçları tasarım beklentilerini tam olarak karşıladı, bu da tasarım sürecinin güvenilir ve pratik olduğunu ve değerlendirme yönteminin doğru olduğunu ve çip dışı filtre kapasitörleri olmadan entegre devre çiplerinin tasarımına genişletilebilir.

Referanslar

ST Microelectronics Company.STM32 veri sayfası. 2015.

Zhang Haifeng, Yu Yanyan. Güç saldırısı ve hata saldırısına karşı blok şifreleme algoritması yöntemi. Elektronik Teknoloji Uygulaması, 2015, 41 (5): 50-52.

Philip Allen, Douglas Holberg. CMOS analog entegre devre tasarımı. Beijing: Electronics Industry Press, 2011.

Razawi Analog CMOS entegre devresinin tasarımı Xi'an: Xi'an Jiaotong University Press, 2003.

yazar bilgileri:

He Yang, Ma Yongwang, Hou Jiali, Wang Xiaoman, Hu Yi, Feng Xi, Tang Xiaoke

(1. Güç Yongası Tasarım ve Analiz Laboratuvarı, Çin Devlet Grid Corporation'ın Anahtar Laboratuvarı, Beijing Zhixin Microelectronics Technology Co., Ltd., Beijing 100192;

2. Beijing Zhixin Microelectronics Technology Co., Ltd. Beijing Electric Power Yüksek Güvenilirlik Entegre Devre Tasarımı Mühendisliği Teknolojisi Araştırma Merkezi, Beijing 100192)

-

- Çin Yeni Yılı dekompresyon eseri "Ondokuzuncu Nesil Atalar", tüm insanların ihtiyaçlarını karşılamak için deyim posterlerini çıkmaz sokak olmadan 360 derece sergiliyor

-

- Mobile Evening News: MWC yeni ürünü + 5G planlandığı gibi geliyor, Apple, APP geçiş araçlarını mükemmelleştiriyor

-

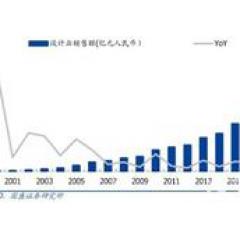

- `` Endüstri Sıcak Noktaları '' 2018'de yerli IC tasarım endüstrisinin hızlı büyümesi, büyüme oranı% 30'u aştı