Yüksek hassasiyetli yankı veri toplama modülünün tasarımı

Wu Song

(Çin Gemi İnşa Endüstrisi Kurumu'nun 726. Araştırma Enstitüsü, Şangay 201100)

- 24-bit analogdan dijitale dönüştürücüye dayalı bir edinim sistemi tanıtıldı.Sistem, 0-60 dB'lik ayarlanabilir bir kazanç, birkaç mikrovolttan onlarca milivolta kadar yüksek hassasiyetli giriş sinyalleri edinimi ve birden çok frekanslı filtre çıkışı sağlar. ; Analogdan dijitale dönüştürücünün yapılandırmasını, kontrolünü ve veri okumasını gerçekleştirmek için FPGA kullanın, toplanan büyük miktarda veri harici Flash'ta arabelleğe alınır, DSP tarafından okunur ve FIR filtreleme ile işlenir ve ardından yankı tanımlaması için RS422 arabirimi aracılığıyla ana bilgisayara gönderilir.

- tipi, yüksek hassasiyetli edinim, FPGA, DSP

Elektronik teknolojinin hızla gelişmesi ve uygulama alanlarının sürekli genişlemesi ile analog dünya ile dijital dünyayı birbirine bağlayan analogdan dijitale dönüştürücü son derece önemlidir.Aynı zamanda analogdan dijitale dönüştürücünün performansına daha yüksek gereksinimler getirilir. Yankı sinyali çok zayıftır, en azından birkaç mikrovolttur ve çeşitli parazit sinyalleri ile karıştırılır.Girişim sinyallerinden etkili sinyalleri tespit etmek ve sistemin yüksek hassasiyet ve yanıt süresi gereksinimlerini karşılamak için, bu makale - temelli bir tür sunar. Yüksek hassasiyetli ADC'nin toplama modülü, sistemin performans gereksinimlerini karşılar.

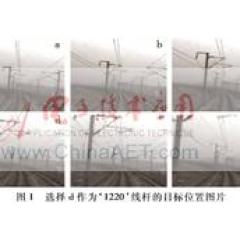

1 Veri toplama modülünün genel yapısı

Edinim modülünün blok diyagramı Şekil 1'de gösterilmektedir. Temelde değişken kazanç amplifikatörü, analogdan dijitale dönüştürücü, FPGA, DSP, Flash, 422 arayüzü ve CAN arayüzünden oluşur. Transdüser tarafından alınan zayıf sinyal, amplifikatör tarafından AD analog giriş aralığı içindeki diferansiyel giriş sinyaline yükseltilir; analogdan dijitale dönüştürücü, değişken kazanç amplifikatörünün diferansiyel sinyal çıkışını bir dijital sinyale dönüştürür ve tam filtrelemeden sonra dijital sinyali çıkarır; FPGA Analogdan dijitale dönüştürücünün okuma ve yazma zamanlamasını kontrol edin, dönüştürülen verileri okuyun ve arabelleğe alma ve işlemeyi tamamlayın ve ardından verileri harici Flash bellekte saklayın; DSP, AD'nin örnekleme oranını FPGA aracılığıyla yapılandırır, örnekleme süresini kontrol eder ve değişken kazanç yükselticisinin kazancını ayarlar , Filtreleme için Flash verilerini okuyun ve ardından verileri iletişim arabirimi aracılığıyla ana bilgisayara gönderin.

2 Sistem donanımı tasarımı

2.1 Ana bileşenlerin seçimi

Bu makalede tanıtılan yankı sinyali, deniz tabanına yönlendirilen ve deniz tabanına ulaştıktan sonra geri dönen verici dönüştürücünün oluşturduğu çeşitli seslerle karıştırılmış bir ses dalgası sinyalidir.Alıcı dönüştürücü, yankı sinyalini belirli bir sabit frekansın yakınında voltaja dönüştürür. sinyal. Farklı su derinliklerinin farklı ses dalgaları yayması gerektiğinden, yankının gücü de farklıdır.Buna dönüştürülen voltaj sinyali birkaç mikrovolttan onlarca milivolta kadar değişir, bu nedenle amplifikatör devresinin düşük gürültü ve değişken olması gerekir. Kazanç. AD8338, tamamen diferansiyel sinyal yolu, düşük güç tüketimi, düşük gürültü ve LF ~ 18 MHz frekans bandında doğru kazanç gerektiren uygulamalar için uygun bir değişken kazanç amplifikatörüdür (VGA). Temel kazanç işlevi doğrusaldır ve nominal kazanç aralığı şöyledir: 0 dB ila 80 dB'dir; nominal kazanç aralığı, kazanç pini üzerindeki 0,1 V ila 1,1 V kontrol voltajına karşılık gelir ve kazanç ile frekans arasındaki ilişki Şekil 2'de gösterilmiştir.

AD8338 yalnızca birkaç ayrı bileşene ihtiyaç duyar ve kullanıcılar, kendi uygulama gereksinimlerini karşılamak için aygıtın kazanımını, bant genişliğini, giriş empedansını ve gürültü performansını özelleştirebilir. Cihaz, son derece yüksek enerji verimliliğine sahip olan ve yalnızca 3 mA kadar düşük bir durgun akım tüketen, 3,0 V ila 5,0 V arasında değişen tek bir güç kaynağı kullanır.

AD7760, geniş giriş bant genişliği ve yüksek çözünürlük özelliklerini birleştiren, yüksek performanslı, 24 bitlik bir - analogdan dijitale dönüştürücüdür. 2,5 MHz'lik bir frekansta veri çıkışı yapılırken, sinyal-gürültü oranı (SNR) dinamik bir aralıkla 100 dB'ye ulaşır Aynı zamanda 100 dB'dir. Alıcı dönüştürücüden gelen sinyal çıkışı geniş bir dinamik aralığa sahiptir.Değişken kazanç yükselticisi AD8338 tarafından yükseltildikten sonra tepeden tepeye diferansiyel sinyal çıkışı 2,8 V iken, AD7760'ın tepeden tepeye diferansiyel giriş voltajı dinamik aralığı ve diferansiyel analog girişi karşılayan 3,25 V'tur. Gereksinimler. Ek olarak, AD7760, sinyal tamponlama ve seviye dönüştürme için dahili diferansiyel amplifikatörlere, aralık üstü bayraklara, dahili kazanç ve ofset kayıtlarına ve düşük geçişli dijital filtrelere sahiptir.Cihaz, programlanabilir bir onsimasyon oranı, 3 serisi FIR filtreleri, ondalık oranı ve filtreleme sağlar. Filtre seçimi ve baypasın birçok farklı kombinasyonu vardır, bu nedenle Tablo 1'de gösterildiği gibi, farklı koşullar altında sinyal çıkış hızları için gereksinimleri karşılayabilen 48 kHz ila 2.5 MHz arasında değişen birden çok veri hızında veri çıkışı sağlayabilir.

Cihazın giriş senkronizasyon pimi aynı zamanda uygulama için kolaylık sağlar ve kullanıcının zaman içinde bilinen bir noktadan analog ön uç girişinin örneklerini toplamasına izin verir, böylece işlemci, verici dönüştürücünün emisyon dalgası bittikten sonra analogdan dijitale dönüştürücüyü doğru bir şekilde kontrol edebilir. Koleksiyonun başlatılacağı zaman düğümü. Yüksek sinyal-gürültü oranı gerektiren uygulamalar için, AD7760 ayrıca ön uç sinyal koşullandırma devreleri için gereksinimleri basitleştirebilir, böylece analog devrelerin karmaşıklığını azaltabilir.

2.2 Toplama devre tasarımı

Edinim devresi, bir parça değişken kazanç amplifikatörü AD8338, bir parça analogdan dijitale dönüştürücü AD7760 ve bir FPGA parçasından oluşur. İşlemci, 0 ~ 80 dB amplifikatörün kazanç ayarını elde etmek için AD8338'in GAIN pinindeki voltajı (0.1 V ~ 1.1 V) ayarlar.Diferansiyel sinyal, OUTP ve OUTM pinlerinden verilir.Değişken kazanç amplifikatör devresi Şekil 3'te gösterilmiştir. .

AD7760'ın yukarıda açıklandığı gibi yüksek performansını elde etmek için, özellikle daha katı gereksinimleri olan güç girişi için uygun ayırma ve yerleşim teknikleri kullanılmalıdır.Her güç kaynağı pimi, bir ferrit boncuk aracılığıyla uygun bir güç kaynağına bağlanmalıdır ve bir 100 nF kapasitör, doğru toprak pimine ayrıştırılır ve AD7760'ın referans voltajı da özel bir düşük gürültü referans voltaj kaynağı tarafından sağlanır. AD7760, harici bir düşük titreşimli saat kaynağına ihtiyaç duyar ve giriş saati sinyali, cihazın MCLK pinine girilmeden önce arabelleğe alınmalıdır, bu nedenle FPGA tarafından oluşturulan 40 MHz saat sinyalinin AND geçidinin iki giriş terminalinden ve ardından AND geçidinden geçmesi gerekir. Çıkış, cihazın MCLK pinine bağlanır. Analogdan dijitale dönüştürme devresi Şekil 4'te gösterilmektedir.

FPGA ve AD7760 arasındaki sinyal hatları temel olarak çift yönlü veri yolu, çip sıfırlama hattı, çip seçimi, okuma ve yazma kontrolü, senkronizasyon sinyali ve veri hazır çıkış sinyalini içerir. Sıfırlama hattı, analogdan dijitale dönüştürücünün dahili dijital devresini sıfırlayabilir; senkronizasyon sinyalinin düşen kenarı, dahili filtreyi sıfırlayabilir; veri hazır çıkış sinyali, veri yolunda veri çıkışı olduğunu gösteren düşük seviyeli bir darbe sinyalidir; okuma ve yazma kontrolü, Çip seçimi ve çift yönlü veri yolu, analogdan dijitale dönüştürücünün dahili kayıtlarının konfigürasyonunu tamamlar ve filtrelenmiş çıkış verilerini okur.

2.3 Güç devresi tasarımı

Alım modülü tek bir güç kaynağı 5 V güç kaynağıdır, sistemin dahili FPGA çekirdek güç kaynağı voltajı 1,2 V, IO güç kaynağı voltajı 3,3 V, AD77602,5 V ve 5 V güç kaynağı kullanır, DSP çekirdek güç kaynağı voltajı 1,9 V, IO güç kaynağı voltajı 3,3 V. FPGA ve DSP düşük güç tüketen cihazlardır ve gerçek kullanımda güç tüketimi yaklaşık 300 mW iken, AD7760'ın normal çalışma koşulları altında güç tüketimi 1 W'a yakındır. Deneyde kullanılan doğrusal güç kaynağı, normal çalışma sırasında devrenin büyük güç tüketimi ve doğrusal güç kaynağının düşük dönüştürme verimliliği nedeniyle, normal çalışma sırasında tüm sistemin güç tüketiminin daha yüksek olduğunu ve güç yongasının, sistemin ağır koşullar altında kararlı çalışmasına elverişli olmayan ciddi ısı ürettiğini buldu. Böylece anahtarlama güç kaynağı gerçek kullanımda kullanılır. Anahtarlamalı güç kaynağı, küçük boyut, düşük güç tüketimi, yüksek dönüştürme verimliliği, geniş voltaj düzenleme aralığı, yüksek filtreleme verimliliği, güvenlik ve güvenilirlik ve esnek devre formları gibi avantajlara sahiptir. Devre TInin TPS62400 ve TPS62404ünü kullanır, giriş voltajı aralığı 2,5 ~ 6 V, ayarlanabilir voltaj çıkış aralığı 0,6 V ~ VIN, dönüştürme verimliliği% 95e kadar yüksektir, hata aralığı yalnızca% 1 ve çıkış akımı 400 mA ve 600 mA, güç kaynağı için sistemin performans gereksinimlerini karşılar Güç kaynağı devresi Şekil 5'te gösterilmiştir.

3 sistem yazılım tasarımı

Sistem yazılımı temel olarak iki bölümden oluşur: FPGA yazılımı ve DSP yazılımı FPGA yazılımı AD7760'ın kontrolünü gerçekleştirir, veri okuma arabelleği ve Flash okuma ve yazma; DSP yazılımı dolaylı yapılandırmayı, veri okuma ve işleme ve AD7760 veri gönderimini tamamlar. FPGA yazılım akışı Şekil 6'da gösterilmektedir.

AD7760'ın yazılım başlatması, saat osilatörünü başlatmayı, sıfırlama sinyalini düşük çekmeyi ve en az bir saat döngüsünü sürdürmeyi, sıfırlama sinyalini serbest bırakmayı ve en az iki saat döngüsünü sürdürmeyi, kontrol yazmacı 2 adresine yazmayı ve saat bölme oranını ayarlamayı ve kontrol yazmacına yazmayı içerir. 1 Adres ve veri çıkış veri hızını ayarlar, çip seçme serbest bırakma ve en az 5 saat döngüsü bekleyin. Konfigürasyon tamamlandıktan sonra senkronizasyon sinyali serbest bırakılır, analogdan dijitale dönüştürücü çalışmaya başlar, yazılım veri hazır sinyalini DRDY algılamaya başlar ve düşük seviyeli bir darbe algılandığında veri yolundaki verileri okumaya başlar.Veri iletimi 16 bit çift yönlü paralel arabirim, 24 bit kullanır Dönüştürme verileri iki tamamlayıcı biçiminde çıktı olarak verilir, bu nedenle dönüştürme sonucunu bir kez okumak için iki 16 bit okuma işlemi gerekir ve ikinci okuma işlemi dönüştürme sonucunun düşük 8 bitini ve 6 durum bitini verir. Dönüştürme sonucunu okuduktan sonra, DSP boş bayrak bitini kontrol edin, sonucu boşta Flash'a karşılık gelen adrese yazın ve DSP'ye bir iş döngüsünün bitiminden sonra bir tamamlanma sinyali verin. Çalışmaya başladıktan sonra, DSP analogdan dijitale dönüştürücünün konfigürasyon verilerini harici Flash'a yazar ve vericinin iletim süresini kontrol etmek için vericiye bir darbe sinyali sağlar Sondan sonra, yankı toplamayı başlatmak için analogdan dijitale dönüştürücünün senkronizasyon sinyali serbest bırakılır. Tam bir yankı sinyali topladıktan sonra, DSP tüm verileri dahili ara bellek alanına okur, veri FIR filtreleme ve işleme gerçekleştirir ve ardından yankı tanımlaması için RS422 arabirimi aracılığıyla ana bilgisayara gönderir.

4. Sonuç

Modülün hataları ayıklandıktan sonra, sistem performansı beklenen gereksinimleri karşılar. AD7760 beklenen çoklu frekans filtre veri çıkışına ulaşabilir, kazanç 0 ila 60 dB arasında ayarlanabilir, FPGA'nın harici saati 50 MHz'dir ve statik zamanlama analizi sentezden sonra gerçekleştirilir. En yüksek çalışma frekansı olabilir 242 MHz'e ulaşın, zamanlama gereksinimlerini karşılayın ve genel sistem güç tüketimi yaklaşık 2 W'tır. Yankı toplama modülü, test için tüm makineye eklenir.Tüm makine normal çalışır. Birden fazla aralıkta ölçülen su derinliği,% 1'lik hata gereksinimini karşılar, kazanç aralığı ayarlanabilir ve sistem kararlı ve güvenilirdir. Önceki ekipmanın alımını karşılaştırın Modül, analog devre parçasının tasarımını basitleştirir, doğruluğu ve performans-gürültü oranını iyileştirir ve örnekleme oranını büyük ölçüde artırır, böylece tüm cihazın doğruluğunu iyileştirir.

Referanslar

1 Analog Aygıtlar. AD8338. Düşük Güç, 18 MHz Değişken Kazançlı Amplifikatör Z. 2013: 1-20.

[2] Analog Cihazlar AD7760.2.5 MSPS, 24-Bit, 100 dB Sigma-Delta ADC, On-Chip Tamponlu Z .2006: 1-36.

3 Analog Cihazlar ADM3053 Sinyal ve Güç İzoleli Entegre İzole DC-DC Dönüştürücülü CAN Alıcı-Vericisi Z .2013: 1-20.

4 Analog Cihazlar ADM2582E Sinyal ve Güç İzoleli RS485 Alıcı-Verici ± 15 kV ESD Korumalı Z .2014: 1-20.

[5] Texas Instruments. TPS6240xQ12.25MHz 400mA ve 600mA Dual StepDown Converter Z .2014: 1-41.

[6] Hou Boheng, Liu Kai, Gu Xin. VHDL donanım açıklama dili ve sayısal mantık devre tasarımı (üçüncü baskı) [M] Xian: Xidian University Press, 2009.

[7] Wang Chenghua, Wang Youren, Hu Zhizhong, vs. Elektronik Devrelerin Temelleri M Pekin: Tsinghua University Press, 2008.

[8] WAITE A D. Pratik Sonar Mühendisliği M. Wang Deshi, Çevrilmiş Pekin: Electronic Industry Press, 2004.

[9] EDA Pioneer Stüdyosu Altera FPGA / CPLD Tasarımı (Temeller) [M] Wang Cheng, Wu Jihua ve diğerleri Pekin: Halk Mesajları ve Telekomünikasyon Basını, 2005.

AET üyeleri için yıl sonu avantajları!