ESIstream IP, deterministik veri serileştirme tasarımını basitleştirir

Genel Bakış

Modern geniş bant veri dönüştürücülerini kullanırken, ortaya çıkan yüksek hızlı seri veri akışını yönetmek büyük bir zorluktur. ESIstream, son derece düşük maliyetli, açık kaynaklı bir seri veri arabirim protokolüdür, birden çok FPGA mimarisinin basit donanım uygulamasını destekler ve minimum kaynak kullanır. Basitçe söylemek gerekirse, JEDEC'in JESD204B alt kümesi 1 ve 2 standartlarına açık kaynaklı bir alternatiftir. Ek olarak ESIstream, kullanıcılara düşük karmaşıklık, düşük bağlantı gecikmesi ve deterministik gecikme elde etmek için basit çözümler dahil olmak üzere bazıları burada tartışılacak olan birçok fayda sağlayabilir.

Bu makale yalnızca ESIstream mimarisini açıklayacaktır, çünkü şu anda JESD204B standardını iyi açıklayan birçok belge vardır. Sonra bu iki protokol arasındaki ince farkları ortaya çıkaracağız ve ESIstream protokolünün geliştiricisi Teledyne e2v, kullanıcıların kullanımını daha da basitleştirmek için kendi ESIstream VHDL IP'sini yayınlamaya karar verdi.

Seri tarih

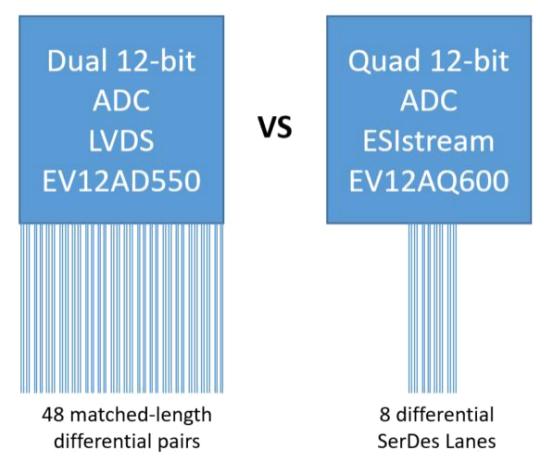

Yeni milenyumdan bu yana, veri dönüştürücü teknolojisinin ve CMOS teknolojisinin gelişimi işlevsel bir darboğaza ulaşmaya başladı. İlk başta, yüksek hızlı ADC ve DAC (fs > 10 MHz) paralel bir veri arabirimi kullanır, bu da basılı devre kartındaki (PCB) her bir veri dönüştürücüsünden büyük miktarda kablolamanın çekilmesi / tanıtılması gerektiği anlamına gelir (Şekil 1). Örnekleme hızı ve çıktı veri hızı arttıkça, PCB tasarımı gittikçe daha zor hale geliyor. Başlangıçta LVDS (düşük voltajlı diferansiyel model) kullanan serileştirilmiş arabirim, son zamanlarda bu veri aktarımı sorununa bir çözüm sağlayan serileştirici / seri çözücü (SERDES) arabirimini (saat, veri akışına gömülüdür) kullandı. PCB kablolamasını basitleştirebilir ve şekil parametrelerinin gelişimini büyük ölçüde teşvik edebilir. Arayüzün bu basitleştirilmesi, bağlantının her iki ucu için de faydalıdır (Şekil 1). Serdes bağlantısı PCB'nin tasarımını daha da basitleştirir çünkü veri hattı uzunluğunun eşleşmesini sağlamaya gerek yoktur.

Şekil 1 Bir seri bağlantının ara bağlantı yükünü nasıl azalttığı.

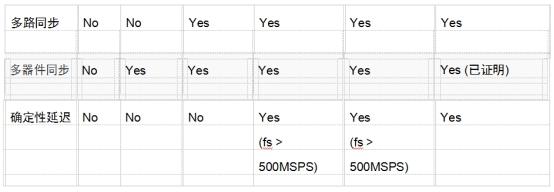

Bununla birlikte, uzun yıllar sonra, geniş bant veri dönüştürücülerinin getirdiği tüm sistem düzeyindeki zorlukları çözmek için bir seri çözüm vardır. Belirleyici gecikmeye ulaşmak, eşzamanlı örneklemenin ön şartıdır ve insanlar bunu incelemek için çok çaba sarf etmişlerdir. Aşağıdaki tablo (Tablo 1), JESD204 standardının gelişimini ve son 12 yıl veya daha uzun süredir açık kaynak ESIstream'in gelişimini göstermektedir.

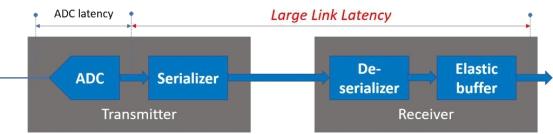

Buradaki nokta, kodlama / kod çözme işleminin tanıtılması ve yollar arasındaki hizalanmanın, ek bir iletim gecikmesine neden olan bazı ek alıcı yol elastik tamponları tarafından telafi edilmesidir.

Şekil 2 Serileştirme, ara bağlantı gecikmesini ortaya çıkarır.

Serileştirme, tek bir aygıtın ihtiyaç duyduğu belirli çıktı sürücülerinin sayısını azaltabileceğinden, veri dönüştürücülerinin güç gereksinimlerinin yönetilmesine de yardımcı olabilir. Ayrıca, diferansiyel bir seri hat uygulayarak, iyi bir dinamik aralık sağlamak için karmaşık bir sistemde üretilen elektriksel gürültüyü azaltmaya yardımcı olabilir. Ek olarak, kodlama şeması aynı zamanda spektral gürültüyü dağıtabilir ve diferansiyel sinyaller paraziti azaltabilir.

Aslında, şimdiye kadar, erken seri arabirim hala birden fazla paralel kanalın uygulanmasını destekleyemiyor ve tasarımcılar hala pano düzeyinde tasarım zorluğuyla karşı karşıya.

ESIstream özel uygulama

Şimdi ESIstream'in temel unsurlarına bakalım. ESIstream, en az önemli bit başta olmak üzere 14b / 16b veri kodlama algoritması kullanır ve 13 Gbps'yi aşan hat hızlarını destekler. 12 bit ve 14 bit dönüştürücüleri destekler. Protokol, Şekil 3'te gösterildiği gibi her veri kelimesine eşit olmayan bitler ve saat senkronizasyon bitleri (2 bitlik ekstra bir yük) ekleyerek doğrusal geri besleme kaydırma yazmacı karıştırma teknolojisini kullanır. Bu şekilde, kodlama verimliliği% 87,5'e kadar çıkmaktadır ve bu, JESD204B'den (8b / 10b kodlama akışı) biraz daha yüksektir. Eşit olmayan bit (DB), senkronize izlemeyi etkinleştirmek için CLK biti değiştirildiğinde veri bağlantıları arasındaki DC dengesini koruyabilir.

Şekil 3 ESIstream temel veri çerçevesi

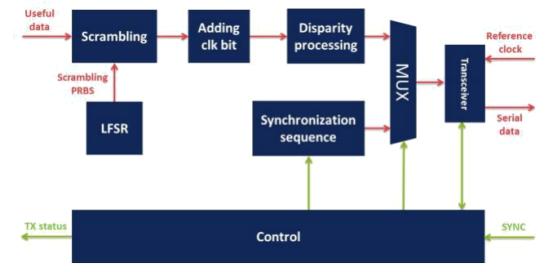

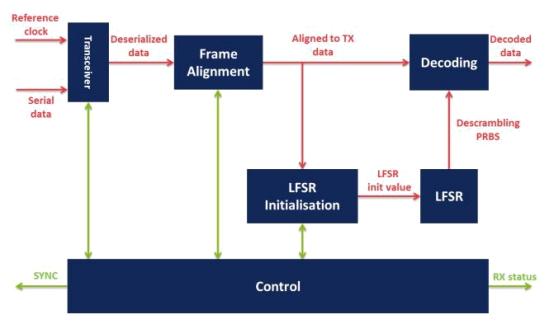

Şekil 4 ve Şekil 5, ESIstream vericisi (Tx) ve alıcı (Rx) çekirdeklerinin üst katman blok diyagramlarını göstermektedir.

Şekil 4 ESIstream'in Tx yolu

Şekil 5 ESIstream'in Rx yolu

ESIstream kodlama algoritması, seri arayüzün fiziksel sınırlamalarını azaltmak için tasarlanmıştır. En önemlisi, verici ve alıcı arasındaki bağlantı AC bağlantısı gerektirir. Bunu akılda tutarak, iletilen veriler DC dengesini sağlamalıdır, aksi takdirde bağlantı bağlantı kapasitörü kayabilir ve veri göz diyagramının alınan verileri kapatmasına ve yok etmesine neden olabilir.

Alıcı uçta, saat ve veri kurtarma (CDR) modülü, iletilen sinyali kilitlemek için genellikle bir PLL kullanır, bu nedenle ayrı bir saat hattı kullanmaya gerek yoktur. Bununla birlikte, CDR'nin kilitli durumu kilitlemesi ve sürdürmesi için, iletilen sinyalin belirli sayıda dönüşümden geçmesini sağlamak gerekir.

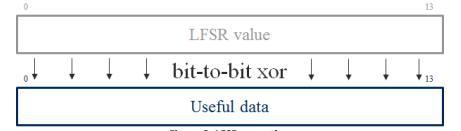

Gönderilen verileri karıştırmanın amacı, DC dengesini korumak ve bağlantının kilitli kalmasını sağlamaktır. ESIstream geliştiricileri, dijital tasarımın karmaşıklığını sınırlamak istediler, bu nedenle hata yayılmasını en aza indirmek için ek algoritmalar kullanıldı. Bu algoritma, 217-1 uzunluğundaki Fibonacci dizisine dayanmaktadır. Ek olarak, 14 bitlik bir kaydırma uygulanır. Dönüştürme işlemi ve doğrusal geri besleme kaydırma yazmacı verileri (sözde rasgele kod) tarafından elde edilen yararlı veri çıkışı, Şekil 6'da gösterildiği gibi XOR'lanır.

Şekil 6 LSFR kodlu XOR ile veri karıştırmayı gerçekleştirin

Karıştırmadan sonra, 14 bitlik veri sonucu 16 bitlik bir veri çerçevesine kodlanır. İlk ek saat biti, ardışık her çerçevede değiştirilir. İkinci ek bit eşit olmayan bit, eşit olmayan sayacın (RDC) mevcut durumuna göre ayarlanır. İki RDC durumu şunlara neden olabilir:

1. RDC +/- 16'dan azdır ve eşit olmayan bit "0" olarak ayarlanmıştır.

2. RDC +/- 16'dan büyük, eşit olmayan bit "1" e ayarlandı ve veriler tersine çevrildi (bitsel DEĞİL işlemi).

Bu işlem, Rx PLL tarafından kilitlenen minimum dönüşüm sayısı gereksinimini karşılayabilir ve DC bakiyesi bağlantısı gereksinimini karşılayabilir. Normal çalışma altında, alıcı uç önce eşit olmayan biti kontrol eder. Yüksekse, alınan veriler, çözülmeden önce tersine çevrilir. Düşükse, verilerin karışıklığı doğrudan çözülecektir.

Belirleyici işlemler için, ESIstream bağlantı senkronizasyonunu gerektirir, yani verici ve alıcıdaki veri çerçeveleri hizalanır ve bağlantının her iki ucundaki karıştırıcı motorlar aynı başlatma durumundadır. Senkronizasyon, çerçeve hizalama ve sözde rastgele bit dizisi (PRBS) başlatma olmak üzere iki adıma bölünmüştür.

Şekil 7 ESIstream bağlantı senkronizasyon çerçevesi

Alıcı uç, SYNC'i etkinleştirerek işlemi başlatır. Bu darbe en az bir kare periyodu sürmelidir. Ardından verici 32 çerçeveli bir hizalama deseni gönderir (Şekil 7). Alıcı uçta, bu ayrılmış dizi, karıştırmayı ve eşit olmayan işlemi atlar, böylece alıcı uç ve verici uçun zamanlaması hizalanır. Çerçeveleri hizaladıktan sonra, verici derhal 14 bit dahil 32 çerçeveli bir PRBS verisi gönderir

PRBS ve saat ve eşitsizlik bilgileri. Doğru işlemden sonra, alıcı uç LFSR, alıcı uç PRBS sözcüğü ile başlatılır. Bağlantı artık senkronize edilmiştir (Şekil 8). Kullanıcılar, alıcı uçtaki saat bitini gözlemleyerek senkronizasyon durumunu sürekli olarak izleyebilir. Saat biti belirli bir çerçevede değiştirilmezse, bir senkronizasyon sorunu oluşmuştur ve bağlantının sıfırlanması ve yeniden senkronize edilmesi gerekir.

Şekil 8 ESIstream alıcı hattı senkronizasyon dizisi

Karıştırma ve saat biti ve eşit olmayan bit işleme yoluyla, ESIstream belirli veri iletimini garanti edebilir.

Senkronize GHz örnekleme sistemi - hafif yürekli olanlar için değil

Bir radyo sisteminde dijital hüzmelemenin uygulanması, anten dizisinin düşük seviyeli sinyallerinin eşzamanlı örneklenmesini gerektirir. Bu, her anten düğümüne ulaşan sinyalin uzamsal bilgisinin kaydedilmesini gerektirir. Bu çözüm daha karmaşık olmasına ve ek güç tüketimi getirmesine rağmen, bazı önemli avantajlara da sahiptir:

· Yüksek sinyal-gürültü oranı (SNR), kablosuz bağlantı kapasitesini artırmaya yardımcı olarak sinyal aralığını artırır

· Paraziti önlemek için anten dizisinin uzamsal özelliklerini kullanın. Parazit belirli bir yönden geldiğinden, hüzmeleme algoritması paraziti ortadan kaldırmak için sıfırlama tekniklerini kullanabilir.

· Yüksek verimli ve geniş kapasiteli kablosuz bağlantılar, radar sisteminin aynı anda birden çok hedefi izleyebileceği veya cep telefonu ağının birden çok aramayı destekleyebileceği anlamına gelir.

Günümüzde birçok uygulama hüzmeleme kullanıyor veya en azından eşzamanlı örneklemeyi gerektiriyor. Bununla birlikte, GHz frekanslarında çalışırken, IC ve kart seviyesindeki sinyallerin yayılma süresi çok önemlidir. PCB izleri iletim hatları için kullanılır, bu nedenle faz bilgisini korumak için sinyal hattı uzunluğunun eşleştiğinden emin olmak gerekir. Hat uzunluğunun her santimetresi, teslimat süresini 60 ila 75ps artıracaktır. 6GHz örnekleme saatinin 166ps saat periyodu ile karşılaştırıldığında, kart seviyesindeki etkilerin tasarımı büyük ölçüde etkileyeceği görülebilir. Bu, PCB düzeninin neden yüksek hızlı örnekleme sistemlerinde önemli bir faktör olduğunu açıklar. Ancak, tasarımı zorlaştıran başka bir faktör daha vardır: Bu faktör, zaman alanı ile ilgilidir ve buna metastabilite denir.

Senkronizasyon zinciri, ESIstream'e kesin gecikme getirir

Metastabilite, dijital devrelerde belirsiz bir durumu tanımlar Örnekleme hızı arttıkça, potansiyel sistem zamanlama problemlerinin önemli bir nedeni haline gelir. Kullanıcıların, senkronizasyon zinciri şemasını tanıtmanın nedeni olan metastabilite ile mücadele etmek için senkronizasyon yöntemlerini kullanmaları gerekir.

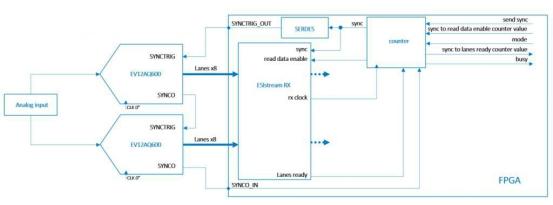

Kullanıcılar, senkronizasyon zamanlamasını gerçekleştirmek için güvenilir ve basit bir yönteme ihtiyaç duyar. Teledyne e2v'de deterministik senkronizasyon, bir çift olaya dayalı diferansiyel elektrik sinyali etrafında inşa edilir: senkronizasyon ve senkronizasyon çıkış sinyalleri (SYNCTRIG ve SYNCO). Bu sinyaller, hedef dönüştürücünün zamanlama sisteminin sıfırlanabilmesini ve tüm dijital alt sistemlerin ana referans saate uygun şekilde kilitlenmesini sağlar. Ek olarak, bu senkronizasyon şeması, büyük sistemlerde birden çok ADC'ye genişletilebilir.

Bu şemanın avantajı, çok basit olmasıdır - ek bir saat sinyali gerektirmez ve sistem yaşam döngüsü boyunca birden fazla paralel kanalın senkronizasyonunu sağlayabilir. Tasarım tamamlandığında ve üretime hazır olduğunda, doğru sistem senkronizasyonunu sağlamak için bir eğitim dizisi kullanılabilir. Sıcaklık veya voltaj değişiklikleri gibi çevresel koşullar değişirse, sistem zamanlama parametreleri değişmeden kalır. Senkronizasyon zinciri, seri üretim için büyük bir avantaj olan çok güvenilir bir senkronizasyon kaynağı sağlar.

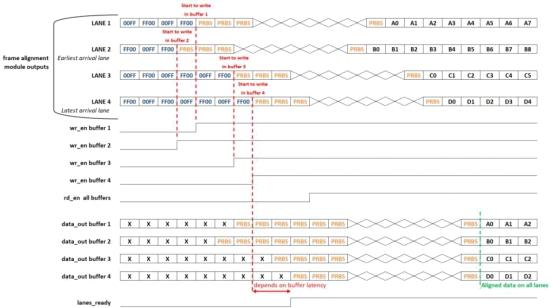

Daha sonra, deterministik gecikmeye ulaşmak için, ESI-akış bağlantısının alıcı ucunda, iletim işleminin maksimum hat gecikme belirsizliğini telafi etmek için basit bir sayaç ve alıcı elastik tampon bulunur.

Şekil 9 Çerçeve sayacının ESIstream alıcısındaki konumu

FPGA içindeki sayaç modülü, SYNCTRIG yükselen kenar olayı ve "tüm hatlar almaya hazır" olayı arasındaki Rx saatlerinin sayısını sayar. Bu bilgi ve esnek alma tamponu, tüm sistemin veri hizalamasını almasına izin verir. Bu şekilde, ESIstream'i kullanarak tüm sisteme deterministik davranışı genişletmek için ESIstream ürünlerinin sinyal zinciri işlevini kullanmak mümkündür.

ESIstream VHDL modül geliştirme hedefi

Teledyne e2v'nin savunucusu olan Teledyne e2v, ESIstream'in kullanımını kolaylaştırmak amacıyla sektördeki FPGA üreticileri (Xilinx ve Intel dahil) tarafından sağlanan genel amaçlı FPGA'lar için ESIstream Tx ve Rx IP modüllerini geliştirmek üzere 2018'in sonunda bir proje başlattı. IP, farklı işletim hızlarını destekleyecek ve havacılık seviyesi dahil olmak üzere farklı seviyelerdeki uygulamalar için uygun olacaktır. Kuşkusuz, IP'nin odak noktası, Teledyne e2v'nin mevcut ürün serisine uygun performans sağlamaktır. Bu sabit işlevli IP'ye ulaşmak için Teledyne e2v, çok çeşitli veri dönüştürücü örnekleme frekansları da dahil olmak üzere yapılandırılabilir hat hızı modüllerini dinamik olarak tanımlamak ve daha tanımlanabilir işlevleri desteklemek için alt katmanda çok fazla çalışma yapmıştır.

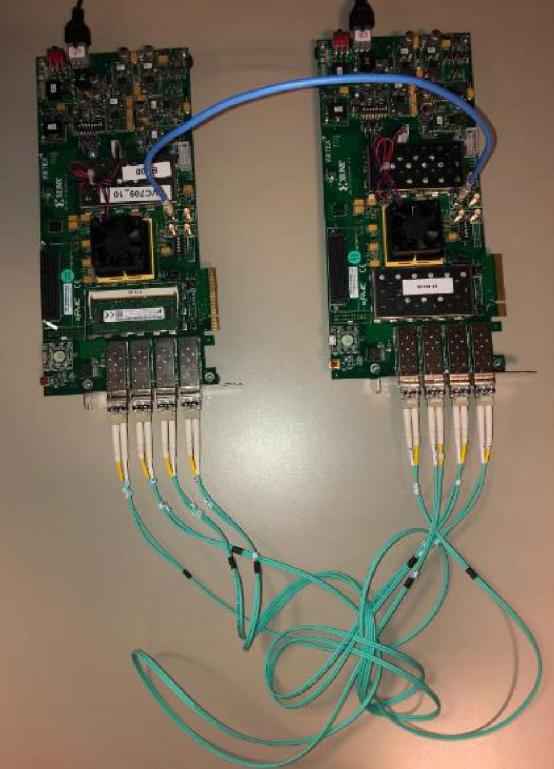

Serileştirmenin geleceği

Teledyne e2v'nin gelecekteki geliştirme planları, ESIstream fiziksel katman için fiber optik uygulamaları da içerir. Optik fiber, dönüştürücünün bakır tabanlı bir arayüz (PCB izi veya koaksiyel kablo) yerine FPGA'dan uzağa yerleştirilmesine izin verir. Dört SFP (Küçük Takılabilir) optik hat kullanarak ve 6Gsps hızında çalışan iki Xilinx VC709 değerlendirme panosunu bağlayarak, yukarıdaki özellikler kanıtlanmıştır.

Şekil 10 Fiziksel katman ESIstream Tx ve Rx kullanılarak fiber gösterimi

Test ve sertifikasyon tamamlandıktan sonra, kullanıcıların ücretsiz olarak indirmeleri için VHDL kod modülü web sitesine yerleştirilecektir.

ESIstream ve JEDEC karşılaştırması

ESIstream'in sistem düzeyinde avantajları kısaca şu şekilde özetlenebilir:

· Her cihaz için LMFC saatine gerek yoktur, LMFC saat hizalama işlemine gerek yoktur.

· Tek bir cihaz kullanırken veya birden fazla cihazı senkronize etmek için bir senkronizasyon zinciri kullanırken, ESIstream senkronizasyon sinyalinin PCB hat uzunluğu eşleşmesini dikkate almaya gerek yoktur.

· SYSREF gerekmez, bu nedenle JESD204B ile karşılaştırıldığında ESIstream, donanım karmaşıklığını azaltır ve deterministik çalışmayı başarır.

· ESIstream sistemindeki kesin senkronizasyon davranışı, senkronizasyon eğitimi adı verilen bir özellik aracılığıyla elde edilir (lütfen diğer belgelere bakın). ESIstream yalnızca bir sistem eğitimi gerektirir. Gecikme parametreleri elde edildiğinde, bu gecikme parametreleri belirli bir tasarım için değişmeden kalacaktır. Bu, ESIstream'in toplu üretimi kolay bir arayüz olduğu anlamına gelir.

Sonuç

JESD204B alt kümeleri 1 ve 2'de açıklanan JEDEC veri serileştirme yöntemi, çok kanallı veri dönüştürücü sistemlerinin deterministik çalışmasının zorluğunu çözüyor gibi görünüyor. Bu şüphesiz bir dereceye kadar doğrudur, ancak genellikle gözden kaçan, tasarımcıların karmaşık iletim ve spesifikasyon fiziksel katman gereksinimleri ile uğraşırken karşılaştıkları birçok zorluktur. Mühendisler genellikle JESD204B lisansının ve sinyal işleme SoC'leri (FPGA veya ASIC) için çekirdek IP'nin çoğu tasarım problemini çözmeye yardımcı olabileceğine inanırlar. Bununla birlikte, raporlara göre, birçok gerçek ve deneyim, JESD204B tarafından getirilen çok alanlı saat karmaşıklığının zamanlama kısıtlamalarının PCB tasarımına büyük sorunlar getirdiğini göstermektedir.

Başka bir yol var. ESIStream. ESIStream açık kaynaklı ve ücretsiz bir protokoldür. JESD204B ile aynı performans düzeyine sahiptir, ancak daha iyi bir kullanıcı deneyimi sağlayabilir. Düşük karmaşıklık, kolay tasarım, düşük güç tüketimi. Şimdi, endüstri standardı FPGA'lar için Rx ve Tx IP modüllerinin ve VHDL kod modüllerinin piyasaya sürülmesiyle, ESIstream'i kullanmanın zorluğu büyük ölçüde azaldı. Mevcut IP modülü geliştirme aşamasındadır ve Teledyne e2v'nin yeni veri dönüştürücüsünün teknik özelliklerini destekleyecektir. Ayrıca kullanıcılar yüksek hızlı seri projelerine uygun VHDL kod modüllerini ücretsiz indirebilirler.