"Akademik makale" için aktif gürültü kontrol platformunun FPGA uygulaması

Endüstriyel modernizasyonun gelişmesiyle birlikte gürültünün etkisi giderek daha fazla dikkat çekmiştir. Gürültü kontrolü temel olarak pasif gürültü kontrolü ve aktif gürültü kontrolü olarak ikiye ayrılır. Düşük frekanslı gürültü için, pasif gürültü azaltma teknolojisi tatmin edici olmayan bir bastırma etkisine sahiptir ve buna büyük malzeme tüketimi ve yüksek maliyet sorunları eşlik eder ve uygulanabilirliği zayıftır. Şu anda, Aktif Gürültü Kontrolü (ANC) teknolojisi önemli avantajlara sahiptir. Aynı zamanda, ileri geri hareket eden cihaz veya dönen cihaz tarafından üretilen dar bantlı gürültünün enerjisi belirli bir frekans bandında yoğunlaştığı için frekans değeri, genellikle akustik olmayan sensörler tarafından toplanabilen, dolayısıyla akustik geri besleme problemini ortadan kaldıran ve kullanım için daha uygun olan ayrı bir değerdir. Aktif kontrol yöntemi.

Şu anda, mühendislikteki akustik olmayan sinyallerin edinimi temelde birden çok seri olarak işlenmiş tek sensöre dayanmaktadır Birden fazla sensör aynı anda çalıştığında, veri toplama senkronizasyonu garanti edilemez, bu da sonraki veri işleme ve hesaplamalara neden olur. hata. Bazı mühendislik uygulamalarında, bu sorunu önlemek için, birden fazla sensörden sonra bir sinyal senkronizasyon düzenleyicisi ekleme çözümü önerilmektedir, ancak bu, tüm sistemi karmaşık ve çalıştırılması zahmetli hale getirecektir.

Yukarıdaki sorunlara yanıt olarak, bu makale FPGA'ya dayalı bir aktif gürültü kontrol platformu oluşturur. Platform, çok kanallı sinyallerin senkronizasyonunu karşılamak için sinyalleri gerçek zamanlı olarak doğru bir şekilde toplayabilir ve ayrıca kanalları gerekli işlevlere göre genişletmek de uygundur.Tüm platformun çalıştırılması da kolaydır.

1 Aktif gürültü kontrol platformu tasarımı

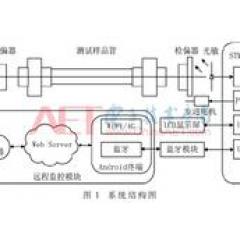

Aktif gürültü kontrol platformu, bir sensör çalıştırma sistemi ve bir gürültü azaltma algoritma modülünden oluşur.Sensör çalıştırma sistemi, FPGA'daki ilgili sensörlerden ve karşılık gelen veri işleme modüllerinden ve veri depolama modüllerinden oluşur.Referans sinyallerinden (birincil sinyallerle ilgili) sorumludur. Titreşim ve dönüş hızı sinyalleri gibi çeşitli sinyal formlarının toplanması ve ikincil akustik sinyallerin üretilmesi, gürültü azaltma algoritması modülü, temel olarak ikincil akustik sinyalleri üretmek için referans sinyalini analiz etmek için donanım dili tarafından oluşturulur.

Otomobilin içindeki gürültü esas olarak motor gürültüsü, giriş ve egzoz gürültüsü ve aktarma organının gürültüsüdür. Araştırmalar, motor titreşiminin neden olduğu düşük frekanslı gürültünün, arabadaki gürültünün ana bileşeni olduğunu göstermiştir.Aynı zamanda, diğer aktarma organlarının neden olduğu motor titreşim gürültüsü ve gürültü, motor titreşimi ve gövde üzerindeki çeşitli noktaların titreşimi ile doğru orantılıdır.Gürültüün ana frekansı da motor hızı ile orantılıdır. . Buna dayanarak, bu kağıt, arabadaki gürültünün referans sinyalini oluşturmak için arabanın hızı ve platform üzerindeki motorun titreşim ivmesi gibi akustik olmayan sinyalleri toplar ve ardından akustik geri besleme sorununu önlemek için ikincil akustik sinyali üretir.

Aktif gürültü kontrol platformu Şekil 1'de gösterilmektedir. Bunların arasında, MPU6065 yongası titreşim sinyallerinin toplanmasından sorumludur ve GCAN-600 modülü, hız sinyallerinin toplanmasından sorumludur.Akustik olmayan sinyallerden gürültü referans sinyalleri oluşturma sürecinde, birincil gürültü sinyallerinin ve ilgili algoritmaların katılımı gereklidir, bu nedenle WM8731 yongası ve ses gereklidir Giriş ve çıkış modülü, birincil akustik sinyallerin ve ikincil akustik sinyallerin çıkışının toplanmasını tamamlarken, SDRAM yongası, ilgili algoritmaları incelemek için toplanan verileri depolar.

2 Sensör çalıştırma sisteminin gerçekleştirilmesi

2.1 Titreşim ivmesinin toplanması

Titreşim hızlandırma elde etmek için kullanılan yonga MPU6065 yongasıdır ve yonga ile FPGA arasındaki sinyal iletimi UART protokolü aracılığıyla gerçekleştirilir. Örnekleme frekansı 100 Hz'dir.

Çip, çeşitli fiziksel sinyalleri toplayabilir (hızlanma, açısal hız, açı vb. Gibi) Farklı sinyallerin farklı veri paketi formatları ve kontrol bitleri vardır.Her veri paketi 10 veri biti ve 1 kontrol biti içerir. FPGA bunu tespit eder Doğru paket başlığından sonra ilk 10 numara geçici olarak saklanır ve kontrol biti ile karşılaştırılır.Doğru ise veri işleme gerçekleştirilir ve yanlışsa başlangıç durumuna geri döner ve bir sonraki doğru veri çerçevesinin gelmesini bekler.

2.2 Hız toplama

Otomobil hızının toplanması, tüm standart CAN veriyolu fiziksel katmanlarını ve ISO 15765 otomobil OBD arabirimi teşhis protokolünü destekleyebilen ve otomobil elektronik kontrol sisteminin çeşitli sensör değerlerini otomatik olarak seri format verilerine dönüştürebilen GCAN-600 modülüne dayanmaktadır. Modül, gerekli verileri okumak ve verileri UART protokolü aracılığıyla çıkarmak için ilgili AT komutunu girer. Örnekleme hızı 200 Hz'dir.

Motor hızı sinyaline karşılık gelen komut, ASCII kodu biçiminde iletilen ATPID = 012'dir Alınan her veri çerçevesi, PID012 = XXXX komutuna karşılık gelen ASCII kodudur. Bir iletim ve alım döngüsünün tamamlanması, bir dönüş hızının toplandığı anlamına gelir Dönme hızı sinyalinin sürekli olarak toplanması, iletim ve alım döngüsünün sürekli olarak döngüye alınması gerektiği anlamına gelir. Ancak alınan her veri çerçevesinin bir bitiş bayrağı biti yoktur ve hızın basamak sayısı belirsiz olduğundan (3 hane veya 4 hane), yukarıdaki döngü otomatik olarak gerçekleştirilemez ve bir tanımlayıcı gereklidir.

Verileri almak için UART protokolünü kullanırken, her bir numara alındığında, numaranın sonunda bir rx_done tanımlayıcısı oluşturulur. Alınan veri sinyalini bir mantık analizörü ile analiz edin ve her veri çerçevesinde iki rx_done arasındaki zaman aralığının T1 (UART protokolü tarafından seçilen baud hızıyla ilgili), önceki çerçevenin sonunda rx_done ve sonraki çerçevenin başında rx_done olduğunu bulun Zaman aralığı T2 (örnekleme oranıyla ilgili) ve T2'dir. > > T1. Bu nedenle, bir zamanlayıcı tasarlanır.Rx_done sinyali her algılandığında, zamanlayıcı zamanlamaya başlar, T1 + t (t < < Bir sonraki rx_done sinyali Tl'de tespit edilir ve çerçeve verisinin henüz sona ermediğini gösterir, bayrak sinyali tespit edilmezse, sayının son numara olduğunu gösterir ve yapılan çerçeve verisi iletim sonu tanımlayıcısı üretilir. Yapılan sinyali tespit ettikten sonra FPGA tekrar ATPID = 012 komutunu modüle gönderir ve bu döngüde kesintisiz hız sinyali elde edilebilir.

2.3 Ses girişi ve çıkışı

Ses sinyali alımı ve çıkışı için kullanılan çip, düşük güçlü ses kodek çipi WM8731'dir. Ses iletim modülü, FPGA ve ses kodek yongası WM8731'i bağlayan bir arayüz modülüdür, iki işlevi gerçekleştirmesi gerekir: ilk işlev, yonganın sistemin gerektirdiği modda çalışmasını sağlamak için WM8731 yongasına yapılandırma parametresi komutları göndermektir; İşlevlerden biri, parametre yapılandırması tamamlandıktan sonra mikrofonu ses verilerini toplamak üzere kontrol etmektir.

FPGA, yapılandırma parametrelerini I2C protokolü aracılığıyla çipe iletir Yapılandırma tamamlandıktan sonra, FPGA ve yonga ses veri iletimi gerçekleştirir. Ses edinme sürecine çeşitli parametreler dahil edilir: BCLK, ses veri iletimi (gönderme ve alma dahil) sürecindeki bit saati hattıdır, ADCLRC ve DACLRC, çipin ses verilerini göndermesi ve alması için çerçeve saat hatlarıdır ve ADCDAT ve DACDAT sırasıyla Ses verilerini göndermek ve almak için sinyal hattı.

Referans sinyali akustik olmayan sinyalden üretildikten sonra, referans sinyali bir ikincil akustik sinyal oluşturmak için gürültü azaltma algoritması modülünden geçer.

Birincil akustik sinyallerin alınması ve ikincil akustik sinyallerin çıkışı I2S modunu takip eder. Yani, ses verilerinin geçerli bitlerinin iletimi, ADCLRC veya DACLRC sinyal geçişlerinden sonra BCLK sinyalinin ikinci yükselen kenarında başlar ve ses verileri en yüksek bitten iletilir. Çip bağımlı modda çalışırken, BCLK sinyali FPGA denetleyicisi tarafından üretilir.

2.4 Veri depolama

Toplanan sinyalin, ana gövde olarak bir durum makinesine sahip bir SDRAM denetleyicisi aracılığıyla gerçek zamanlı olarak SDRANM yongasında depolanması gerekir.

SDRAM depolama verileri, belirli bir depolama uzunluğuna göre başlangıç konumundan sırayla depolandığından, üç sinyalin gerçek zamanlı olarak depolanması gerekir. Aynı zamanda, sinyaller birbirlerini etkileyemez veya örtemez, bu da SDRAM'daki üç sinyal için konum aralıklarının tahsis edilmesini gerektirir. Her sinyalin kendi farklı başlangıç pozisyonu vardır Depolama işlemi sırasında, SDRAM sırayla saklanır ve depolama adresi bir artırılır Depolama adresi birden fazla biti değiştirdiğinde, saklanan veriler kaybolur veya hata verir. SDRAM'de birden çok sinyal saklandığında, birden çok sinyalin bir bütün olarak bir dizi kontrolü gerekir. Ek olarak, SDRAM'de veri depolama sürecinde çapraz zaman etki alanı işlemleri olduğundan, platformda eşzamansız bir FIFO modülünün oluşturulması gerekir.

FIFO, ilk giren ilk çıkar veri arabelleğidir.Harici okuma / yazma adres satırı yoktur ve veriler yalnızca sıralı olarak yazılabilir ve okunabilir.Veri adresi, tamamlanması için dahili okuma / yazma işaretçisi tarafından otomatik olarak eklenir. Eşzamansız FIFO, okuma ve yazma bölümlerinde farklı saatler kullanır. Bu makalede, SDRAM'ın çalışma frekansı 27 MHz, hızlanma, dönme hızı ve ses edinme modüllerinin çalışma frekansı 50 MHz'dir.Verilerin zaman alanlarında iletilmesi gerekir. Ek olarak, birden fazla sinyali SDRAM'da saklama sürecinde, sekans kontrolü için asenkron FIFO kullanmak da gereklidir: bir sinyal saklandığında, diğer sinyaller geçici olarak FIFO'da depolanır ve önceki tip sinyal bir işaret oluşturmak için depolandıktan sonra, bir sonrakinde saklanır. Bir tür sinyal. Yani, birden fazla sinyal aynı anda toplanır ve sıralı olarak depolanır.

3 Sonuç analizi

Tüm edinim sistemi DE2-115 geliştirme kartı üzerine inşa edilmiştir.Seçilen FPGA, Cyclone IV EP4CE115F29 yongasıdır.Yapılan veri toplama sisteminin doğruluğunu onaylamak için, sistem aynı zamanda kayıt kullanılırken arabadan veri toplamak için kullanılır Cihaz ses sinyallerini toplar; hızlanma sensör sistemi titreşim ivmesini aynı konumda toplar; hız sensör sistemi motor devrini toplar. Oluşturulan platform tarafından toplanan sinyalin doğruluğunu ve gerçek zamanlı performansını doğrulamak için bu referans sistemi tarafından toplanan sinyali kullanın.

Deney sırasında, üç tek sinyal algılama sistemi, sinyalleri aynı anda toplamak için ilgili başlatma düğmelerine basar.Toplam edinim süresi 5 saniyedir. Yaklaşık 1 saniye sonra, yerleşik platformun başlat düğmesine basın ve üç sinyal aynı anda Edinme, 3 s edinimden sonra durun. Bu şekilde oluşturulan platform tarafından toplanan sinyaller, üç referans algılama sistemi tarafından toplanan sinyallerin alt sinyalleridir ve iki sistem tarafından toplanan üç sinyal çapraz korelasyonludur ve elde edilen korelasyon katsayıları ve alt sinyallerin başlangıç zamanı Şekil 2'de gösterilmiştir. Şekil 2'den dönme hızı sinyalinin başlangıç zamanı t1 = 1.1 s ve kendi kendine oluşturulmuş sistem edinim sinyali ile korelasyon katsayısının 1 olduğu; titreşim hızlanma sinyali başlangıç zamanı t1 = 0.91 s, kendi kendine oluşturulmuş sistem edinme sinyali ile korelasyon katsayısının 0.98 olduğu görülebilir. ; Ses sinyali başlangıç zamanı t1 = 1.34 s ve kendi kendine oluşturulmuş sistem toplama sinyali ile korelasyon katsayısı 0.94'tür (ses sinyalleri için, ilgili sistemlerin farklı alıcıları nedeniyle, toplanan ses sinyali genliğinin büyüklüğü daha uygun olması için farklıdır İki sistem tarafından toplanan sinyalleri karşılaştırın, normalleştirin). Korelasyon katsayısının tanımına göre, iki sistem tarafından toplanan üç segmentli sinyaller karşılık olarak eşit olarak kabul edilebilir ve alt sinyalin başlama zamanı referans sinyale eşlenir Üç sinyalin zaman alan diyagramları Şekil 3'te gösterilmiştir. Kendi kendine oluşturulmuş platform tarafından toplanan hız sinyalinin gerçek zamanlı doğruluğu kanıtlanmıştır.

Şekil 2'deki yatay karşılaştırmadan, kendi kendine oluşturulmuş platform tarafından toplanan üç sinyalin, üç bağımsız referans sisteminde başlangıç zamanları t1, t2 ve t3'e karşılık geldiği görülebilir. Bu birbirine eşit değildir. Bu aynı zamanda birden fazla sinyalin toplanması için daha fazla olduğunu kanıtlar. İki edinim sistemi aynı anda çalışırken, elde edilen verilerin sıkı senkronizasyonu garanti edilemez ve sinyal senkronizasyon ayarı için özel bir alet gereklidir. Kendi kendine inşa edilmiş platformda, birden fazla sinyalin çalışması, verilerin senkronizasyonunu kesinlikle garanti edebilen aynı düğme ile gerçekleştirilir, böylece aracın çeşitli parametreleri herhangi bir zamanda elde edilebilir.

4. Sonuç

Bu makale, FPGA'ya dayalı olarak otomobillerin aktif gürültü azaltımı için bir platform oluşturur.Bu platformun çalıştırma algılama sistemi, çalışma sırasında otomobilin hızını, titreşim ivmesini ve gürültü sinyallerini etkili bir şekilde toplayabilir. Aynı zamanda platform, aktif gürültü azaltma algoritmaları tarafından uygulanan bir donanım sistemidir ve sonraki aktif gürültü azaltma araştırmaları için önemli bir temel oluşturur.

Veriler SDRAM'da saklanmadan önce, geçici olarak FIFO'da depolanması gerekir.Sonuç olarak, depolanan veri miktarı FIFO'nun kapasitesi ile ilgilidir.Nios II, veri depolamayı büyük ölçüde genişletebilen çok kanallı sinyallerin saklama sırasını kontrol etmek için kullanılabilir. Kapasite, ancak geliştirme döngüsü daha uzun.

Özetle, platform aşağıdaki avantajlara sahiptir:

(1) Platform, referans sinyalini doğru ve gerçek zamanlı olarak toplayabilir. Bu, aktif gürültü azaltma sürecinde üretilen ikincil akustik sinyallerin gerçekleştirilmesi için iyi bir temel oluşturur.

(2) Platform, toplanan çok kanallı sinyaller için sıkı zaman senkronizasyonuna sahiptir, yani çok kanallı sinyallerin eşzamanlı çalışmasını sağlayabilir, bu da seri işlemcilere dayalı diğer sistemlerin elde edemediği bir avantajdır.

(3) FPGA'nın programlanabilirliği, platformun işlevleri isteğe bağlı olarak artırmasına olanak tanır ve kanal sayısını başka yongalar veya işlemciler eklemeden genişletmek uygundur.

(4) Platformun tam olarak tasarlanabilmesi, geliştirilebilmesi ve doğrulanabilmesi için tekrar tekrar programlanabilen, kontrol edilebilen ve yeniden programlanabilen çeşitli mantık işlev modüllerini (kontrol modülleri ve gürültü azaltma algoritması modülleri gibi) programlamak için donanım dilini kullanın.

-

- Yatırımcılar okumalı | ABD hisse senetleri genel olarak yükseldi! Danıştay işe alımlarını genişletti ve bu tür hisse senetleri ağır faydalar getirdi!