SoC FPGA'ya Dayalı Beidou Alıcı Taşıyıcı İzleme Döngüsünün "Akademik Belge" Tasarımı

Özet:

Beidou uydu navigasyon alıcısının yüksek gerçek zamanlı performansını, minyatürleştirmesini ve düşük güç tüketimini gerçekleştirmek için, SoC FPGA'ya dayalı bir taşıyıcı izleme döngüsü tasarım şeması önerilmiştir. FLL (Frekans Kilitli Döngü) ve PLL (Faz Kilitli Döngü) analizi ile ve SOPC teknolojisi kullanılarak, FPGA içindeki taşıyıcı sıyırma işlemini tamamen tamamlayabilen SoC FPGA'ya dayalı bir taşıyıcı izleme döngüsü gerçekleştirilir. Test sonucu, planın, taşıyıcı sinyalinin hızlı ve doğru bir şekilde izlenmesini sağlayabildiğini ve iyi bir gerçek zamanlı performans ve uygulama değerine sahip olduğunu göstermektedir.

Çince alıntı biçimi: Wei Zhaochuan, Pan Jundao, Wu Guozeng.SoC FPGA'ya dayalı Beidou alıcı taşıyıcı izleme döngüsünün tasarımı.Elektronik Teknoloji Uygulaması, 2018, 44 (6): 124-128.

İngilizce alıntı biçimi: Wei Zhaochuan, Pan Jundao, Wu Guozeng.SoC FPGA'ya dayalı Beidou alıcısı için taşıyıcı izleme döngüsü tasarımı.Elektronik Tekniğin Uygulanması, 2018, 44 (6): 124-128.

0 Önsöz

Küresel Navigasyon Uydu Sistemi (GNSS), ulusal güvenliğin sağlanması ve ekonominin geliştirilmesi için önemli bir altyapıdır ve ülkenin kapsamlı ulusal gücünün ve modern bir gücün uluslararası etkisinin önemli bir sembolüdür. Beidou navigasyon sistemini destekleyen alıcı terminallerinin geliştirilmesi, Beidou navigasyon sisteminin vazgeçilmez bir parçasıdır. Şu anda Çin, Beidou uydu navigasyon sistemini (BDS) güçlü bir şekilde geliştiriyor, bu nedenle BDS'ye dayalı Beidou uydu navigasyon alıcısının güçlü araştırması ve tasarımı, Beidou uydu navigasyon sisteminin önemli bir parçası haline geldi.

Yarıiletken entegrasyonu hızla gelişiyor ve şu anda yakınsak silikon levhalara doğru gelişiyor. FPGA bu yönde bir istisna değildir.Genel amaçlı işlemciler, ASSP ve DSP işlevlerine sahip IP sürekli olarak FPGA'ya entegre edilir; FPGA teknolojisinin sürekli inovasyonu ve atılımı ve silikon birleşik mimari ürünlerin tanıtımı, kaçınılmaz olarak FPGA uygulamaları yapacaktır. Daha önce dahil edilmemiş birçok alan. Teknolojinin ilerlemesiyle, SoC yüksek entegre tek çipli alıcıların geliştirilmesi, gelecekteki uydu navigasyon alıcısı gelişiminin ana yönü olacaktır.

1 SoC donanım sistemi tasarımı

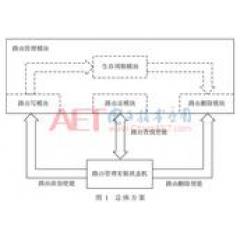

Sistem, ana kontrol yongası olarak Intel 28 nm işlem düşük güçlü Cyclone V 5CSEM5F31C6N SoC FPGA kullanır. SoC FPGA'ya dayalı taşıyıcı izleme döngüsünün donanım sistemi tasarımı Şekil 1'de gösterilmektedir.

SoC Sistemi, Qsys System (gömülü sistem) bölümünün donanım tasarımı ve Verilog HDL'ye dayalı FPGA Sistemi (FPGA mantık birimi sistemi) donanım tasarımı dahil olmak üzere temel olarak iki bölümden oluşur.

1.1 Qsys Sistem tasarımı

Şekil 1'deki tasarıma göre, Qsys sistemi Qsys araçları kullanılarak oluşturulmuştur ve ara bağlantı Şekil 2'de gösterilmiştir.

Sistemin her bir parçasının işlev tasarımı aşağıdaki gibidir:

(1) clk_0, TCXO-50M saat girişi ve PLL için sistem sıfırlama sinyali sağlayan harici bir saat ve sıfırlama girişidir.

(2) pll_0, Qsys'deki her bileşene 6 saat, outclk0 ve outclk5 sağlayan Şekil 1'deki PLL'dir; outclk1, çip dışı SDRAM için saat sağlar; kalan 3 saat, FPGA Sistemindeki her modül için harici olarak çıkarılır Sürücü saati.

(3) sdram, Nios II Gen2 Core'un belleği olarak işlev gören yonga dışı SDRAM yongasını kontrol etmek için kullanılan Şekil 1'deki SDRAM Denetleyicisidir.

(4) epcs, harici Flash'ı kontrol eden ve Nios II Gen2 Core'un program hafızası olarak görev yapan Şekil 1'deki EPCS Flash Denetleyicisidir.

(5) jtag_uart_0, program işleminin izlenmesi ve hata ayıklama için PC ana bilgisayarındaki Eclipse SBT'nin hata ayıklama portuna bağlanan Şekil 1'deki JTAG Denetleyicisidir.

(6) sysid, yazılım programı sürümünün Qsys sistem sürümü ile tutarlı olmasını sağlamak için Şekil 1'deki Sistem Kimliğidir.

(7) Timer_0, Nios II Gen2 Core çekirdek saati için kullanılabilen ve aynı zamanda programın çalışma süresini test etmek ve ölçülen zamana göre karşılık gelen testi ve hata ayıklamayı gerçekleştirmek için kullanılabilen Şekil 1'deki Aralık Zamanlayıcısıdır.

(8) LED, Şekil 1'deki LED Denetleyicidir, burada PIO çekirdeği bir çıkış işlevi olarak tasarlanmıştır ve çıkış verilerinin bit genişliği, sistemin çalışma durumunu test etmek ve sormak için FPGA Sisteminin 6 LED'ini kontrol etmek için 6 bit olarak ayarlanmıştır.

(9) Saat, Şekil 1'deki Avalon-MM Saat Geçiş Köprüsüdür, Avalon veri yoluna bağlanmak için kullanılır ve farklı saat alanlarındaki IP çekirdekleri arasındaki veri iletimi ve iletişimine aittir.

(10) INIT5 ve INIT6, PIO çekirdeğinin sinyal giriş fonksiyonunu kesmek için ayarlandığı, INIT5 ve INIT6'nın bit genişliğinin 1 bit olarak tasarlandığı ve kesme modunun kenar (yükselen kenar) tetiklemeye ayarlandığı Şekil 1'deki Kesme Denetleyicileridir. INIT5 ve INIT6, sırasıyla FPGASystem tarafından üretilen 2 kesme sinyalini almak için kullanılır.

(11) aFloa, Nios II Gen2 Core'un kayan nokta aritmetik donanımını hızlandırmak için kullanılan Şekil 1'deki Kayan Nokta Donanımıdır.

(12) SoC_TO_FPGA_V2_1_0, Şekil 1'deki adres veri iletişim IP'sidir. Bu arayüz, FPGA Sistemi ve Qsys Sistemi arasında iki yönlü veri aktarımı için kullanılır.

(13) hps_0, Şekil 1'deki HPS Sistemidir ve hps_0, konumlandırma sonrası çözümün ve grafik arayüzün ana CPU'sudur. Linux sistemini destekleme gerekliliği nedeniyle, EMAC, QSPI, SD / MMC, USBOTG, SPI, UART, I2C ve bazı GPIO'lar gibi çevre birimleri dahil olmak üzere bazı çevre birimlerinin kurulması gerekir.

(14) nios2_gen2_0, temel bant sinyal işleme sisteminin ana CPU'su olarak tasarlanmış, Şekil 1'deki Nios II Gen2 Çekirdektir.

(15) Dual_ram Şekil 1'de gösterilen Dual-port RAM, HPS ve Nios II Gen2 Core arasında veri iletişimi sağlar; HPS, Nios II Gen2 Core ve Dual-port RAM arasındaki ilişki blok diyagramı Şekil 3'te gösterilmektedir.

Şekil 4, System Interconnet Fabric'te Qsys sisteminin her bir bileşeninin adres tahsisini gösterir.

1.2 FPGA Sistem tasarımı

FPGA Sistemi temel olarak SPI kontrol modülü, yüksek hızlı veri arayüzü, zaman referans modülü, yakalama modülü, izleme modülü, seri port modülü, adres kod çözme ve veri kanalı seçim modülünden oluşur. Her bir parçanın işlevleri aşağıdaki gibidir:

(1) SPI kontrol modülü, 3.098 MHz ara frekans verisi oluşturmak için anten alınan sinyalle karıştırılan 1550 MHz'lik yerel osilatör taşıyıcı sinyali oluşturmak için radyo frekansı kartını kontrol etmek için kullanılır.

(2) Yüksek hızlı veri arayüzü, I / Q iki kanallı 8 bit veriyi nicelemek ve oluşturmak için RF ön ucunun yüksek hızlı ADC'sini elde etmek için kullanılır ve her kanal, temel bant işleme için yüksek 4 bit veriyi keser.

(3) Zaman referans modülü, 0,5 ms ve 20 ms kesintiler dahil olmak üzere 2 kesinti sinyali üretmek için kullanılır.

(4) Yakalama modülü uydu yakalama için kullanılır ve yakalama kanalı tek kanallı bir tasarımdır.

(5) İzleme modülü uydu takibi için kullanılmaktadır.İzleme kanallarının sayısı şu anda 24 kanal olacak şekilde tasarlanmıştır.

(6) Seri bağlantı noktası modülü, hata ayıklama bilgileri ve gezinme mesajlarını çıkarmak için kullanılır.

(7) Adres kodu çözme ve veri kanalı seçim modülü, adresin kodunu çözmek ve adres bilgilerine göre farklı veri kanallarını seçmek için kullanılır.

2 Taşıyıcı döngü tasarımı

2.1 Taşıyıcı halka ayırıcı

Uydu sinyali navigasyon mesajları ile modüle edildiğinden, alınan ara frekans sinyali, veri bit seviyesi sıçradığında 180 ° 'lik bir faz sıçraması üretecektir.Bu nedenle, döngünün kararlılığını korumak için 180 ° faz sıçraması ortadan kaldırılmalıdır. değişiklik. COSTAS JP tarafından icat edilen faz dedektörü veri bitlerinden etkilenemeyeceği için, icat ettiği faz dedektörüne Costas faz dedektörü (veya Costas faz dedektörü) ve bu faz dedektörlerini kullanan faz kilidi adı verilir. Yüzük, Costas yüzüğü (veya Costas yüzüğü) olarak adlandırılır.

Bu tasarımın faz kilitli döngü ayırıcısı, sinyal-gürültü oranı düşük olduğunda yaklaşık olarak optimize edilmiş faz ayırt etme özelliklerine sahip klasik Costas döngü faz ayırıcısı Qp × Ip'i kullanır, çıktı sonucu genliğin karesiyle orantılıdır ve hesaplama miktarı Küçüktür ve faz ayrım eğimi, sinyal genliğinden büyük ölçüde etkilenir.

Bu yazıda, frekans kilitli döngü ayırıcı, düşük sinyal-gürültü oranı durumunda neredeyse optimize edilmiş frekans ayırt etme özelliklerine sahip çapraz ürün ayırıcı Pcross / (t2-t1) 'i benimsemek için tasarlanmıştır, eğim sinyal genliğinin karesiyle orantılıdır, minimum hesaplama miktarı ve Sinyal genliğinden etkilenir.

2.2 Döngü filtresi

3 Taşıyıcı halka yazılım tasarımı

Yazılım programının tasarım fikri, izleme döngüsünün işleme programını 0,5 ms'lik kesintiye yerleştirmektir. 0,5 ms'lik kesinti, sırayla her kanalı sorgular ve mevcut izleme kanalı durumuna göre traksiyon veya izleme yapılıp yapılmayacağını seçer: eğer çekiş durumundaysa, traksiyon alt rutini çağrılacaktır. ; İzleme durumundaysa, izleme alt rutini çağrılacaktır. Çalışma süreci Şekil 6'da gösterilmektedir.

Çekiş alt yordamı, FPGA'dan I / Q ile ilgili genliği okumayı ve gücü hesapladıktan sonra, sırasıyla kod döngüsünü, frekans kilitli döngüyü ve faz kilitli döngü işleme alt yordamlarını çağırmayı içerir Kod döngüsü, frekans kilitli döngü ve faz kilitli döngü, frekans ayrımına ve ayrımına tabidir. Faz ve döngü filtrelemeden sonra, FPGA içindeki NCO kodunu ve taşıyıcı NCO kodunu güncelleyin ve mevcut kanal durumunu bit senkronizasyonuna göre ayarlayın: senkronizasyon başarılıysa, mevcut kanalı izleme durumuna ayarlayın; senkronizasyon başarısız olursa, çekme sayısı gerçekleştirilecektir. İstatistikler, istatistik eşiği aşılırsa, kanal kapanmaya ayarlanır, kanal yeniden yakalanır ve başlatılır ve ardından traksiyon alt yordamından dışarı atlanır, aksi takdirde doğrudan traksiyon alt yordamından atlar. Çekiş işleme alt rutini Şekil 7'de gösterilmektedir.

İzleme alt yordamı, FPGA'dan I / Q ile ilgili genlikleri okumayı, gücü hesapladıktan sonra kod döngüsünü ve faz kilitli döngü işleme alt yordamlarını çağırmayı ve kod döngüsü ve faz kilitli döngü faz algılama ve döngü filtreleme ile işlendikten sonra dahili FPGA'nın güncellenmesini içerir. Görev durumunu çerçeve senkronizasyon durumuna göre ayarlayın: senkronizasyon başarılıysa, navigasyon mesajı işleme görevini görev kuyruğuna itin; faz kilidi durumunu belirleyin, faz kilidi başarısız olursa kanal durumunu çekişe ayarlayın Durum ve ardından izleme alt programından çıkın. İzleme işleme alt yordamı Şekil 8'de gösterilmektedir.

4 Test sonuçları

Sinyal çekişe girdikten sonra, frekans kilitli döngü filtresinin çıkış değerini toplamak için Nios II SBT for Eclipse kullanın ve Şekil 9'da gösterildiği gibi frekans kilitli döngü filtresinin çıkış değerinin zamanla değişimini simüle etmek için MATLAB kullanın. Şekilden, 0 zamanında, frekans hatasının mutlak değerinin yaklaşık 100 Hz olduğu görülebilir; 0 ila 300 ms arasındaki aralıkta, döngü tarafından anlık frekans hatası çıkışının mutlak değeri, zamanla kademeli olarak azalır; 300 ms zamanında, döngü Çıkış anlık frekans hatasının mutlak değeri 0'a yakındır ve ardından faz kilitli döngü, faz hatasını daha da işlemek için devreye girer.

PLL döngü filtresinin çıkış değerini toplamak için Nios II SBT for Eclipse kullanın ve Şekil 10'da gösterildiği gibi PLL döngü filtresinin çıkış değerinin zamanla değişimini simüle etmek için MATLAB kullanın. Bölüm 3'teki izleme alt yordamının tasarımına göre, hassas izleme aşaması, frekans hatasının etkisini ortadan kaldırmak için çekiş aşamasından geçer ve ardından hassas izleme için faz kilitli döngüyü kullanır. Şekilden, faz kilitli döngünün faz hata aralığının temelde ± 15 ° içinde dalgalandığı görülebilir.

5. Sonuç

Temel bant sinyal işlemenin gereksinimlerine göre, bu makale tasarım platformu olarak SoC FPGA kullanır, Beidou uydu sinyali izleme algoritmasının tasarımını tek bir çip üzerinde tamamlar ve ilgili taşıyıcı döngü algoritmasını test eder ve doğrular. Sonuçlar, izleme algoritmasının Beidou uydu navigasyon alıcısının gerçek zamanlı gereksinimlerini tam olarak karşıladığını göstermektedir.

Referanslar

Ning Jinsheng, Yao Yibin, Zhang Xiaohong Küresel navigasyon uydu sistemlerinin gelişimine genel bakış. Navigasyon ve Konumlandırma Dergisi, 2013 (1): 3-8.

Xu Jingyu FPGA, silikon entegrasyonu çağına doğru ilerliyor World Electronic Components, 2012 (7): 71-72.

Wu Guozeng, Wei Zhaochuan, Tang Zhenhui ve diğerleri.Qsys tabanlı HPS ve FPGA veri iletişim arabirimi IP çekirdeğinin uygulanması. Journal of Guilin University of Electronic Technology, 2018, 38 (1): 16-22.

Zhang Jingbo. GNSS Yazılım Alıcısı için Yüksek Dinamik Taşıyıcı İzleme Döngüsünün Anahtar Teknolojisi Araştırması Dalian: Dalian Denizcilik Üniversitesi, 2012.

COSTAS J P. Synchronous Communications.IEEE, 2002, 90 (8): 1461-1466.

Xie Gang. GPS prensibi ve alıcı tasarımı Beijing: Electronic Industry Press, 2009.

Lu Yu. Beidou / GPS İkili Mod Yazılım Alıcısının Prensip ve Uygulama Teknolojisi Pekin: Electronic Industry Press, 2016.

Zha Huan, Li Chao.Beidou uydu navigasyon alıcısı için izleme döngüsü teknolojisinin tasarımı ve uygulaması.Optik ve Optoelektronik Teknolojisi, 2016, 8 (4): 59-61.

Shen Feng, Xu Dingjie, Xue Bing. Navigasyon Alıcısında FLL / PLL Kombinasyonuna Dayalı Taşıyıcı Takibinin Uygulanması. Navigasyon, 2004 (2): 51-54.

yazar bilgileri:

Wei Zhaochuan, Pan Jundao, Wu Guozeng

(Bilgi ve İletişim Okulu, Guilin Elektronik Teknolojisi Üniversitesi, Guilin 541004, Guangxi)

-

- Kai Chen bağımsızlığını ilan ediyor Sektör alkışları bastırmak veya teşvik etmek için büyük bir sopa vermeli mi?

-

- "AET Original" 5G, Nesnelerin İnterneti, Otonom Sürüş, NI Trend Outlook Raporu 2019'da hangi yeni trendler ortaya çıkıyor?

-

- "Gizemli Kasabadaki Cinayet" in perde arkasında Matt Damon, 1950'lerde orta yaşlı yağlı bir adama dönüşüyor.