Sistem Üreteci Modeli Türetme Yöntemine Göre Yükseltme Dönüştürücüsünün Kontrolü

Liu Chaoyong 1, Wang Suichao 2, Zheng Xiancheng 2

(1. Shanghai Aircraft Design and Research Institute, Shanghai 201210; 2. School of Automation, Northwestern Polytechnical University, Xi'an 710000, Shaanxi)

Modüler modelleme yöntemine dayalı dönüştürücü modellemeyi gerçekleştirmek ve dil programlama kontrol sisteminin karmaşık sürecini basitleştirmek için System Generator yazılım platformunu kullanın. MATLAB-Xilinx ortamından modüler modelleme yöntemi kullanılarak türetilen kontrol algoritması incelenmiştir. Kontrol algoritmasını dışa aktarmanın ve kullanmanın uygulanabilirliğini kanıtlamak için MATLAB simülasyonu, yazılım ve donanım birlikte simülasyonu ve deneyiyle doğrulanır.

Sistem Üreteci; modüler modelleme; kontrol algoritması dışa aktarımı

Çin Kütüphanesi Sınıflandırma Numarası: TP273

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.2017.07.015

Çince alıntı biçimi: Liu Chaoyong, Wang Suichao, Zheng Xiancheng. Sistem Üreteci model türetme yöntemine dayalı olarak dönüştürücü kontrolünü artırın.Elektronik Teknoloji Uygulaması, 2017, 43 (7): 59-62.

İngilizce alıntı biçimi: Liu Chaoyong, Wang Suichao, Zheng Xiancheng System Generator modelinin dışa aktarma yöntemine dayalı olarak Boost dönüştürücü kontrolünün uygulanması.Elektronik Tekniğin Uygulanması, 2017, 43 (7): 59-62.

0 Önsöz

Geçmişte, FPGA tasarımcıları, tasarımcının diline yüksek talepler getiren model oluşturmayı uygulamak için çoğunlukla Verilog / VHDL dilini kullanıyorlardı. Modüler tasarıma dayalı model oluşturma yöntemlerinin ortaya çıkışı, karmaşık dil modelleme sürecini basitleştirir, sistemin tasarımından uygulanmasına kadar olan döngüyü büyük ölçüde kısaltır ve ayrıca uygulanan işlevlerin tutarlılığını sağlar.

Xilinx'in System Generator yazılımıyla birlikte gelen algoritma modülü, FPGA'lerin tasarımı ve kullanımı için yeni yöntemler sunar. FPGA'nın kendi zengin tetikleme kaynaklarını, çok sayıda I / O pin kaynağını, yüksek hızlı CMOS teknolojisini ve düşük güç tüketimi özelliklerini birleştiren System Generator yazılımı, kontrol sistemini dışa aktarabilir ve FPGA entegre geliştirme yazılımına uygulayarak tasarımı basitleştirebilir süreç.

Sistemin tamamı, test için FPGA platformuna indirilen bir donanım dili entegre çekirdeğini doğrudan oluşturmak için System Generator yazılımı tarafından simüle edilir, böylece zayıf Verilog / VHDL dil altyapısına sahip mühendisler tasarım, simülasyon ve deney yoluyla FPGA geliştirme çalışmalarını iyi bir şekilde gerçekleştirebilir.

1 Modüler modellemeye dayalı

1.1 Xilinx Yazılımına Giriş

Xilinx'in yeni nesil entegre geliştirme ortamı Vivado, fikri mülkiyet (Fikri Mülkiyet, IP) çekirdeklerine dayalı tasarım yöntemini vurgular, sistem düzeyinde tasarım fikirlerini daha fazla yansıtır ve tasarımcının FPGA alt katmanının düzenine ve yönlendirmesine müdahale etme becerisini daha da geliştirir.

Geliştiriciler, model oluşturmayı tamamlamak için Xilinx modülünü çağırmak için MATLAB / Simulink ortamını kullanabilir ve yerleşik kontrol modülü için optimize edilmiş ağ listeleri ve fikri mülkiyet temel dosyaları oluşturmak için çekirdek oluşturucuyu çağırarak, ilgili proje dosyalarını dışa aktarabilir ve oluşturabilir. MATLAB / Simulink tarafından oluşturulan proje dosyası, en sonunda FPGA tarafından yürütülebilen bir veri akışı dosyası oluşturmak için Vivado yazılımı kullanılarak daha fazla düzenlenebilir. System Generator'ün bu özelliği, tasarımın sadece anahtar parçalara odaklanmasını sağlayabilir.

1.2 Model oluşturma

Şekil 1, model oluşturma, model simülasyonu, kontrolör dışa aktarımı ve deneysel doğrulama dahil olmak üzere Sistem Üreteci modelinden türetilen dönüştürücü kontrol blok diyagramını göstermektedir.

Bu makale, Sistem Üreticisi'ne dayalı denetleyici dışa aktarımını gerçekleştirmek için örnek olarak basit bir Boost boost devresini ele almaktadır. Yükseltici dönüştürücü giriş voltajını 12 V, çıkış voltajını 24 V ve anahtarlama frekansını 40 kHz olarak ayarlayın.

Xilinx modülleri kullanılarak oluşturulan simülasyon modeli iki bölüme ayrılmıştır: ana devre ve kontrol devresi. Ana devre, güç kaynağı, endüktans, kapasitans, yük ve anahtarlama cihazlarından oluşur ve kontrol devresi, Xilinx modülleri ile oluşturulmuş ayrı bir PI denetleyicidir. Ana devrenin çıkış voltajı örneklenir ve ardından kontrolöre gönderilir. Kontrolörün çıktı sonucu, ana devrenin anahtar tüpünün açılıp kapanmasını kontrol etmek için PWM darbe genişlik modülasyon dalgasını elde etmek için üçgen dalga ile karşılaştırılır, böylece sinyal geri besleme kapalı döngü işlemi gerçekleştirilir.

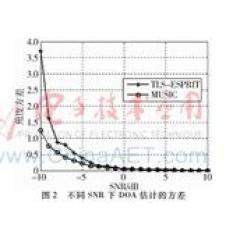

MATLAB-Xilinx modelinde, PI kontrol algoritmasının ayrıklaştırılması gerekir. Ayrık PI'nın iki yöntemi vardır: artımlı ve konumsal Denklemler (1) ve (2) 'de açıklandığı gibi, artımlı ayrık PI yalnızca cari dönem hatasını ve kullanımı daha uygun olan önceki dönem hatasını içerir. En yaygın kullanılan ayrık PI algoritmasıdır. Ancak, artımlı PI uygulaması, Xilinx modüllerinin kullanımı için ideal olmayan FPGA'daki kayıt döngüsü kaydırma ataması ile sınırlıdır. Bu makale konumsal ayrık PI algoritmasını seçer ve sürekli durumda integral fonksiyonunu gerçekleştirmek için ayrık durumda toplama modülünü kullanır. Biriktirme modülünün kendisi, Xilinx modüllerinin kullanımını büyük ölçüde azaltan sınırlı bir genlik işlevine sahiptir. Kontrolör modeli diyagramı Şekil 2'de gösterilmektedir.

Artımlı ayrık PI algoritması:

Konumsal ayrık PI algoritması:

Formülde Kp ve Ki sırasıyla orantılı kazancı ve integral kazancı temsil eder, u kontrol miktarını temsil eder, e kontrol miktarı ile verilen miktar arasındaki sapmayı temsil eder ve k farklı dönemleri temsil eder.

2 Simülasyon modeli doğrulama ve denetleyici dışa aktarımı

2.1 Simülasyon sonuçlarının karşılaştırmalı analizi

Simulink modülü tarafından oluşturulan denetleyicinin aksine, Xilinx modülü altındaki denetleyici, ayrık zaman modunda çalışan PI ayrık denklemleri kullanılarak oluşturulmuştur, bu nedenle ayrık denetleyicinin işlevsel doğrulaması özellikle önemlidir. Aynı zamanda System Generator modelinden türetilen dönüştürücü denetleyicinin tasarımına bağlı olarak nihai hedef, modül tarafından oluşturulan denetleyiciyi kullanım için bir IP çekirdeğine dönüştürmektir.Bu nedenle, Xilinx modülü tarafından oluşturulan denetleyicinin işlevinin FPGA'da normal olarak çalıştırılıp çalıştırılamayacağıdır Çok önemli kısım.

Yukarıda ortaya çıkan problemlere cevaben simülasyon çalışması MATLAB-Simulink ortamında, MATLAB-Xilinx ortamında ve donanım-in-the-loop ortamında gerçekleştirilmiş ve simülasyon sonuçları analiz edilmiştir: simülasyon sonuçlarının büyüklüğü açısından, çıktı sonuçları üç simülasyon modunda Udc'nin büyüklüğü aynıdır ve farklı şekillerde oluşturulan kontrolör simülasyon modellerinin aynı işlevi yerine getirebileceğini gösterir; algoritma yürütme ortamı açısından, aynı simülasyon sonuçları Xilinx modülü tarafından oluşturulan kontrolör algoritmasının FPGA'da normal şekilde çalışabileceğini gösterir; simülasyon sonuçları kararlıdır Durum açısından Simulink model çıktısı, Xilinx model çıktısından daha kararlıdır ve titreme yoktur. Analizden sonra, Xilinx modelindeki seğirmenin nedeni, System Generator tarafından kontrol edilen ve yönetilen Xilinx modülünün ayrık moddaki algoritma modülüne dayanması ve POWER GUI tarafından kontrol edilen ve yönetilen Simulink modülünün sürekli bir durumda çalışmasıdır. Sürekli model ve ayrık model birlikte çalışır ve çıktı sonucunda titremeye neden olur. Birlikte simülasyon, denetleyici IP çekirdeğinin hesaplamaları FPGA'da gerçekleştirdiğini ve ayrıca dalgalanmalar olduğunu fark eder.

2.2 Eş simülasyon analizi

Birlikte simülasyon ilkesi, bu belgede yer alan Sistem Üreteci modelinden türetilen dönüştürücü kontrol tasarımının merkezi fikri ile tutarlıdır ve odak noktası, dışa aktarma bağlantısındadır. Birlikte simülasyon sürecinde, Xilinx modülü tarafından oluşturulan kontrolör, Verilog dili altında entegre bir çekirdeğe aktarılır ve çekirdek, FPGA'daki kontrolör algoritmasının hesaplama sürecini tamamlar.

Co-simülasyon, Xilinx modülü tarafından oluşturulan kontrolörün en doğrudan doğrulama sürecidir.ZedBoard geliştirme kartının FPGA ortamında kontrol algoritması simülasyonunu gerçekleştirdiği için, ko-simülasyonun sonucu, kontrolör algoritmasının ve algoritmanın fonksiyonel doğrulamasının en gerçekçi uygulamasıdır. En iyi yol. Simülasyon modeli Şekil 3'te gösterilmiştir. Şekil 4, kontrol algoritmasının FPGA üzerinde çalışması sırasında veri geri bildirimini gerçekleştiren ortak simülasyon entegre çekirdeğini göstermektedir.

2.3 Model ihracatı

Xilinx modülleri tarafından oluşturulan denetleyici, Vivado tarafından System Generator aracılığıyla kullanılabilen IP çekirdeklerine aktarılabilir. IP çekirdeği yalnızca, GatewayIN / GatewayOUT ile bağlantı noktası parametrelerini tanımlayan Xilinx modüllerinden oluşan denetleyici bölümünü içerir. Bu bağlantı noktası parametreleri, giriş / çıkış verilerinin tipini, bit sayısını ve diğer bilgilerin yanı sıra ayrık simülasyon adım uzunluğu bilgilerini ayarlar. GatewayIN / GatewayOUT, harici verileri ve Xilinx modüllerini bağlamada önemli bir rol oynar. Dışa aktarım ortamındaki System Generator bilgileri Şekil 5'te gösterilmektedir. Şekildeki yazılım ayarı bilgilerinden, Boost dönüştürücünün kontrol sisteminin bir IP çekirdeği biçiminde ihraç edildiği ve sahip olunan FPGA yonga serisi için karşılık gelen geliştirme kartının seçildiği ve geliştirme ve tasarım için donanım olarak Verilog dilinin kullanıldığı görülebilir. Açıklama dili. Diğer seçenekleri varsayılan ayarlar olarak ayarlayın. Burada uygun bir dışa aktarma nesnesi ve dışa aktarma ortamı ayarlamak, tüm tasarımın önemli bir adımıdır.

2.4 Vivado yazılım işleme

System Generator tarafından bağımsız bir IP çekirdeği olarak dışa aktarılan Boost denetleyicisi Vivado yazılımı tarafından kullanılabilir ve çalıştırılabilir. Bu makalede Vivado yazılımı, Şekil 6'da gösterildiği gibi ana modül (XADC analogdan dijitale dönüştürme modülü, veri ayırma işleme modülü) ve kontrol modülü (IP çekirdeği) dahil olmak üzere Boost dönüştürücünün veri işleme modelini oluşturmak için kullanılır. Bunların arasında, analogdan dijitale dönüştürme, ZedBoard kartıyla birlikte gelen analogdan dijitale dönüştürücüyü kullanır ve analog girişi geliştirme kartına dijitale dönüştürmek için XADC kullanır. Veri ayırma modülü, XADC'den gelen veriler dağınık olduğu için mevcuttur (geliştirme panosu n-kanal verilerini girer ve XADC verileri 1 ... n.1 ... n formatında verir) Amacı, XADC tarafından dönüştürülen verileri etkili bir şekilde ayırmaktır. Sonraki işlemleri kolaylaştırmak için. Veri işleme modülü temel olarak dijital miktarı, sonraki PI kontrolü için gerçek analog miktara karşılık gelecek şekilde işler.

3 Deneysel doğrulama

Deney, ZedBoard geliştirme kartı platformundaki yüksek hassasiyetli AD dönüştürücüsünü kullanıyor ve devre tahtası üzerine inşa edilen Boost dönüştürücü, örnekleme ve koşullandırma panosu ile birlikte deney için kapalı döngü bir kontrol sistemi oluşturuyor.

Birincisi, klima panosu tarafından işlenen Boost ana devresindeki çıkış sinyalini örneklemektir. Koşullandırma kartından gelen sinyal, geliştirme kartında analogdan dijitale dönüştürme ve daha fazla veri işlemenin gerçekleştirildiği ZedBoard geliştirme kartına gönderilir.İşlem sonucu, PWM dalga çıkışını elde etmek için denetleyici IP çekirdeği Sistem Üreticisi aracılığıyla dışa aktarıldıktan sonra üçgen dalga ile karşılaştırılır. PWM dalgası tahrik devresinden geçer ve ardından Mosfet'in açılıp kapanmasını kontrol eder.

Tablo 1, Şekil 7'de gösterilen deneysel sonuçlarla bağlantılı olarak elde edilmiştir. Tablo 1'den görülebileceği gibi, Boost dönüştürücünün çıkış voltajı, 11,5 V'tan 15 V'a giriş değişikliği sırasında yaklaşık 24,2 V'ta stabilize edilebilir. Değişken yük testinde, çıkış voltajı 0,3 V hafifçe düştü.

4. Sonuç

MATLAB / Simulink ortamı ile birleştirildiğinde, simülasyon modelini oluşturmak için Xilinx tarafından sağlanan System Generator modül kitaplığını kullanın ve ardından Verilog donanım açıklama dili tarafından gerçekleştirilen IP çekirdeğinin kontrol sistemi tasarım yöntemini oluşturun, böylece FPGA tasarım geliştiricileri Simulink ve MATLAB simülasyon işlevini kullanabilir. FPGA sistem düzeyinde simülasyon ve davranış düzeyinde analiz için güçlü veri analizi özellikleri. Geçmişte kontrol sistemini yazmak için Verilog / VHDL dilinin doğrudan kullanımıyla karşılaştırıldığında, farklı bağlantılar arasındaki ara bağlantı doğrulama çalışmasını büyük ölçüde basitleştirir ve aynı zamanda işlevsel gerçekleştirmenin doğrulama verimliliğini artırır ve tasarım döngüsünü kısaltır. Bu tür tasarım esnekliği, gereksinimleri karşılarken ayrıntıları değiştirmek de kolaydır, böylece tasarlanan model yeniden kullanılabilir, bu da FPGA tasarımında yeni bir yöndür.

Referanslar

Bin He. Xilinx FPGA için yetkili tasarım kılavuzu: Vivado 2014 Integrated Development Environment Pekin: Electronic Industry Press, 2015.

Pang Shengzhao, Huangfu Yigeng, Guo Liang ve diğerleri.Yüksek frekanslı akım ileri besleme telafisini kullanan bir Boost dönüştürücü sistemi stabilizasyon yöntemi.Çin Elektrik Mühendisliği Derneği Bildirileri, 2016, 36 (20): 5616-5623.

ABBAS G, FAROOQ U, ASAD M U. Güç anahtarlama dönüştürücü için 1 serbestlik dereceli ayrık PID denetleyicinin tasarımı ve FPGA uygulaması. Endüstriyel Elektronik ve Uygulamalar. IEEE, 2012: 1070-1074.

KOCUR M, Kozak S, DVORSCAK B. FPGA-sayısal tabanlı PID kontrolör tasarımı ve uygulaması Kontrol Konferansı IEEE, 2014: 233-236.

Qian Weikang, Ni Yuanhong, Xie Kainian, vb. Xilinx System Generator tabanlı PID algoritmasının hızlı donanım gerçekleştirilmesi Elektronik Teknolojinin Uygulanması, 2011: 37 (11): 48-51.

Li Ning. Xilinx FPGA'ya dayalı elektromekanik sistem için akıllı kontrolör tasarımı ve uygulaması Jinan: Shandong Üniversitesi, 2010.

KIDOKORO H, NAKAHARA M. FPGA tabanlı yüksek anahtarlama frekanslı güç dönüştürücülerinin döngü içi donanım simülatörü.Uluslararası Telekomünikasyon Enerji Konferansı, IEEE, 2015: 1-6.

SOPHIA A S, BABU A R. Birleştirilmiş indüktör kullanılarak FPGA denetleyicisine dayalı yüksek yükseltmeli DC-DC Dönüştürücünün geliştirilmesi. 2016 İkinci Uluslararası Bilim Teknolojisi Mühendisliği ve Yönetimi Konferansı. IEEE, 2016: 377-382.

DUFOUR C, CENSE S, B? LANGER J. Yüksek bant genişliğine sahip HIL gerçek zamanlı simülatör için FPGA tabanlı anahtarlamalı relüktans motor sürücü ve DC-DC dönüştürücü modelleri.European Conference on Power Electronics and Applications.IEEE, 2013: 1-8 .

-

- L2 otonom sürüş, 630 km dayanıklılık, GAC New Energy Aion S piyasaya sürüldü | İlk satır otomobil haberleri

-

- İşyerinin seçkinlerini oluşturmaya yardımcı olun Haier Tianyue Y3C bilgisayarı Aralık ayı başlarında resmi olarak listelenecek