Çok Kanallı GNSS Veri Toplama Platformunun Tasarımı ve Uygulanması

Zhao Yudong, Qin Honglei, Zhang Koşusu

(Elektronik Bilgi Mühendisliği Okulu, Beihang Üniversitesi, Pekin 100191)

GNSS sistemlerinin gelişmesiyle birlikte, çok yollu etkiler giderek konumlandırma doğruluğunu ve güvenilirliğini etkileyen önemli faktörlerden biri haline geldi. Anten dizisi yöntemiyle çok yollu etkilerin ortadan kaldırılmasını doğrulamak için, birden çok anten tarafından alınan verilerin gerçek zamanlı eşzamanlı olarak alınması ve depolanması gerekir. Bu amaca ulaşmak için, sistem gereksinimlerini karşılayan bir veri toplama platformu tasarlamak ve uygulamak için PCIE iletişim veriyoluna ve çok kanallı AD toplama kartına dayalı FPGA geliştirme kartı kullanılır. İlk olarak, edinim platformunun yapısını ve PCIE iletişim bağlantısının kurulmasını kısaca tanıtır ve ardından bir sürekli veri depolama yöntemi tasarlar ve uygular.Son olarak, yöntemin uygulanabilirliği ve edinim platformunun genel performansı deneylerle doğrulanır.

Dizi anteni; PCIE veriyolu; AD edinimi; sürekli depolama

Çin Kütüphanesi Sınıflandırma Numarası: TN965

Belge tanımlama kodu: Bir

DOI: 10.16157 / j.issn.0258-7998.2017.07.016

Çince alıntı biçimi: Zhao Yudong, Qin Honglei, Zhang Runping.Çok kanallı GNSS veri toplama platformunun tasarımı ve uygulaması.Elektronik Teknoloji Uygulaması, 2017, 43 (7): 63-66.

İngilizce alıntı biçimi: Zhao Yudong, Qin Honglei, Zhang Runping.Çok kanallı GNSS veri toplama platformunun tasarımı ve uygulaması. Application of Electronic Technique, 2017, 43 (7): 63-66.

0 Önsöz

Şu anda, veri toplama teknolojisi radar, navigasyon, iletişim, görüntü işleme ve diğer alanlarda yaygın olarak kullanılmaktadır ve doğruluk ve güvenilirlik doğrulamasını kolaylaştırmak için çeşitli sistemler için gerçek ve etkili ölçülmüş veriler sağlamaktadır. Uydu navigasyonunda, çok yollu ve dizi anten yöntemini kullanarak parazit önleme üzerine teorik araştırma nispeten derinlemesine olmuştur, ancak ölçülen verileri toplamak ve sonuçları doğrulamak için donanım platformunu kullanma araştırması Çin'de hala nadirdir. Platformun, her bir anten elemanı tarafından alınan sinyalleri eşzamanlı olarak toplaması ve depolaması ve verilerin doğruluğunu ve güvenilirliğini sağlaması gerektiğinden, platformun çok kanallı bozulmasız yüksek hızlı veri toplama ve büyük kapasiteli veri depolama özelliklerine sahip olması gerekir. Bu sorunu çözmek için tasarım, daha yüksek aktarım hızına sahip PCIE seri veri yolunu benimser ve işlemci çekirdeği olarak Xilinx Kintex7-325T serisi FPGA yongasını kullanır, çok çeşitli uygulama değerine sahip çok kanallı yüksek hızlı GNSS veri toplama platformu tasarlar ve uygular. .

1 Genel sistem mimarisi

Bu yazıda tasarlanan çok kanallı uydu navigasyon edinme ve depolama sistemi, çok elemanlı anten dizileri, çok kanallı aşağı dönüştürme modülleri, yüksek hızlı A / D dönüştürme modülleri, FPGA'lar ve SATA sabit sürücülerden oluşur.Tüm sistem mimarisi Şekil 1'de gösterilmektedir.

Anten dizisi, GPSL1 ve Beidou B1 ve B3 gibi farklı yönlerden birden çok frekanstan sinyal alabilen 8 navigasyon ölçüm anteninden oluşur. Çok kanallı aşağı dönüştürme ekipmanı, her bir anten elemanı tarafından alınan radyo frekansı sinyali üzerinde alt dönüştürme işlemi gerçekleştirir ve ardından bunu her bir A / D edinim kanalına girer. Dijital ara frekans sinyali ara belleğe alınır ve FPGA içinde paketlenir ve ardından veriler, PCI Express sabit çekirdeği işlenerek PCIE veri yolundan PC belleğine yazılır ve son olarak tüm toplama ve depolama işlemini tamamlamak için masaüstü bilgisayarın katı hal sabit diskine taşınır.

2 Sistem donanım yapısı

2.1 Radyo frekansı ön ucunun tasarımı ve gerçekleştirilmesi

Bu tasarımda kullanılan alt dönüştürme kartı, laboratuvar tarafından bağımsız olarak geliştirilmiş bir üründür.Beidou ikinci nesil RNSS bölgesel sinyal alıcı radyo frekansı çipi ile çekirdek olarak B1, B2, B3 ve GPS L1, GLONASS L1, L2 frekans noktalarında sinyal alabilir ( Çipte yalnızca bir radyo frekansı kanalı vardır, yükseltme, frekans dönüştürme ve filtreleme gibi işlemlerden sonra, temel bant yongası tarafından kullanılmak üzere çıkış analog veya dijital ara frekans sinyalleri gibi işlemlerden sonra, SPI arabirimi ve S0, S1 kadran anahtarı seçim sinyali üzerinden çalışmak için frekans noktalarından birini seçin. SPI yazmacını ayarlayarak, çip üzerindeki kanalların genlik frekansı özellikleri BPSK-2, BPSK-10 ve MBOC (6, 1, 1/11) gibi farklı sinyal sistemlerine uyacak şekilde ayarlanabilir. Aşağı dönüştürme frekansı parametreleri Tablo 1'de gösterilmiştir.

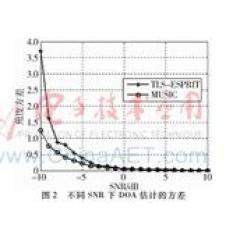

Çipin RF ön uç bant genişliği, RF ön uç filtresinin yayma kodunun korelasyon zirvesi üzerindeki etkisini azaltmak, böylece anti-çok yollu algoritma temel bant işlemesinin gereklerini karşılayacak şekilde yapılandırılabilir. Çip yapısı ve prensibi Şekil 2'de gösterilmektedir.

Anten dizisi anti-multipath algoritmasının aynı anda birden fazla IF navigasyon verisini işlemesi gerektiğinden, bu tasarımda 8 aşağı dönüşüm kartı aynı anda bir kasaya yerleştirilir ve tüm kartların güç kaynağı ve harici saat girişi sorunları çözülür. . Kasa düzeni Şekil 3'te gösterilmektedir.

2.2 AD edinim platformunun tasarımı ve uygulaması

Bu makalede tasarlanan edinme platformu, PCIE veri yolu tabanlı FPGA geliştirme kartı ve birden çok AD edinme yardımcı kartından oluşur. AD toplama panosunun ana işlevi, harici analog verileri toplamak, her AD örnekleme kanalının örnekleme saatini yapılandırmak ve verileri FMC arayüzü aracılığıyla FPGA'ya girmek; FPGA geliştirme kartının ana işlevi, veriler dahil olmak üzere AD tarafından veri girişini işlemektir. Biçim dönüştürme, arabelleğe alma ve PCIE veri yoluna paketleme ve gönderme, vb., İki kart FMC-HPC yüksek hızlı arabirim aracılığıyla bağlanır. FPGA geliştirme kartının blok diyagramı Şekil 4'te gösterilmektedir.

Kartın ana yongası Xilinx Kintex-7 FPGA xc7k325t-ffg900-2'yi benimser, yongada PCI Express Uç Nokta modülü, yüksek hızlı seri iletişim arabirimi, DDR3 bellek arabirimi ve özel G / Ç arabirimi bulunur. PCI Express 1/2/4/8 Lane'i destekler, PCI Express v1.1 / 2.0 ile uyumludur ve her şeridin aktarım hızı 2,5 Gb / s'dir. Tüm anakart DDR3 belleğinin toplam kapasitesi 1 GB'a ulaşır (2 GB'a kadar destekler). DDR3 SDRAM saati 303.03 MHz'e kadardır. DDR3 SDRAM parçacıkları 128 M × 16 bit kullanır. 4 DDR3 parçacığı 64 bit 1 GB önbellek oluşturur.

Bu tasarımda kullanılan AD yakalama kartı, 14 bit çözünürlük ve maksimum 250 MS / s örnekleme hızı ile ADS62P49 yongası kullanan 8 kanallı analogdan dijitale dönüştürücü (ADC) içeren bir FPGA ara kartıdır. ADC saat tasarımı, AD9516 yongası ile sağlanmaktadır. AD9516 referans saati 10 MHz'dir ve kart üzerindeki 10 MHz VCXO seçilebilir veya saat kartın dışından sağlanabilir. Kart, yüksek pin sayısı (HPC) konektörü kullanır ve giriş sinyali tek uçlu bir sinyal veya diferansiyel bir sinyal çifti olabilir. Kartın blok diyagramı Şekil 5'te gösterilmektedir.

3 PCIE DMA iletişim bağlantısının gerçekleştirilmesi

DMA kontrolörü, PCIE veriyolunu kullanarak yüksek verimli veri aktarımı için önemli bir araçtır. Bu tasarımdaki DMA kontrolörü, sürücünün kontrolü altında ADC FIFO'daki verilerin PC belleğine taşınmasından sorumludur.

Bu makaledeki DMA denetleyicisinin kodu, Xilinx tarafından sağlanan xapp1052 DMA demosuna göre değiştirilmiştir ve Şekil 6'da gösterildiği gibi esas olarak RX Motoru, TX Motoru ve EP_MEM'den oluşur. Bu makale yalnızca veri toplama ve alma ile ilgilendiğinden, yalnızca TX Motor modülü ve EP_MEM modülü açıklanmıştır.

3.1 TX_ENGINE Tasarımı

TX_ENGINE modülü, paketlenmiş verileri PCIE protokolüne göre arabelleğe almaktan ve PC belleğinin okunmasını ve yazılmasını ve PC isteklerine yanıtın gerçekleştirilmesi için PCIE arayüzünü PC'ye TLP göndermek için kontrol etmekten sorumludur.

3.2 EP_MEM'in Tasarımı

EP_MEM modülü, tüm FPGA'nın kontrol merkezidir.DMA kontrolü, veri toplama ve oynatma kontrolü, bu modülde uygulanmaktadır. Veriler toplandığında, adc_run_en'i ayarlayın, ADC çalışmaya başlar ve toplanan verileri TX FIFO'ya koyun. Ana kontrol Süreci, sürücü tarafından talep edilen verileri algılarsa ve TX FIFO'daki veriler 16 KB'den büyükse, bir Mwr DMA işlemi başlatır ve 16 KB'yi sürücünün arabelleğine taşır. Hareket tamamlandıktan sonra, sürücü işleminin tamamlandığını bildirmek için sürücü arabelleğinin ilk adresine sıfır olmayan bir veri yazın. Şekil 7, FIFO'dan bir seferde belleğe veri yazma işlemini göstermektedir.

4 Verilerin sürekli saklanmasının gerçekleştirilmesi

Toplanacak veri miktarı 1 GB'den az olduğunda, toplanan veriler bir bütün olarak hafızada saklanabilir ve ardından tek seferde dosyaya yazılabilir. Hafıza boyutunun sınırlandırılması nedeniyle, bir seferde yeterli depolama alanı açılamaz, ancak hafızayı birden çok kez açma işlemi kullanılabilir. Yani bir alan dolduğunda elde edilen veriler sabit diskteki hedef dosyaya yazılır; daha sonra bir alan bölümü tekrar açılır ve veriler yeni bellek alanına yazılır ve ardından veriler sabit diske aktarılır. Bu yöntem, büyük ölçekli bir depolama işlemini birden çok küçük ölçekli yazma işlemine dönüştürür ve sınırsız kapasiteye sahip bir depolama işlemi gerçekleştirir. Öte yandan hafızadan sabit diske her seferinde veri yazma süresini kısaltmak için her seferinde açılan hafıza alanı boyutu 16 KB olarak bulunur, yani hafıza FIFO'dan 16 KB veri okuduğunda hemen Sabit diskteki hedef dosyalar için, her bellek geliştirmesinin kesinti süresi ihmal edilebilir. Bu yöntemin süreci Şekil 8'de gösterilmektedir.

5 Sinyal edinme testi

5.1 Tek kanallı sinyal edinme testi

AD girişi olarak bir sinüs dalgası sinyali kaynağı kullanın, örnekleme oranını 62,5 MHz'e, niceleme bit sayısını 16 bit'e ayarlayın ve 1 MHz frekanslı bir sinüs sinyali toplamak için tek kanallı bir ADC kullanın ve ardından verileri PCIE veri yolu aracılığıyla sabit diske kaydedin. Veri görüntüleri yapmak için MATLAB kullanın ve sonuçlar Şekil 9'da gösterilmektedir.

Şekilden, sinyalin zaman alanında sürekli ve bozulmamış olduğu ve bariz bir parazit paraziti olmadığı görülebilir.

Daha sonra tek kanallı uydu navigasyon sinyalini test için veri kaynağı olarak kullanın. Sinyal kaynağı, uydu navigasyon simülatörü tarafından üretilen GPSL1 ara frekans sinyalidir Ara frekans 42.966 MHz, AD örnekleme hızı 62.5 MHz olarak yapılandırılmıştır ve depolama veri dosyası boyutu 20 GB'dir Elde edilen spektrum Şekil 10'da gösterilmektedir. Şekilden, ara frekans noktasının pozisyonunun önceden ayarlanmış değer ile tutarlı olduğu ve spektrum görüntüsünün GPSL1 sinyali BPSK modülasyon yasasına uygun olduğu görülebilir.

5.2 Genel sistem testi sonuçları

Test ekipmanının tamamı, gerçek sinyal doğrulaması için bir dış ortama yerleştirildi. Test yeri, Beihang Üniversitesi'nin yeni ana binasının büyük platformuydu ve test frekansı GPSL1 sinyaliydi. 8 enlem ve boylam kanalının ortalama ve standart sapmasının istatistiksel sonuçları Tablo 2'de gösterilmektedir. . Tablo 2'den, edinim platformu tarafından enlem ve boylamın iki boyutunda toplanan ve depolanan verilerin konumlandırma hatalarının hepsinin 10 m dahilinde olduğu ve GPS konumlandırma gereksinimlerini karşılayan rakım hatasının yaklaşık 20 m olduğu görülmektedir.

6. Sonuç

Uydu navigasyonunun anti-çok yollu algoritmasında aynı anda çok kanallı ham verilerin ihtiyacını karşılamak için, bu makale işleme çekirdeği olarak FPGA, yüksek hızlı iletişim ortamı olarak PCIE seri veri yolu ve depolama aygıtı olarak katı hal sabit diski ile yüksek hızlı bir çok kanal tasarlar ve uygular. Veri toplama ve depolama platformu. Sistemin kapsamlı bir testinden sonra, sonuçlar sistemin aynı anda çok kanallı uydu navigasyonunun gerçek verilerini doğru bir şekilde toplayıp depolayabildiğini göstermektedir. PCIE protokolünün çok yönlülüğü nedeniyle platform, PCIEx8 ve üzeri arayüzlere sahip herhangi bir PC sistemine uygulanabilir. Gelecekteki tasarımda, aynı anda çalışmak için birden fazla panoya genişletilebilir, bu da platformu daha fazla veri toplama ve depolama kanalı için uygun hale getirir ve geniş uygulama olanaklarına sahiptir.

Referanslar

BRAASCH M. DGPS yer referans istasyonları için optimum anten tasarımı ION GPS 1994. Salt Lake City, UT: 1994: 1291-1297.

NEHORAI A, PALDI E. Elektromanyetik kaynak yerelleştirme için vektör sensör dizisi işleme IEEE Aktarım Sinyal İşleme, 1994, 42 (2): 376-398.

MIRON S, MARS J I. Polarize sismik kaynakların lokalizasyonu için vektör sensörlü müzik.EURASIP Uygulamalı Sinyal İşleme Dergisi, 2005, 1 (1): 74-84.

Xia Yuwen Verilog Digital System Design Tutorial. Beijing: Beihang University Press, 2008.

Zhang Qin, Ma Youchun, Li Jinming PCI Express yüksek hızlı veri toplama kartına dayalı arayüz tasarımı Ölçme ve Kontrol Teknolojisi, 2010, 29 (2): 63-66.

Shen Hui, Zhang Ping, PCI Express veri yolu arabiriminde FPGA uygulaması Modern Elektronik Teknolojisi, 2010, 33 (14): 109-111.

Liu Ning. PCI Express arayüzüne dayalı yüksek hızlı veri aktarım sisteminin tasarımı ve uygulaması Taiyuan: Çin Kuzey Üniversitesi, 2008.

Xue Xiaogang, Ge Yimin. XilinxISE9.XFPGA / CPLD Tasarım Rehberi Pekin: Halk Mesajları ve Telekomünikasyon Basını, 2007.

Liu Kai, Xu Xin. Virtexs tabanlı PCI-Express veri yolu arayüz tasarımı Modern Elektronik Teknolojisi, 2005 (20): 107-109.

Shi Feng, Wu Jianfei, Liu Kai, vb. Xilinx FPGA'ya Dayalı PCIE Arayüzünün Uygulanması Mikroişlemci, 2008 (6): 18-22.

-

- L2 otonom sürüş, 630 km dayanıklılık, GAC New Energy Aion S piyasaya sürüldü | İlk satır otomobil haberleri

-

- İşyerinin seçkinlerini oluşturmaya yardımcı olun Haier Tianyue Y3C bilgisayarı Aralık ayı başlarında resmi olarak listelenecek