FPGA zamanlama yapısına dayalı LBT dönüştürme denetleyicisinin tasarımı

Görüntü, bilgi aktarımının önemli bir taşıyıcısıdır.Sosyal bilim ve teknolojinin ilerlemesiyle, insanlar, özellikle havacılık ve video güvenliği alanlarında görüntü kalitesi için gitgide daha yüksek gereksinimlere ve görüntü aktarımı ve depolama için daha yüksek gereksinimlere sahiptir. Bu nedenle, aktarım bant genişliğini arttırırken, özellikle JPEG serisinin geliştirilmesi başta olmak üzere, görüntü sıkıştırma ile ilgili araştırmalar da eş zamanlı olarak yürütülmektedir. 2009 yılında, JPEG XR (JPEG eXtended Range) resmi olarak piyasaya sürüldü. Üst üste binen biorthogonal dönüşüm (LBT) algoritmasını kullanıyor. Karmaşıklık JPEG'nin ayrık kosinüs dönüşümüne (DCT) eşdeğerdir, ancak geri yüklenen görüntünün kalitesi daha karmaşık Ayrık Dalgacık Dönüşümü (DWT), JPEG 2000 ile karşılaştırılabilir, bu nedenle kapsamlı bir şekilde incelenmiştir ve iyi uygulama olanaklarına sahiptir.

Doğrusal terfi yapısına dayalı geleneksel LBT dönüşümünün zamanlama kısıtlaması yoktur, katsayı dönüşümü yarı kararlı duruma sahiptir, veri kodu akışı kontrol edilmez ve doğrusal terfi yapısının çok sayıda çarpanı, bölücüsü ve kayma yazmacıları vardır, bu da FPGA donanım kaynakları için çok önemlidir. Çok pahalı. Bu makale, LBT'nin dönüşüm operatörü zamanlamasını yapmak ve el sıkışma sinyalleri aracılığıyla ön ve arka kontrol modülleri ile iletişim kurmak için FPGA'nın zamanlama kısıtlama özelliklerinden tam olarak yararlanır.FPGA'nın dahili alanını korumak için, kontrol talimatlarına göre kanal seçiciler kullanılarak tek bir RAM tasarlanmıştır, Farklı dönüştürme modülleri çalışırken, RAM ile RAM arasındaki kanalı açın ve diğer kanalları kapatın, dönüştürme katsayılarının karıştırılmasını önlemek için dönüştürme sırasına göre döngüsel olarak RAM'e okuyun ve yazın; kontrol modülü, okuma ve yazma için dönüştürme sırasına göre katsayı adresini gerçek zamanlı olarak hesaplar Operasyon, bu tasarım FPGA zamanlama özelliklerinin LBT dönüşümünü gerçekleştirir.

1 LBT prensibi ve JPEG XR analizi

1.1 LBT dönüşümünün bileşimi

JPEG XR kodlama işlemi, JPEG ve JPEG2000'e benzer, ancak işleme algoritmasını görüntü içeriğine göre gerçek zamanlı olarak ayarlayabilir, yani görüntü ön işleme, LBT dönüşümü, niceleme, uyarlamalı tahmin, uyarlamalı tarama ve uyarlamalı entropi kodlama dahil olmak üzere uyarlanabilir. 1 gösterilmektedir.

JPEG XR'nin güçlü uyarlanabilir kodlama yeteneğine ek olarak, en büyük fark, yalnızca JPEG'nin blok efekti sorununu çözmekle kalmayıp aynı zamanda eski ikisine göre en bariz avantajı olan karmaşık DWT algoritmasını da ortadan kaldıran LBT dönüşümü kullanımında yatıyor. LBT, görüntü blok efektlerini ortadan kaldırmak için kullanılan görüntü filtreleme dönüşümü (POT) ve görüntüyü uzamsal alandan frekans alanına dönüştürmek için kullanılan görüntü çekirdek dönüşümü (PCT) olan iki alt dönüşüm içerir.

1.2 LBT'nin dönüşüm operatörü ve prensibi

Tek kanallı görüntüler için, LBT'nin iki alt dönüşümü birkaç dönüşüm operatörü içerir. Bunlar arasında POT, 4 noktalı filtreleme (Tpre4) ve 4 × 4 filtreleme (T4mul4) olmak üzere 2 kategoriye ayrılmıştır. T4mul4, 5 dönüşüm operatöründen oluşur:

(1) 2 × 2 Hadamard Dönüşümü, operatör sembolü THEnc'dir;

(2) 2 noktalı ileri yakınlaştırma, operatör sembolü TS'dir;

(3) 2 nokta ileri dönüş, operatör sembolü TR'dir;

(4) 2 × 2 ileri dönüş, operatör sembolü TOddOdd'dir;

(5) 2 × 2 Hadamard dönüşümü, operatör sembolü TH'dir.

Ve Tpre4 sadece yukarıdaki TS ve TR'yi içerir, ancak aynı zamanda bazı işlemleri de vardır.

3 dönüştürme operatörüne sahip tek bir PCT türü vardır:

(1) 2 × 2 Hadamard dönüşümü, operatör sembolü TH'dir, bu T4mul4'ün TH'si ile aynıdır;

(2) Tek boyutlu dönüş dönüşümü, operatör sembolü TOdd'dir;

(3) İki boyutlu dönüş dönüşümü, operatör sembolü TOddOdd'dir ve bu, T4mul4'ün TOddOdd'sinden farklıdır.

1.3 LBT dönüşümünün görüntü üzerinde dağılımı

JPEG XR'de, görüntü işleme için döşemelere (Döşeme) bölünmemişse, LBT işlem aralığı görüntünün tamamıdır; görüntü parçalara bölünmüşse, LBT işlem aralığı döşemenin tamamıdır. Bir döşemeyi işledikten sonra bir sonrakine geçin. . Aşağıdaki açıklamanın rahatlığı için, resimler veya döşemeler toplu olarak işleme nesneleri olarak anılır. Bunların arasında, POT, işleme nesnesinin kenarında Tpre4'ü ve bunun içinde T4mul4'ü gerçekleştirir; PCT'nin çalışma aralığı her zaman tüm işleme nesnesidir.Şekil 2, LBT'nin POT ve PCT'sinin işleme nesnesi üzerindeki dağılımının şematik bir diyagramıdır.

2 FPGA zamanlama özelliklerinin dönüşüm operatörü

2.1 Geleneksel dönüşümlerle karşılaştırma ve dönüşüm operatörlerinin kapsüllenmesinin analizi

Bu makale, ITU kodlama önerisi LBT'nin her bir alt dönüşümünün sözde koduna atıfta bulunur ve FPGA zamanlama yapısına dayalı optimizasyon ve iyileştirme önerir. Tablo 1, teklifin TH operatörü sözde kodu ile FPGA zamanlama özelliklerinin TH operatörü arasındaki karşılaştırmadır. Adım, FPGA durum makinesindeki bir durumu temsil eder ve sonraki hesaplama, bu durumdaki veri işleme sürecidir ve teklifin sözde kodu bir satırdır Hesaplama bir adımı temsil eder FPGA zamanlama karakteristikleri altındaki TH operatör operasyon adımlarının sayısının teklifin sahte kodundan daha az olduğu ve bu da LBT dönüşümünün operasyon süresini azalttığı bulunabilir.

2.2 Dönüşüm operatörünün kapsüllenmesi

Şekil 3 TH operatör modülüdür.Kontrol modülü dönüştürülecek katsayıları giriş portuna gönderir ve daha sonra TH'ye bir istek gönderir TH veriyi alma talebini alır ve kontrol modülüne cevap gönderir; TH dönüşümü tamamlanır ve veri kontrol modülüne çıkış portuna gönderilir Bir işlem tamamlama talebi gönderin, kontrol modülü veri alma talebini alır ve TH'ye bir alım tamamlanma cevabı gönderir. Bu noktada, TH dönüşüm görevi tamamlanır ve bir sonraki dönüşüm veri girişi talepleri kümesini bekler.

3 FPGA tasarımı ve mantık analizi

3.1 FPGA üst düzey modül tasarımı

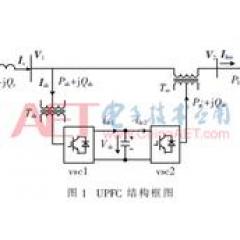

Sistem, analog görüntü kaynağı olarak FPGA dahili ROM'unu kullanır ve Şekil 4'te gösterilen 664 × 64 piksel test desenleri için başlatma dosyalarını oluşturmak ve depolamak ve bunları ROM'da depolamak için MATLAB kullanır. Şekil 5, analog kaynak, dönüştürme kontrolü, RAM ve kanal kontrolü ve paralelden seriye modüller dahil olmak üzere FPGA'nın üst düzey modül tasarımıdır.

3.2 LBT dönüştürme modülü tasarımı

Dönüştürme modülünde, tek bir RAM döngü yapısı LBT dönüştürme denetleyicisine ve RAM kanal seçiciye bölünmüştür, ikincisi, dönüştürme denetleyicisinin kanal denetim talimatına göre her alt dönüştürme ve RAM arasındaki iletişim üzerinde çapraz denetim gerçekleştirir. Dönüşüm kontrolörü, LBT'nin 4 alt dönüşümüne (birinci aşamada POT ve PCT, ikinci aşamada POT ve PCT) göre 4 bölüme ayrılmıştır ve her bölüm, kanal seçiciyi kontrol etmek için bir talimata sahiptir. RAM okuma ve yazma aynı anda yapılamadığından, RAM kontrolörü tarafından kanal kontrol talimatlarının, yani çapraz çalışan RAM'in serpiştirilmesinin dikkate alınması gerekir, böylece RAM kanalı aynı anda açılamaz.Şekil 6, RAM okuma ve yazma modülü tarafından kanal kontrolünün zamanlama analizidir. , İki kontrol modülünün aynı anda RAM kanalını açmasını önlemek için, yazma modülü kanalı kapattıktan sonra, okuma modülü RAM kanalını açmadan önce bir döngü (durum) bekler.

3.3 FPGA kontrol modülü iş akışı

Şekil 7, Şekil 2'deki üst Tpre4'ün ilk işlemesine göre POT okuma modülünün bir akış şemasıdır; daha sonra her 4 satırda, sol Tpre4 iki kez, orta T4mul4 ve sağ Tpre4 iki kez işlenir; alttaki Tpre4 en son işlenir. ROM'dan sıralı olarak görüntü verilerini okuyun. POT okuma modülü 4 Tpre4 veya 16 T4mul4'ü işledikten sonra, son dönüştürme katsayısı adresini POT yazma modülüne gönderir, ikincisi POT dönüştürülmüş katsayıları alır ve ardından sonuçları adresin tersi sırasına göre RAM'e kaydeder. POT son talimatını aldıktan sonra, PCT okuma modülü Şekil 8'de gösterildiği gibi PCT dönüşümü için raster tarama sırasında RAM'den 4 × 4 katsayıları okumaya başlar. PCT okuma modülünün işlenmesi tamamlandıktan sonra, ilk dönüşüm katsayısının adresini PCT dönüşüm yazma modülüne gönderir.İkincisi, PCT dönüştürülmüş katsayıları aldıktan sonra, dönüşüm sonuçlarını Şekil 9'da gösterildiği gibi raster tarama sırasında RAM'e kaydeder. .

4 FPGA simülasyonu ve sonuç analizi

4.1 FPGA çevrimiçi simülasyon

Bu makale FPGA tasarım doğrulaması için Signal Tap kullanır.Şekil 10, analog kaynak modülünün veri adresinin bir kısmının simülasyonunu gösterir.A, aynı zamanda Tpre4'ün ilk dönüştürme katsayısı olan birinci ila dördüncü katsayılardır; B, ilk T4mul4'tür 16 Katsayıları dönüştürün.

Örnek olarak TR operatörünü ele alalım Şekil 11, POT'un TR operatör dönüşümünün bir simülasyon diyagramıdır. A, kontrol modülü tarafından gönderilen giriş talebi ve TR operatörünün yanıtı ve B, TR operatör dönüşümü tarafından gönderilen talep ve kontrol modülüdür. Cevap geri döndü.

Şekil 12, RAM kontrol modülü çalışma simülasyonudur.A'da, T4mul4 modülü RAM yazma kontrol modülüne bir yazma talebi gönderdikten sonra, modül RAM kanal kontrolörünü açar, POT dönüştürme sonucunu B'deki RAM'e yazar ve C'deki kanalı kapatır. Signal Tap ile simülasyon doğrulaması, FPGA zamanlama kısıtlamaları altında LBT dönüşümünün kontrol edildiğini gösterir.

4.2 LBT dönüşüm sonuçlarının karşılaştırmalı analizi

İkinci PCT dönüşümü tamamlanır ve tüm LBT dönüşümü sona erer Bu zamanda, nihai dönüşüm sonucu RAM'de saklanır ve paralel dönüşüm modülü RAM'den okur ve bunu CP2102 üzerinden 9600 b / s hızında ana bilgisayarın seri port hata ayıklama yardımcısına gönderir; Verileri bir txt dosyası olarak kaydedin ve verileri yeniden yapılandırmak için MATLAB kullanın. Şekil 13'ün her bir alt resminde, soldaki resim, MATLAB test çizelgesinin LBT simülasyon sonucudur ve sağdaki resim, FPGA'nın LBT işleme sonucudur. Test sonuçları, FPGA'nın LBT dönüşüm sonucunun MATLAB simülasyon sonucuna benzer olduğunu ve FPGA zamanlama yapısının LBT dönüşümünün temelde gerçekleştiğini göstermektedir.

5. Sonuç

Bu makale, tek bir RAM döngüsü depolama yapısının FPGA zamanlama özelliklerine dayalı bir LBT dönüştürme algoritması önermektedir. Geleneksel doğrusal kaldırma yapısıyla karşılaştırıldığında, bu algoritma dönüştürme sürecini gerçek zamanlı olarak kontrol edebilir ve kod akışı karışıklığını önlemek için hibrit durum makinesini zaman sırasına göre ilerlemek için kullanabilir ve son olarak LBT dönüştürme sonucunu elde edebilir. Ancak bu tasarımın katsayı doğruluğu yeterli olmadığından ve yalnızca tek kanallı görüntü dönüşümünü desteklediğinden, dönüşüm katsayılarının doğruluğunu artırarak LBT dönüşümünün kalitesini ve hızını artırmak ve çok kanallı görüntü (renkli görüntü) dönüşümünü gerçekleştirmek bir sonraki araştırma yönü olacaktır.

Referanslar

Qi Zhiheng, Jiang Zhe, Zhang Wei.ADV212'ye dayalı Radar görüntü sıkıştırma iletim sistemi. Elektronik Teknoloji Uygulaması, 2015, 41 (11): 78-80, 84.

Zhang Huihui. FPGA tabanlı JPEG sıkıştırmalı kodlayıcının tasarımı ve uygulaması. Taiyuan: Çin Kuzey Üniversitesi, 2017.

Liu Zhiyuan, Chen Yaowu. Sübjektif kaliteye dayalı JPEG XR niceleme parametresi seçimi Bilgisayar Mühendisliği, 2014, 40 (1): 239-245.

HORVATH K, STOGNER H, UHL A. JPEG XR sıkıştırma ayarlarının iris tanıma sistemleri üzerindeki etkileri. Görüntü ve Desenlerin Bilgisayar Analizi, Uluslararası Konferans, Caip 2011, Seville, İspanya, 29-31 Ağustos 2011, Proceedings.DBLP, 2011: 73-80.

PAN C, CHIEN C, CHAO W, ve diğerleri.Dijital fotoğrafçılık uygulamaları için tam HD JPEG XR kodlayıcının mimari tasarımı Tüketici Elektroniği IEEE İşlemleri, 2008, 54 (3): 963-971.

Wu Chunming, Jiao Longlong, Zhang Jinqiang. Görüntü dokusu özelliklerine dayalı JPEG-XR iç tahmin teknolojisi. Journal of Northeastern Normal University (Natural Science), 2016 (1): 54-59.

IIDA K, KOBAYASHI H, KIYA H.JPEG XR görüntüleri için bulanık taahhüt şemasına dayalı güvenli kimlik. Signal Processing Conference. IEEE, 2016: 968-972.

ZHONG G, CHENG L, CHEN H. Tamsayı bindirilmiş biortogonal dönüşüm Uluslararası Görüntü İşleme Konferansı IEEE, 2001: 471-474.

MALVAR H S. Azaltılmış engelleme ve çınlama artefaktları ile dönüşüm kodlaması için üst üste bindirilmiş biortogonal dönüşümler IEEE Uluslararası Akustik, Konuşma ve Sinyal İşleme Konferansı IEEE, 1997: 2421-2424.

YU L. Video gözetimi için optimize edilmiş JPEG XR'nin değerlendirilmesi ve uygulanması. İsveç: Linkopings Üniversitesi, 2010.

SUZUKI T, YOSHIDA T. JPEG XR standardı ile son derece uyumlu hiyerarşik üst üste binmiş dönüşümler için daha düşük karmaşıklık kaldırma yapıları. Video Teknolojisi için Devreler ve Sistemlerde IEEE İşlemleri, 2017, 27 (12): 2652-2660

yazar bilgileri:

Gu Zeling, Yang Mingyuan, Ding Honghui, Heng Yan

(Şangay Radyo Ekipmanı Enstitüsü, Şangay 200090)

-

- 2019 OPPO İnovasyon Konferansı, mobil fotoğrafçılık deneyiminde devrim yaratmak için 10x hibrit optik yakınlaştırma teknolojisini sergiliyor

-

- Natalie Portman, yayınlanan en güzel "First Lady" filminde rol aldı ve doğrudan Kendini'nin suikastına isabet etti.

-

- Silahlı Polis Yueyang Müfrezesi: Ching Ming Festivali'nde silah ateşleyerek "Haiti Ruhuna" haraç ödemek