Yüksek kare hızlı görsel gerçek zamanlı hedef tespit sistemi

Makine görüşüne dayalı akıllı hedef tespit sistemleri, özellikle yüksek hızlı hedeflerin gerçek zamanlı tespitini ve kontrolünü içeren ve hedef tespitin istihbarat ve gerçek zamanlı performansı için daha katı gereklilikler ortaya koyan havacılık ve askeri endüstrilerde yaygın olarak kullanılmaktadır. Bu uygulamada görsel sistem, radar ve sonar ile karşılaştırıldığında büyük miktarda bilgi, güçlü parazit önleme yeteneği, esnek yazılım işleme, küçük boyut ve ağırlık ve düşük maliyet özelliklerine sahiptir, ancak dezavantajı, iletim ve işleme için daha fazla zaman almasıdır, bu nedenle çok Görüntü bilgisi aktarımı ve işlemesinin gerçek zamanlı gereksinimlerini karşılamak zordur.

Genel olarak görüntü toplanır ve GigE, Camera Link, USB3.0 vb. Arayüzler aracılığıyla görüntü işlemciye iletilir. Bu yöntem bilgi aktarım kanalına çok zaman harcar. Bu sorunu çözmek için en iyi yol, sensör çipi tarafından toplanan görüntüleri doğrudan proksimal uçta işlemektir. Donanım paralel hesaplamanın avantajlarına dayanan FPGA'lar, yüksek hızlı kameralarda ve yüksek hızlı hareket algılama sistemlerinde giderek daha fazla kullanılmaktadır, bu da görüntü işleme hızını büyük ölçüde artırır ve sistemin yüksek hızlı, gerçek zamanlı ve doğruluğunu sağlar. Görüntü sensörünün FPGA aracılığıyla yakın uçta işlenmesi, görüntü alma ve akıllı işlemenin senkronizasyonunu sağlayabilir. Çözülmesi gereken en önemli sorun, hesaplamayı daha basit ve daha verimli hale getirmek ve daha az kaynak kullanmak için akıllı algoritmayı optimize etmektir.

Şu anda, birçok bilim insanı, yüksek hızlı görsel hedef tespit sistemi araştırması üzerinde çalışıyor. GU Q Y ve diğerleri, hedefi gerçek zamanlı olarak akıllı bir şekilde izleyebilen 2.000 f / s'lik yüksek hızlı bir akıllı kamera tasarladı. Daha sonra, yüksek kare hızlı bir video ekleme sistemi tasarlandı.Sistem, panoramik görüntüleri gerçek zamanlı olarak 500 f / s kare hızıyla sentezleyebilen gelişmiş bir özellik tabanlı video ekleme algoritması kullanıyor. CHEN JG ve Massachusetts Institute of Technology'den diğerleri, hedef nesnenin konsol kirişindeki yer değiştirmesini ölçmek için yüksek hızlı bir kamera (5000 f / s) kullandılar ve verileri PC aracılığıyla çevrimdışı olarak analiz ettiler ve ölçümü lazer titreşim ölçer ve ivmeölçer ile elde ettiler. Tutarlı titreşim eğrisi. Ve FFT algoritması aracılığıyla, üç veri seti frekans alanında analiz edilir ve her bir rezonans frekansı bileşeni elde edilir.

Bu makale, araştırma için başlangıç noktası olarak yüksek kare hızı ve gerçek zamanlı performansı alıyor ve çipteki FPGA kaynaklarını ve hedef çıkarma ve merkez algılama algoritmalarını uygulamak için donanım paralelliğinin avantajlarını tam olarak kullanan ZYNQ7000'e dayalı yüksek hızlı bir kamera platformu tasarlıyor. Bu makale, hedef algılamanın FPGA algoritmasını optimize eder, ara tampon bağlantısını kaldırır ve görüntü verilerinin gerçek zamanlı iş hattı işlemesini gerçekleştirmek için bir boru hattı yapısı kullanır; bu, hedef algılama algoritmasının işleme verimliliğini artırır ve her görüntü edinme karesinden sonra sınırlı bir saat döngüsü içinde konum algılamayı tamamlayabilir. Eşzamanlı algılama elde etmek için hesaplayın. Deneysel sonuçlar, sistemin 560 × 480 çözünürlük, 1100 f / s ve 3 piksel doğruluğu ile gerçek zamanlı hedef tespiti yapabildiğini göstermektedir.

1 donanım sistemi tasarımı

1.1 Sistem bileşimi

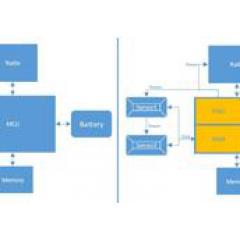

Yüksek hızlı gerçek zamanlı gereksinimleri karşılamak için, bu sistem, yakın uç işleme elde etmek için yüksek hızlı CMOS sensörlerini doğrudan çalıştırmak için FPGA kullanır. Algılama sistemi, Şekil 1'de gösterildiği gibi temel olarak FPGA ana kontrol ünitesi, CMOS görüntü toplama ünitesi, çoklu güç rayı güç kaynağı ünitesi, harici arayüz ünitesi ve optik görüntüleme ünitesinden oluşur.

FPGA ana kontrol ünitesi, ARM sert çekirdeği ve FPGA kaynaklarını entegre eden ZYNQ7020 yongasını kullanır. ARM, CMOS sensörünü yapılandırmaktan sorumludur ve FPGA, elde edilen görüntü üzerinde veri işlemeyi gerçekleştirir, hedef algılama algoritmasını uygular ve görüntü ve konum bilgilerini verir.

CMOS görüntü toplama birimi, 640 × 480 çözünürlüğe sahip bir Python300 gri tonlamalı CMOS sensörü kullanır; bu, 815 f / s'lik tam çözünürlüklü bir çıktı elde edebilir ve pencereleme (ROI) işlemi aracılığıyla kare hızını daha da artırabilir.

Harici arabirim birimi, görüntü görüntüleme, konum koordinat iletimi, hata ayıklama ve indirme işlevlerini gerçekleştirebilen HDMI ekran arabirimi, seri bağlantı noktası, JTAG arabirimi ve diğer devreleri içerir.

1.2 Donanım tasarımı

Sistemin donanım devresi iki parça halinde tasarlanmıştır: FPGA ana kontrol kartı ve yüksek hızlı arka panel İkisi birbirine bağlıdır ve standartlaştırılmış yüksek hızlı konektörler aracılığıyla sinyal iletilir. Ana kontrol panosu, bitmiş bir yüksek hızlı FPGA çekirdek kartı kullanır ve alt kart, CMOS devrelerini, HDMI ekran devrelerini, güç devrelerini, seri bağlantı noktalarını vb. Entegre eden 4 katmanlı bir PCB kartı tasarımı kullanır.

Alt panel tasarımı, esas olarak, devrenin yukarıda belirtilen parçalarının makul bir şekilde düzenlenmesi ve kablolanmasını gerçekleştirmektir. Bunların arasında, CMOS sensör düşük voltajlı bir diferansiyel sinyal (Düşük Voltaj Diferansiyel Sinyal, LVDS) çıkardığı için, her kanalın veri hızı 720 Mb / s'ye ulaşabilir, bu nedenle tasarım sırasında sinyal bütünlüğü dikkate alınmalıdır.

Sinyal, kablolama sırasında özel olarak işlenir ve yüksek hızlı diferansiyel hatların kurallarına sıkı sıkıya uyulur: her bir diferansiyel hat çifti paralel olarak bağlanır, mümkün olduğunca aynı minimum mesafe ve hat genişliğinden daha az; yolların sayısını azaltır; 90 ° 'den daha büyük kablo köşeleri; Diferansiyel empedans, sinyal yansımasını azaltmak için diferansiyel sinyal alıcı ucunun 100 sonlandırma direnci ile eşleşen 100 'da kontrol edilir; her bir diferansiyel hat grubunun kablo uzunluğu olabildiğince tutarlı tutulmalıdır; her bir diferansiyel hat grubu arasındaki mesafe büyük tutulmalıdır.

Yukarıdaki önlemlerle, yüksek hızlı diferansiyel sinyalin sinyal bütünlüğü ve her sinyal grubunun küçük gecikme farkı garanti edilir.

2 Yazılım sistemi tasarımı

Yazılım tasarımı temel olarak iki işlevi gerçekleştirir: denetimi etkinleştirmek ve yapılandırmayı kaydetmek. Etkinleştirme denetimi, ARM işlemcisinin IO işlemi aracılığıyla CMOS'un saatini ve güç kaynağını kontrol eder; kayıt yapılandırması, ARM'nin SPI veri yolu IP çekirdeği aracılığıyla CMOS sensörüyle iletişim kurması ve pencere boyutu, görüntü derinliği ve çalışma modu dahil olmak üzere bazı gerekli kayıtları yapılandırmasıdır. , Görüntü veri çıkışı vb.

CMOS dahili kaydını yapılandırarak CMOS sensörü, veri işleme ve algoritma uygulaması için LVDS arabirimi aracılığıyla FPGA'ya iletilen, 8 bit derinliğe, 560 × 480 çözünürlüğe ve 1000 f / s'ye sahip yüksek hızlı bir video akışı görüntüsü çıkarabilir.

Sinyal işleme ve algılama algoritmalarının 3 FPGA uygulaması

3.1 Hedef algılama ilkesi

3.1.1 Hedef çıkarma

Hedef tespiti için, öncelikle görüntüdeki hedefi ve arka planı ayırt etmek ve çıkarmak gerekir. Uygulama senaryoları ile birlikte bu sistem, hedefi çıkarmak için arka plan farkı artı eşik segmentasyonu yöntemini seçer.

Önce net ve sabit bir arka plan görüntüsü elde edin ve ardından fark işlemini tamamlamak için mevcut çerçeve görüntüsü ile arka plan görüntüsünün karşılık gelen piksel değeri arasındaki farkı yapın. Daha sonra fark, belirlenen eşik ile karşılaştırılır, eşikten büyükse 1 olarak değerlendirilir, yani ön plan hareket ediyor demektir; aksi takdirde 0'dır, yani arka plan arka plan demektir ve ikili bir görüntü oluşturulur.

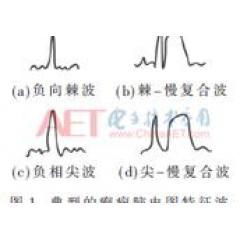

3.1.2 Centroid algılama

Bu sistem tarafından tespit edilecek hedef bir küredir Eşik segmentasyonundan sonra ikili görüntüde hedef dairesel bir parlak nokta olarak görünür. Hedefin özelliğini ve FPGA boru hattı yapısının özelliklerini dikkate alan bu makale, dairenin merkezinin konumunu belirlemek için çapın X yönünde ve Y yönünde olduğu düz çizginin kesişimini bulmak için daire çapı algılama yöntemini kullanır.

Spesifik yöntem Şekil 2'de gösterilmektedir: İkilileştirilmiş görüntünün her satırının piksel gri değerlerinin eklenmesi ve ikisinin toplamının karşılaştırılması, çapın bulunduğu satırda maksimum bir değer üretilecektir. Satırların sayısı, dairenin merkezinin Y koordinatı olarak kabul edilir. Sütun yönündeki aynı işlem X koordinatını da alabilir.

Daire çapı algılama ve daire merkezinin hesaplanması yöntemi, görüntüyü okurken görüntüyü işlemek ve çözmek için FPGA boru hattı yapısı ile işbirliği yapar, bu da algılama gecikmesini en aza indirebilir ve gerçek zamanlı performansı artırabilir.

3.2 FPGA mantık tasarımı

CMOS sensör görüntü verilerinin iletimi, soldan sağa ve aşağıdan yukarıya satır satır gerçekleştirilir ve her 8 piksel, çekirdek adı verilen bir gruptur. Hedef kare hızı nedeniyle > 1000 f / s, kare başına görüntü güncelleme döngüsü < 1 ms'dir ve çoğu zaman görüntüyü elde etmek için kullanılır ve görüntü önbelleğe alma ve işleme süreci geçerli çerçeve süresi içinde tamamlanamaz.

Bu sistem, FPGA paralel işleminin özelliklerinden tam olarak yararlanır.Mantık tasarımı, Şekil 3'te gösterildiği gibi üç aşamalı bir boru hattı yapısını benimser ve ara tampon bağlantısını kaldırır.Görüntü okurken, her bir veri grubu, aşamalı olarak işlenmek üzere doğrudan boru hattına gönderilir. Ardışık düzen, aynı anda üç veri grubunu işleyebilir ve her gruptaki 8 pikselin işlemleri de eşzamanlıdır. Bu şekilde, görüntü okuma ve işleme süreci eşzamanlı olarak gerçekleştirilir ve veri işlemenin verimliliği ve gerçek zamanlı performansı sağlanır.

Üç aşamalı boru hattı yapısı, hedef tespitinin üç aşamasına karşılık gelir ve mantık tasarımı aşağıdaki gibidir:

(1) Arka plan farkı

Mevcut çekirdek değerini elde ederken, arka plan çerçevesinde karşılık gelen adresin arka plan çekirdek değerini okuyun ve aynı anda 8 piksel değerine karşılık gelen farkı yaparak her bir piksel konumunun fark değerini elde edin, fark değeri kaydında saklayın ve bir sonraki seviyeye girin Akar su. Ardından, görüntünün tamamı okunana kadar hemen sonraki çekirdeğin piksellerini işleyin.

(2) Eşik segmentasyonu

Fark kaydı güncellendikten sonra, 8 piksel fark değeri ayarlanan eşik değeriyle karşılaştırılır Fark değeri eşik değerinden büyükse, ikilileştirme yazmacının karşılık gelen konumundaki piksele maksimum değer atanır, aksi takdirde 0 değeri atanır ve sonuç, boru hattının bir sonraki aşamasına girilir. Ardından bir sonraki çekirdek segmentasyonuna geçin.

(3) Centroid algılama

Ağırlık merkezi algılama mantığı, sırasıyla hedef ağırlık merkezinin X koordinatını ve Y koordinatını hesaplayan iki kola bölünmüştür.

X koordinatını hesaplama mantığında, 560 sütun ekleme kaydı ayarlanır ve ikilileştirme yazmacı her güncellendiğinde, ilgili sütunun sütun ekleme kaydına 8 ikili piksel değeri eklenir. Tam bir çerçeve görüntüsünü okurken, maksimum değeri ve X koordinatı olan ilgili sütun numarasını elde etmek için her bir sütunun ekleme kayıtlarının değerlerini karşılaştırın.

Y koordinatını hesaplama mantığında, biri geçerli satırın piksel değerlerinin toplamını ve diğeri satırın piksel toplamının maksimum değerini saklar. Bir satırı okuduktan sonra, toplam kayıt değerini maksimum toplam kayıt değeri ile karşılaştırın.Maksimum toplam değerden büyükse, maksimum toplam değeri satır toplam değerine güncelleyin ve bu sırada satır sayısını kaydedin; aksi takdirde Maksimum toplam değeri ve karşılık gelen satır sayısını değiştirmeden tutun. Bir görüntü çerçevesini okuduktan sonra, maksimum toplam değerine karşılık gelen satır sayısı, ağırlık merkezinin Y koordinatıdır.

4 Sistem testi ve sonuç analizi

4.1 Test ortamı

Kamera, kamerayı sabit tutmak için optik bir düz panel ile sabitlenir; arka plan olarak beyaz A4 kağıtla, algılama hedefi siyah bir karbon topudur; lens, odak uzaklığı 6 mm olan endüstriyel bir mercektir ve mercek ile hedef arasındaki mesafe 20 cm'dir ve test sırasında ışığı doldurmak için düz LED ışık kullanılır . Test, esas olarak doğruluk testi ve hız testi olarak ikiye ayrılır.

4.2 Doğruluk testi

Kamera açıldıktan sonra, önce arka plan çerçevesi olarak 500 kare görüntü toplayın. Ardından hedefi arka plan kağıdına sabitleyin ve tek noktalı edinme doğruluğunu test etmek için sürekli olarak 10.000 kez örnekleyin ve görüntüyü çizmek için hedef konumu seri bağlantı noktasından çıkarın. Deney 10 kez tekrarlandı ve test sonucu Şekil 4'te gösterildi. Test edilen tek nokta doğruluğunun tipik değeri 3 × 3'tür (piksel).

4.3 Hız testi

4.3.1 Kare hızı testi

Kamera 8 bit derinlikte ve 560 × 480 çözünürlükte çalışırken teorik kare hızı 1164 f / s'dir. Kare hızı şu şekilde test edilir: sistemi çalışma moduna getirin, koordinat verilerini almak için seri port aracını açın ve aynı zamanda zamanlama yapın, kare hızını belirli bir süre içinde alınan koordinatların sayısına göre hesaplayın.

Deneysel sonuçlar aşağıdaki gibidir: Sistem 10 saniye çalışır, 11871 koordinat verisi alır ve ölçülen kare hızı 1187 f / s'dir. Zamanlama hatasını hesaba katarak, ölçülen kare hızının temelde sistem tasarım gereksinimlerini karşılayan teorik kare hızıyla aynı olduğu sonucuna varılabilir.

4.3.2 Egzersiz testi

Sistem hareket testi, hedef nesnenin serbest düşme süreci tespit edilerek gerçekleştirilir. Hedef statik bir durumdan serbestçe düşer ve sistem tüm süreci yakalar ve gerçek zamanlı konumu seri bağlantı noktasına gönderir. Alınan konum koordinatlarının analiz edilmesiyle, Şekil 5'te gösterilen hareket yörünge diyagramı ve Şekil 6'da gösterilen Y-ekseni yönü yer değiştirme-zaman ilişkisi diyagramı elde edilir.

Şekil 6'dan, yer değiştirme eğrisinin eğiliminin temelde teorik eğri ile aynı ve teorik değerden biraz daha küçük olduğu görülebilir. Test sırasında hedefin gerçek düşme mesafesi 60 mm ve teorik düşme süresi 0,11 sn olmalıdır. Gerçek ölçümde, sistem 140 kare görüntü toplamıştır ve gerçek düşme süresi 0,12 sn'dir, bu da teorik süreden 0,01 sn daha uzundur.

Test sonuçlarını analiz edin: İlk olarak, hava direncinin serbest düşme hareketi üzerindeki etkisini göz önünde bulundurun, bu da ivme değerinin yerçekimi ivmesinden daha az olmasına ve ardından yer değiştirmenin teorik değerden daha az olmasına neden olur. Ek olarak Şekil 5'den düşme yönünün Y koordinat yönüyle tam olarak çakışmadığı ve X yönünde bir yer değiştirme olduğu, dolayısıyla Y yönündeki yer değiştirmenin beklenen değerden daha az olduğu görülmektedir. Yukarıdaki iki faktörün etkisi dikkate alındığında, kameranın nesnenin yüksek hızlı hareket sürecini doğru bir şekilde algıladığı düşünülebilir.

5. Sonuç

Bu makale, donanım tasarımı, yazılım yapılandırması ve FPGA algoritması uygulamasından tanıtılan yüksek kare hızlı görsel gerçek zamanlı hedef algılama sistemi geliştirmiştir. FPGA'nın yakın ucunda doğrudan akıllı işleme stratejisi benimsenmiş ve yüksek hızlı akıllı görsel denetim sisteminin gerçek zamanlı sorununu büyük ölçüde çözen boru hattı işlemenin yapısı tasarlanmıştır. Son olarak, sistem test edildi ve sonuçlar, sistemin 560 × 480 çözünürlük ve 1100 f / s yüksek hızlı video akışında 3 piksel hassasiyetle gerçek zamanlı hedef tespiti yaptığını gösterdi. Sistem, yer değiştirme hızı ölçümü, titreşim analizi, yüksek hızlı hedef izleme ve kontrol gibi çeşitli yüksek hızlı algılama senaryolarına uygulanabilir. Takip çalışması, optimizasyon algoritmasını geliştirecek, algılama doğruluğunu iyileştirecek ve onu dairesel hedeflerden düzensiz hedeflere genişletecektir. , Arka plan değiştiğinde algılama sağlamlığını geliştirin.

Referanslar

Du Jianbao, Zhang Zufeng. FPGA tabanlı hareketli hedef tespit sisteminin tasarımı. Enstrüman kullanıcısı, 2018 (3): 40-42.

Wang Xiaojuan, Zhai Chengrui.FpGA ve Sobel algoritmasına dayalı gerçek zamanlı görüntü kenarı algılama sisteminin tasarımı ve uygulaması. Bilgisayar Ölçümü ve Kontrolü, 2017, 25 (1): 34-37.

Qian Feng, Yang Mingyu, Li Gang, vb DSP + FPGA Mimarisine Dayalı Kedi Gözü Hedef Hızlı Algılama Sistemi Optoelektronik · Lazer, 2016 (8): 863-869.

Wen Jie, Li Jinming. FPGA'ya dayalı gerçek zamanlı bir görüntü kenarı algılama sisteminin uygulanması. Application of Electronic Technology, 2015, 41 (10): 65-67.

Shao Peng, Yang Chen, Zhang Jinmin. FPGA tabanlı uyarlanabilir eşik hareketli hedef algılama. Applied Optics, 2017, 38 (6): 903-909.

Zhang Hao. Düşük irtifa hedef tespit radarı yüksek hızlı hedef tespit ve izleme teknolojisinin araştırılması ve uygulanması Chengdu: Çin Elektronik Bilim ve Teknoloji Üniversitesi, 2016.

ISHII I, TATEBE T, GU Q Y ve diğerleri. Yüksek kare hızında video kaydı ile 2000 fps gerçek zamanlı görüş sistemi IEEE Uluslararası Robotik ve Otomasyon Konferansı Bildirileri, 2010: 1536-1541.

OKUMURA K I, RAUT S, GU Q Y, ve diğerleri. 500 fps'de gerçek zamanlı özellik tabanlı video mozaikleme. IEEE / RSJ Uluslararası Akıllı Robotlar ve Sistemler Konferansı. IEEE, 2014: 2665-2670.

CHEN J G, WADHWA N, CHA Y J, et al.Hareket büyütme kullanarak yüksek hızlı video ile basit yapıların modal tanımlaması. Journal of Sound and Vibration, 2015, 345: 58-71.

Liu Ke. ZYNQ'ya dayalı yüksek hızlı görüntü toplama ve işleme platformunun tasarımı ve doğrulaması. Jinan: Shandong Üniversitesi, 2016.

Wang Ying, Gao Meifeng. Video görüntüsü hedef tespit sistemi FPGA tabanlı Bilgisayar Sistemi Uygulaması, 2017, 26 (6): 98-102.

Liu Ming. Kızılötesi görüntü tanıma ve FPGA tabanlı izleme sistemi Chengdu: Çin Elektronik Bilim ve Teknoloji Üniversitesi, 2016.

Su Feng, Ling Qing, Gao Meiguo Kızılötesi küçük hedef gerçek zamanlı algılama sisteminin gerçekleştirilmesi Lazer ve Kızılötesi, 2008, 38 (8): 826-829.

Yu Shuai. CMOS görüntü sensörüne dayalı yüksek hızlı kamera görüntüleme devresinin tasarımı ve araştırması. Pekin: Çin Bilimler Akademisi Üniversitesi, 2014.

yazar bilgileri:

Yang Luxin 1, 2, Dong Wenbo 1

(1. Uzay Uygulama Mühendisliği ve Teknoloji Merkezi, Çin Bilimler Akademisi Uzay Uygulamaları Anahtar Laboratuvarı, Çin Bilimler Akademisi, Pekin 100094;

2. Bilgisayar ve Kontrol Okulu, Çin Bilimler Akademisi Üniversitesi, Pekin 101408)

-

- Bugün, Wu Jing, Huang Bo, Shen Teng ve Han Han, Sırf bunun için, Kamu Güvenliği Bakanlığı'nın basın toplantısının kürsüsünde oturdu ...

-

- Kentsel ilişkiler Exp Expo'nun Zhejiang Pavyonu, Ningbo ekibi tarafından inşa edildi. En büyük vurgu: 9 metre uzunluğundaki koridorun dört mevsim çiçek sınırı var