FPGA tabanlı SRRC filtreleme ve çoklu oran dönüştürme

0 Önsöz

Uydu iletişim sisteminde, daha geniş bir frekans spektrumuna sahip olan temel bant sinyalinin, spektral özelliklerini iyileştirmek için sinyal iletilmeden önce şekillendirilmesi ve filtrelenmesi gerekir.Arabirim Sembol Girişimini (ISI) ortadan kaldırma ve en iyi algılama ve alımın elde edilmesi öncülüğünde, Kanalın frekans bandı kullanımını iyileştirin. İletişim sisteminde, verici uçtaki şekillendirme filtresi ve alıcı uçtaki eşleşen filtre, yükseltilmiş kosinüs filtrelemenin etkisini elde etmek için birlikte kullanılır ve sinyal filtrelenir. Kare Kök Yükseltilmiş Kosinüs (SRRC) daha hızlı zayıflama özelliklerine ve daha iyi gerçekleştirilebilirliğe sahip olduğundan, SRRC filtreleri genellikle iletişim sistemlerinin temel bant şekillendirme filtrelemesini uygulamak için kullanılır.

Çoklu oran dönüştürme genellikle iletişim sistemlerinde sinyal işlemede kullanılır, sinyalin örnekleme frekansı enterpolasyon (yukarı örnekleme) veya ondalık (aşağı örnekleme) ile değiştirilir ve sinyal filtrelenir. Uydu iletişiminin yüksek bant genişliğine sahip iletişim hizmeti ve AD dönüşüm oranının iyileştirilmesi, iletişim sisteminin iletim ucunda farklı sembol oranlarına sahip sinyallerin örnekleme oranının iyileştirilmesini teşvik etmiştir. İletişim sisteminin alıcı ucunda, çok yüksek örnekleme hızı ve veri çıkışı, gerçek zamanlı veri işlemeye elverişli değildir ve sinyal aşağı örnekleme işlemi gereklidir.

FPGA, paralel işleme ve esnek programlanabilir özellikleri ile temel bant sinyal işlemede yaygın olarak kullanılmaktadır. Bu makale, sinyalin örnekleme oranını artırmak ve herhangi bir katsayının sembol oranı dönüşümünü gerçekleştirmek için FPGA'ya dayalı çok oranlı bir dönüştürücü tasarlar (bu makale esas olarak yukarı örnekleme dönüşümünü uygular ve aşağı örnekleme gerçekleştirme yöntemi aynıdır). SRRC filtresi ve yarım bant (Yarım bant, HB) filtre, kademeli entegratör tarağı (Kademeli Entegratör Tarak, CIC) filtresi, örnekleme için Farrow filtre kademeli kullanın, karekök yükseltilmiş kosinüs filtresini gerçekleştirin ve keyfi çoklu sinyalleri uygulayın Frekans dönüştürme işlemi. Bunların arasında, farklı roll-off katsayıları için, SRRC filtrelerinin filtre katsayıları yeniden yüklenebilir; CIC ve Farrow filtrelerinin yukarı örnekleme katları çevrimiçi olarak yeniden yüklenebilir. Çoklu oran dönüştürme modülü, FPGA kaynaklarından etkin bir şekilde tasarruf sağlar, verimli ve uygulaması kolaydır ve herhangi bir çoklu için çoklu oran dönüşümünü gerçekleştirebilir.

1.1 SRRC filtreleme

1.1.1 SRRC'nin gerçekleştirme ilkesi

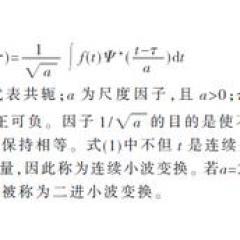

Kanal transfer fonksiyonunun genlik-frekans karakteristiği, yükseltilmiş kosinüs filtresinin karakteristiklerini a yuvarlama katsayısı ile karşıladığında, Şekil 1'de gösterildiği gibi, semboller arası girişim olmaksızın iletim gerçekleştirilebilir.

Şekil 1 (a), yükseltilmiş kosinüs filtresinin roll-off özelliklerini gösterir ve fN, Nyquist bant genişliğidir. Şekil 1 (b), yükseltilmiş kosinüs karakteristiğinin zaman alanı karakteristiğidir.Şekildeki ok en iyi örnekleme noktasına işaret etmektedir Semboller arası girişim olmaksızın maksimum iletim hızının 2fN olduğu görülebilmektedir.

Bunların arasında a, yükseltilmiş kosinüsün yuvarlanma özelliklerini belirleyen yuvarlama katsayısıdır. A = 1 olduğunda, rasyonel bir düşük geçiş özelliğine sahiptir, a ne kadar büyükse, yan kanat zayıflaması o kadar hızlı ve sinyal şekillendirme ve filtrelemeden sonra dalga biçimi hizalama zamanlamasının doğruluğu o kadar düşük olur.

İletişim sisteminin verici ve alıcı uçlarında SRRC filtrelerinin eşzamanlı kullanımı, artan kosinüs filtreleme etkisini sağlayabilir ve semboller arası paraziti ortadan kaldırabilir. SRRC filtresi, verici uçta şekillendirme filtresi olarak ve alıcı uçta eşleşen bir filtre olarak kullanılır. Şekillendirme filtresi, semboller arası girişimi etkili bir şekilde aşabilir, bit hata oranını azaltabilir ve tüm iletişim sisteminin performansını iyileştirebilir. Eşleştirilmiş filtreleme, en iyi alımı elde etmek için semboller arası girişimin neden olduğu sinyal bozulmasını düzeltebilir.

SRRC filtresinin transfer fonksiyonu denklem (2) 'de gösterilmektedir:

Formülde fN, Nyquist bant genişliğidir ve a, roll-off katsayısıdır.

1.1.2 SRRC roll-off faktörü ağır yük

Bu makalede, Xilinx IP çekirdeği, katsayı ile yeniden yüklenebilen SRRC filtrelemesini uygulamak için kullanılmıştır. Roll-off katsayıları 0.25 ve 0.35'tir ve çevrimiçi olarak yeniden yüklenebilir.

Katsayı yeniden yüklemesini uygulamak için IP çekirdeğini kullanırken, birkaç verctor kümesi bir grupta birleştirilebilir veya birkaç dizi filtre katsayısı bir katsayı dosyasına konabilir ve Fir IP çekirdeğinin filtre katsayıları IP çekirdeğindeki yapılandırma portu aracılığıyla yeniden yüklenebilir.

IP çekirdeğini oluştururken, katsayı setlerinin sayısını N olarak ayarlayın (N filtre katsayı seti olduğunu varsayarak). S_axis_config_tdata port değerini M (MN-1) olarak yapılandırarak, SRRC filtreleme için M + 1'inci katsayı setini seçebilirsiniz. , Mühendislik uygulamalarında filtre katsayılarının değiştirilmesini kolaylaştırmak.

Bu yazıda, MATLAB'ın Fdatool aracı, SRRC filtre katsayılarını oluşturmak için kullanılır ve yalnızca roll-off katsayısını a, sinyal iletim hızı, Nyquist oranı vb. Yapılandırması gerekir, işlem basit ve etkilidir.

Fdatool konfigürasyon sayfasında, sinyal iletim hızı, iletim bant genişliğinin B en az iki katına eşit olmalıdır, yani:

Formülde, FS sinyal iletim hızıdır ve FC Nyquist hızıdır.

1.2 CIC filtreleme

1.2.1 CIC filtrelemenin gerçekleştirme ilkesi

CIC filtresi, basit yapıya ve yüksek verime sahip sıfır kutuplu bir iptal filtresidir. Örnekleme frekansı değişikliği büyük olduğunda, kenar yumuşatmanın üstünlüğü nedeniyle CIC filtreleme etkisi daha iyidir.

CIC filtresinin birinci aşama durdurma bandı zayıflaması 13,36 dB ve M aşaması durdurma bandı zayıflaması 13,36M dB'dir. M'nin arttırılması, durdurma bandı zayıflamasını ve yan kanat baskılamasını artırabilir, ancak geçiş bandı içeriğinin sınırlandırılması nedeniyle, M genellikle 5'ten büyük değildir. Yukarı örnekleme faktörü D, CIC filtresinin ana lobunun genişliğini ve gerçek uygulamalardaki gereksinimlere göre ayarlanması gereken CIC filtrelemeden sonra örnekleme sıklığını belirler.

CIC filtresinin uygulanması basittir ve filtre katsayıları gerektirmez. CIC filtre IP çekirdeğini yapılandırırken, filtre sistemi saati giriş veri saatinin 3 katı olmalıdır.

1.2.2 CIC filtresi çoklu oran dönüşümü çevrimiçi yeniden yüklemeyi katlar

Bu makalede, CIC filtresi CIC IP çekirdeği kullanılarak uygulanmaktadır. Uygulama sürecinde, CIC filtre IP çekirdeğinin konfigürasyonu, aradeğerleme katları için programlanabilir, bu da kodun yeniden kullanılabilirliğini artırabilir ve FPGA'nın kaynak kullanımını etkili bir şekilde geliştirebilir.

Spesifik uygulama yöntemi: Örnekleme hızı dönüşümünü programlanabilir olarak yapılandırın ve örnekleme hızı dönüştürme aralığı Minimum Hız, Maksimum Hız'dır. S_axis_config_tvalid'nin yükselen kenarının geçerli olduğu varsayımı altında, S_axis_config_tdata'yı N olarak değiştirerek, CIC filtresinin N kez yukarı örneklemesi gerçekleştirilebilir, böylece CIC filtresinin üst örnekleme çarpanının çevrimiçi yeniden yüklenmesi gerçekleştirilebilir.

1.3 HB filtresi

HB filtresi, 2N dekimasyon veya enterpolasyon elde etmek için kullanılabilen ve düşük hesaplama karmaşıklığı ve güçlü gerçek zamanlı performans özelliklerine sahip, eşit simetrik, tek doğrusal fazlı yüksek verimli dijital filtredir. HB filtresi CIC filtresinde kademeli hale getirildikten sonra HB, CIC filtresinin ana lob kazancını düzeltebilir ve daha büyük örtüşme enerjisi içeren frekans bölgesini bastırabilir.

HB'nin darbe tepkisi h (k) gerçek bir sayıdır. HB filtresinin katsayısı formül (4) 'de gösterildiği gibi simetri özelliklerine sahiptir, çift katsayı sıfırdır, hesaplama miktarı yarıya indirilebilir ve yüksek bir uygulama verimliliğine sahiptir.

Bunların arasında: N, tek sayı olan filtre sırasıdır.

HB filtresi, FIR IP çekirdeği tarafından uygulanan özel bir FIR filtresidir. Filtre katsayıları, FDATOOL aracı tarafından oluşturulur, bir katsayı dosyası olarak kaydedilir ve IP çekirdeğine yüklenir.

1.4 Farrow filtresi

Farrow filtresi, ondalık katların oran dönüşümünü gerçekleştirebilir. Farrow filtresi, 3. interpolasyon filtresinin Farrow yapısını benimser ve frekans dönüştürme oranı, dijital gecikme modüle edilerek değiştirilebilir. Farrow yapısının filtresi enterpolasyon için kullanıldığında, aynalanma özelliğine sahiptir.

1.4.1 Farrow filtresinin gerçekleştirme ilkesi

Bu yazıda, üçüncü dereceden bir interpolasyon Farrow filtresi Verilog programlamasıyla gerçekleştirilebilir. Farrow filtresinin giriş ve çıkış veri frekansına göre, frekans dönüştürme oranı, dijital gecikme uk modüle edilerek değiştirilir.

Giriş sinyalinin periyodunun Ts ve çıkış sinyalinin periyodunun Ti olduğunu varsayalım. sonra:

Kübik interpolasyon polinomunun Farrow filtre yapısı Şekil 2'de gösterilmektedir.

1.4.2 Farrow filtresi, çevrimiçi yeniden yüklemenin katlarını örnekleme

Farrow filtresinin gerçekleştirme prensibi, giriş sinyali periyodu Ts olduğunda, modüle edilmiş dijital gecikme uk gerçekleştirilebileceğini ve çıkış sinyali periyodunun Ts'ye ayarlanabileceğini ve son olarak sinyal örnekleme oranı dönüşümünün gerçekleştirildiğini gösterir. Yani, çoklu örnekleme Farrow filtresinin çevrimiçi yeniden yüklenmesini gerçekleştirmek için. Mühendislik gerçekleştirme sürecinde, İngiltere'yi güçlendirerek doğruluk artırılır.

2 SRRC filtreleme ve çoklu oran dönüştürme uygulaması

Bu makaledeki çoklu oran dönüştürme modülünde, 3 SRRC filtresi isteğe bağlıdır, 3 kademeli 2 kez enterpolasyon HB filtresi, 9 enterpolasyon katlı 1 CIC filtresi ve 13 sıralı enterpolasyon Farrow filtre kaskad uygulaması. Çoklu oran dönüştürme modülünün kademeli yapısı Şekil 3'te gösterilmektedir. Giriş sinyalinin herhangi bir katsayısının yukarı örnekleme dönüşümü Verilog programlamasıyla elde edilebilir.

Çoklu oran dönüşümünün katı, fir_array parametresi tarafından kontrol edilir.

fir_array = 1, Farrow filtresinin kullanılması anlamına gelir; fir_array = 0, Farrow filtresinin kullanılmaması anlamına gelir. Farrow filtresinin interpolasyon çarpanı uk tarafından kontrol edilir.

fir_array, CIC filtre enterpolasyon katsayısını temsil eder. CIC enterpolasyon katları, herhangi bir sembol oranı dönüşümünün ihtiyaçlarını karşılamak için SRRC, HB ve Farrow ile kademelendirilebilen 4, 5, 6, 7, 8, 9, 10, 14, 21 seviyelerine sahiptir. fir_array = 0, CIC filtresinin kullanılmadığı anlamına gelir.

fir_array, ardışık 2 kez enterpolasyonlu HB filtrelerinin sayısını kontrol eder (toplam 3 basamaklı HB filtresi isteğe bağlıdır).

fir_array, SRRC filtresi tarafından kullanılan enterpolasyon çarpanlarını kontrol eder, fir_array sırasıyla 4 kez, 3 kez ve 2 kez enterpolasyonu temsil eder.

Giriş sinyali 2 MHz olduğunda ve 168 MHz'e yukarı örneklenmesi gerektiğinde, fir_array aracılığıyla {1b1, 10b0001000000, 3b001, 3b100} olarak ayarlanır ve 4 kez enterpolasyonlu SRRC filtresi kullanılır ve 2 kez HB Enterpolasyon filtreleme, 10 kez CIC enterpolasyon filtreleme, 160 MHz'den 168 MHz'e kadar birinci seviye Farrow enterpolasyon filtreleme.

ISE platformunda, örnekleme IP çekirdeği fir_compiler 6.3 ve MATLAB'ın FDATOOL aracı, katsayılı yeniden yüklenebilir SRRC filtresi ve HB filtresinin tasarımını birlikte gerçekleştirdi ve CIC'yi yeniden yüklenebilir enterpolasyon katları ile gerçekleştirmek için AXI veriyoluna dayalı cic_compiler 3.0 IP çekirdeği kullanıldı. Farrow filtresi, üçüncü dereceden interpolasyon yapısına dayalı olarak Verilog dil programlaması tarafından uygulanır.

Bunların arasında, SRRC filtresi ve HB filtre katsayıları FDATOOL araçları, 48-seviye, Hamming penceresi tarafından üretilir. HB filtresinin örnekleme hızı 100 MHz'dir ve kesme frekansı 25 MHz'dir. SRRC filtresinin örnekleme hızı 100 MHz'dir ve kesme frekansı 25 MHz'dir.

Simülasyon saatini 168 MHz'e ve giriş sinyali hızını 2 MHz'e ayarlayın. Veri kaynağı 10 rastgele sayı X (-1, -1, 1, 1, 1, -1, 1, 1, 1, 1, -1) 8 kez enterpolasyondur ve enterpolasyon değeri 0'dır. Simülasyon doğrulaması için ModelSim simülasyon aracı aracılığıyla simülasyon sonuçları Şekil 4'te gösterilmektedir.

Şekil 4 (a) 'dan görülebilir: SRRC filtrelemesinden ve hızı değiştirdikten sonra, simüle edilmiş dalga formu, temelde giriş sinyali ile aynı olan ve iyi bir düzgünlüğe sahip olan yükseltilmiş bir kosinüs dalga formudur. Sistem saati açıklığı 168 MHz'dir ve Şekil 4 (b) 'den görülebilir: SRRC giriş sinyalini filtreledikten ve çok oranlı dönüştürme gerçekleştirdikten sonra, sinyal hızı 168 MHz'e yükseltilir.

3 Deneysel doğrulama

Deney panosunda SRRC filtreleme ve çoklu hız dönüştürme modülü (168 MHz'e yükseltme), DA dönüştürme modülü ve 20 MHz sembol hızına sahip 16APSK modülasyonlu sinyalin RF çıkışından sonra, takımyıldız diyagramını ve RF çıkış sinyalinin spektrum analizörü ile sinyalini gözlemleyin. Şekil 5'te gösterildiği gibi kalite ve bant genişliği.

Spektrum analizörünün test sonuçları, 16APSK ile modüle edilmiş sinyalin SRRC filtreleme ve çoklu oran dönüştürme ile işlenmesinden sonra çıkış sinyalinin bant genişliğinin etkili bir şekilde 20 MHz ile sınırlandığını ve 16APSK takımyıldız diyagramının normal olarak çözülebildiğini göstermektedir.EVM sinyalinin yaklaşık% 3'ü, bu da kodu etkin bir şekilde ortadan kaldırır. Girişim. Bunlar arasında, EVM ne kadar küçükse (% 0-% 100), çıktı modülasyon sinyalinin kalitesi o kadar iyidir.

4. Sonuç

Bu makale, SRRC filtrelemeyi ve FPGA'ya dayalı çoklu oran dönüştürme modüllerini uygulamak için ayrıntılı bir yöntem sunar. Modül, SRRC, HB, CIC ve Farrow filtrelerinin basamaklandırılmasıyla ve SRRC filtre katsayılarının, CIC ve Farrow filtre enterpolasyon katsayılarının çevrimiçi yeniden yüklenmesi ile gerçekleştirilir, farklı roll-off katsayıları ile yükseltilmiş kosinüs filtreleme ve çoklu oran dönüşümü elde edebilir, etkili bir şekilde tasarruf sağlayabilir FPGA kaynakları. Modülün SRRC filtreleme ve çoklu oran dönüştürme özellikleri simülasyon analizi ve deneylerle doğrulanır. Modülün mühendislikte uygulanması kolaydır, semboller arası paraziti etkili bir şekilde ortadan kaldırabilir, frekans bandı kullanımını iyileştirebilir ve modern iletişim ve dijital sistem işlemede gerçek zamanlı gereksinimleri daha iyi karşılayabilir.

Referanslar

SREEVIDYA N, SATEESHKUMAR H C.SRRC filtre uygulaması DVB-S2 standardına göre International Journal of Innovative Research and Development, 2013, 2 (5): 1148-1161.

Feng Jiamei, Zou Gang, Zhu Nan ve diğerleri Değişken bant genişliğine dayalı çok oranlı işleme algoritmasının tasarımı ve uygulaması. Digital Communication World, 2015 (8): 21-25.

Fan Changxin, Cao Lina. İletişim İlkeleri. Pekin: Ulusal Savunma Sanayii Basını, 2012.

VANUKURU H R, YOGESH P K R, RAVICHANDRAN V, et al. CCSDS ACM'de kök yükseltilmiş kosinüs filtrelemenin performans analizi. Uluslararası Kablosuz İletişim, Sinyal İşleme ve Ağ Konferansı, 2016.

Xinlinx Inc. LogiCORE IP FIR Derleyici V6.3 DS795, 2011.

Cic filtresinin FPGA uygulaması.2016-06-04> .http: //blog.sina.com.cn/s/blog_4b1046f80102wjrh.html.

Xinlinx Inc. LogiCORE IP CIC Derleyici V3.0 DS845.2011.

Cao Jianfei, Wen Shuangchun, Liu Yu, ve diğerleri.Çok oranlı yazılım radyo dijital orta frekans sisteminin araştırılması ve uygulanması.Bilgisayar Mühendisliği ve Bilimi, 2017, 39 (6): 1079-1086.

Lou Yang, Wang Zhongxun, Xinxing Long, vb. Dijital aşağı dönüşüm DDC'nin tasarımı ve FPGA uygulaması Çin Entegre Devreleri, 2017, 26 (Z1): 52-56.

Chen Qin. QAM sinyalinin bit senkronizasyonu ve kör eşitlemesi gerçekleştirme teknolojisi üzerine araştırma Chengdu: Çin Elektronik Bilimi ve Teknolojisi Üniversitesi, 2014.

yazar bilgileri:

Yang Yang1, Yan Zheng2, Liu Minwei2, Dong Jicheng2

(1. Entegre Devre Tasarım Merkezi, Havacılık Sichuan Şubesi Tianhui Technology Co., Ltd., Chengdu 610100, Sichuan;

2. Aerospace Star Technology Co., Ltd. Tümleşik Devre Tasarım Merkezi, Pekin 100086)

-

- Tencent ikinci çeyrek VR raporunu yayınladı: yetişkinlere yönelik web sitesinin Pornhub VR alanındaki videoların sayısı hızla artıyor

-

- Olimpik tema versiyonu "Fuxing" ilk kez! Saatte 350 kilometrede otonom sürüş ilk kez gerçekleştirildi