Testbench tabanlı FPGA fiziksel otomasyon test ortamının tasarımı

Özet: FPGA yazılım test sürecindeki simülasyon testi ve fiziksel testin eksikliklerini hedef alarak, simülasyon test durumlarına dayalı fiziksel otomatik bir test ortamı önerilmiştir.Simülasyon testi için kullanılan Testbench analiz edilir ve FPGA fiziksel testi için kullanılabilecek bir iletim sinyali oluşturmak için işlenir. Bu sinyal, aktüatör tarafından test edilen FPGA yongasına etki eden gerçek sinyale dönüştürülür ve test edilen FPGA yongasının yanıtı toplanarak FPGA'nın otomatik testini gerçekleştirir. Tasarım mimarisi, fiziksel otomatik test ortamı doğrulama platformu kullanılarak doğrulandı ve iyi sonuçlar elde edildi.

TP311.11

Bir

10.16157 / j.issn.0258-7998.173548

Çince alıntı biçimi: Gao Hu, Feng Erqiang, Zhao Gang.Testbench'e dayalı FPGA fiziksel otomatik test ortamının tasarımı.Elektronik Teknoloji Uygulaması, 2018, 44 (4): 48-51.

İngilizce alıntı biçimi: Gao Hu, Feng Erqiang, Zhao Gang.Testbench'e dayalı FPGA fiziksel otomatik test ortamının tasarımı.Elektronik Tekniğin Uygulanması, 2018, 44 (4): 48-51.

0 Önsöz

FPGA tasarım ölçeğinin sürekli genişlemesi ile FPGA yazılım tasarımının neden olduğu kalite sorunları giderek daha belirgin hale geldi ve ekipman kalitesini etkileyen önemli bir faktör haline geldi. Test şu anda bu sorunu çözmenin en etkili yoludur.Bu nedenle, sonlandırma sürecinde FPGA yazılım testi için giderek daha fazla sayıda ekipman ürünü modeli yeni gereksinimler ortaya koymaktadır.

Bununla birlikte, FPGA testi geleneksel yazılım testlerinden farklıdır. Test ortamının sınırlamaları nedeniyle, test süreci büyük ölçüde simülasyon ve analiz yöntemlerine dayanmalıdır. Gerçek yongalarda gerçekleştirilen testler genellikle kart düzeyinde ve sistem düzeyinde testlerdir ve test sonuçları düşük güvenilirliğe sahiptir. Ve FPGA yazılım tasarım hatalarını etkin bir şekilde bulmak imkansızdır. Bu amaçla, bu makale simülasyon test platformu Testbench verilerine dayanan otomatik bir test ortamı çerçevesi önermektedir.Test sonuçları yüksek güvenilirliğe sahiptir ve FPGA testinin kalitesini etkili bir şekilde artırabilir.

1 FPGA dinamik testine genel bakış

1.1 FPGA dinamik test ortamı prensibi

Mevcut model ekipman FPGA sonlandırma test sürecinin ana yöntemleri tasarım kontrolü, fonksiyonel simülasyon, kapı seviyesinde simülasyon, zamanlama simülasyonu, statik zamanlama analizi, mantık eşdeğerlik kontrolü ve fiziksel testi içerir. Bunlar arasında fonksiyonel simülasyon, kapı seviyesinde simülasyon, zamanlama simülasyonu ve fiziksel testler dinamik testlerdir.Test yapılırken FPGA işlemi için çevresel ortamın test gereksinimlerine göre kurulması gerekir.Farklı test nesnelerine göre bu tür ortam simülasyon test ortamına ve Fiziksel test ortamı.

Bir simülasyon test ortamı kullanılırken, bir simülasyon test platformu dosyası Testbench oluşturmak için test verilerinin test senaryolarına göre farklı anlarda farklı sinyal değerleriyle eşlenmesi gerekir.Test edilen FPGA tarafından oluşturulan yanıt toplanır ve bir test sonucu oluşturmak için simülasyon test aracı tarafından otomatik olarak değerlendirilir .

Fiziksel bir test ortamı kullanıldığında, genellikle bir sistem test ortamı oluşturulur.FPGA, çevresel devreler ve ekipmanla çalıştırılır ve uyarma verileri, harici veri yolu arabirimi aracılığıyla ayarlanır ve ardından yanıt sonuçları, veri yolu çıkış arabirimi aracılığıyla görüntülenir ve test sonuçları, manuel analiz ve değerlendirme ile oluşturulur.

1.2 FPGA dinamik test özellikleri

Test edilen sistem, test uygulama sürecinde çalışır durumda olduğundan, dinamik test, aslında çalışırken sistemin davranışını daha doğru bir şekilde yansıtabilir, bu nedenle test teknolojisindeki en önemli test yöntemlerinden biri haline gelmiştir. FPGA dinamik test süreci genellikle simülasyon testi ile fiziksel testi birleştirme yöntemini benimser.Test senaryolarını yürüterek FPGA gereksinimlerini kapsar ve ilgili hataları bulur.Statik test ile karşılaştırıldığında sezgisel test sonuçları ve yüksek kapsama avantajlarına sahiptir.

Bununla birlikte, FPGA dinamik testinin, mevcut model test görevlerinde gittikçe daha belirgin hale gelen bazı dezavantajları da vardır, bunlar arasında şunlar yer alır: (1) Simülasyon testi, simülasyon aracının performansına çok bağlıdır; (2) Simülasyon testi kapsamı, IP çekirdeklerinin kullanımı ve diğer nedenlerden dolayı mevcut değildir. Tam garantili; (3) Fiziksel test, sistem verileri içindir, ancak çip sinyalleri için değildir.

Yüksek güvenilirlikli sistemler için mevcut FPGA dinamik test yöntemi, model görev testinde önemli bir test yöntemidir.Mühendislik uygulamasında çok sayıda FPGA kalite hatası bulunabilmesine rağmen, yukarıda belirtilen dezavantajlar çözülemez ve FPGA'nın potansiyel kalite riskleri etkili bir şekilde kontrol edilemez.

2 Otomatik test ortamı tasarımı

2.1 Çevresel talep analizi

Mevcut yüksek güvenilirlik sistemi FPGA dinamik testinin güvenilirliğini ve test verimliliğini artırmak için dinamik test süreci aşağıdaki test gereksinimlerini karşılamalıdır:

(1) Test uyaranı, FPGA çipinin girdi ve çıktı davranışını tam olarak yansıtabilmelidir, sistem düzeyinde olmayan test uyaranı ise yalnızca uygulama verilerini yansıtır, yani test senaryosu verilerinin uygulama katmanından sinyal iletim katmanına indirgenmesi gerekir.

(2) Dinamik test için hedef FPGA tasarımının, hedef FPGA'yı değiştirmek için simülasyon araçları kullanmak yerine gerçek bir cihazda çalıştırılması gerekir.

(3) Dinamik test uyarısının uygulanması ve test sonuçlarının toplanması, FPGA tasarım gereksinimlerinin doğruluğunu ve gerçek zamanlı performansını karşılayabilir, yani test edilen FPGA tasarımına yüksek hassasiyetli sinyal girişi uygulayabilir ve aynı zamanda test edilen FPGA'nın yüksek hassasiyetli çıkış sinyalini destekleyebilir. Doğruluk edinimi; ek olarak, FPGA'nın her bir uyarma ve yanıt sinyalinin gerçek zamanlı performansı, sistem gereksinimlerini karşılamalıdır.

2.2 Çevresel çerçeve yapımı

2.2.1 Çalışma prensibi

Dinamik test ortamının gereksinimlerini karşılamak için Testbench'e dayalı fiziksel bir test ortamı tasarlanmıştır.Testbench tarafından test sinyal kapsamı ve tetikleme süresinin tanımlanması ile test uyarımının sinyal iletim katmanı gereksinimleri çözülür.Test tezgah sinyali gerçek bir devre sinyaline dönüştürülerek ona uygulanır. Test edilen gerçek FPGA yongası, test edilen sistemin özgünlüğü sorununu çözer; Testbench sinyal açıklamasının ve gerçek devre sinyalinin yüksek performanslı FPGA yongası aracılığıyla dönüştürülmesi, test uyarımı ve yanıtının doğruluğunu ve gerçek zamanlı gereksinimlerini çözer. Spesifik çalışma prensibi aşağıdaki gibidir: Test uyaran verileri, Testbench'in anlamsal analizi ile elde edilebilir. Bu uyaran verileri simülasyon için kullanılmazsa, ancak sinyal dağıtımı yoluyla test edilen FPGA çip varlığına uygulanırsa, Testbench'e dayalı fiziksel test gerçekleştirilebilir. Aynı zamanda, Testbench'te beklenen sinyalin okuma sürecini analiz edin ve test edilen FPGA'nın çalışma sonucunu elde etmek için test edilen FPGA varlığının çıkış sinyalini okuyun ve ardından gerçek çalışma sonucunu beklenen sonuçla otomatik olarak karşılaştırın. Testbench'e dayalı otomatik test sürecini gerçekleştirin.

2.2.2 Sistem yapısı

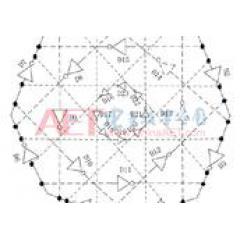

Testbench altında FPGA otomatik testinin çalışma prensibine göre FPGA otomatik test ortamı çerçevesinin tasarımı Şekil 1'de gösterilmektedir.

Test ortamı iki bölüme ayrılmıştır: testin gerçek zamanlı gereksinimlerine göre ana kontrol platformu ve yürütme platformu Ana kontrol platformu gerçek zamanlı olmayan bir düğümdür ve yürütme platformu gerçek zamanlı bir düğümdür.

Ana kontrol platformu esas olarak test hazırlığını ve test sonucu analizini tamamlar. Hazırlık çalışması, test uyaranının hazırlanmasını ve test arayüzünün hazırlanmasını içerir. Test uyaranının hazırlanması, Testbench'teki test uyaran bilgisinin analiz edilmesi sürecini ifade eder Spesifik süreç şudur: Ana kontrol platformunda testbench'i düzenledikten sonra, oluşturulan Testbench resmileştirilir ve iki uyarıcı etki alanına ve sonuç alanına ayrıştırılır. Sınıf alanı, her alan alanı üç öğe içerir: zaman, pin ve pin değeri ve son olarak test uyarma bilgilerini içeren bir veri çerçevesi mesajı oluşturur ve veri çerçevesi mesajını Ethernet üzerinden yürütme platformuna gönderir. Test arayüzünün hazırlanması, test edilen FPGA çevresel arayüz modelinin tasarlanması ve sentez, yerleştirme ve yönlendirmeden sonra yüksek performanslı bir FPGA'ya (bundan sonra aktüatör FPGA olarak anılacaktır) indirilmesi sürecini ifade eder; farklı test edilmiş FPGA test projeleri için Sırasıyla aktüatör FPGA'nın arayüz modelini oluşturmak gerekir. Test sonuç analizi çalışması, test sonuç verilerini almak ve test raporları oluşturmak için kullanılır.

Yürütme platformu, çok kanallı bir sinyal alıcı-verici platformu olarak kabul edilebilir.Ana kontrol tarafından verilen Testbench uyarma veri çerçeve mesajını alır ve bunu büyük kapasiteli DPRAM'de saklar.Test yürütme komutu alındığında, veri çerçevesi mesajı DPRAM'a gönderilir. Aktüatör FPGA. Aktüatör FPGA, sinyali test edilen FPGA'ya DPRAM'de açıklanan sinyal pini, sinyal değeri ve sinyal tetikleme süresi bilgilerine göre verir ve test edilen FPGA tarafından üretilen çıkış sinyalini edinme pimi adresine ve edinme zamanlamasına göre okur ve ardından toplar. Test edilen FPGA'nın yanıt sonucu işlemciye DPRAM aracılığıyla gönderilir ve izleme ve test sonucu analizi için gerçek zamanlı olarak ana kontrol platformuna rapor edilir.

2.3 Anahtar teknoloji

Testbench tabanlı otomatik fiziksel test ortamı, Testbench'i veri çekirdeği olarak alır ve aktüatör FPGA aracılığıyla veriden sinyale dönüşüm gerçekleştirir.Bu nedenle, testbench analiz yöntemi ve aktüatör FPGA tasarımı, fiziksel otomatik test ortamını oluşturmak için anahtar teknolojilerdir.

2.3.1 Testbench analiz yöntemi

Testbench, FPGA testi için veri sürücüsü ve FPGA test sonucu toplama sürücüsüdür. Testbench üç bölümden oluşur: uyarma üretimi, uyarma uygulaması ve yanıt kararı. Testbench'e dayalı otomatik bir fiziksel test ortamının inşasında, Testbench'in analizi esas olarak uyaran üretiminin ve yanıt kararının analizini ifade eder; uyarıcı uygulamasının özü, test altındaki FPGA'yı (yani, DUT, Test Altında Tasarım) başlatmaktır. Test ortamının hiçbir etkisi yoktur.

Testbench'i oluşturmak için kullanılan dilden bağımsız olarak, uyarıcı üretimi, belirli bir zamanda DUT pinlerine belirli değerler uygulayan bir dizi işlem olarak uygulanacaktır. Bu nedenle, Testbench'in uyarıcı uygulama süreci, bir zaman, pin ve pin değerleri koleksiyonu olarak ayrıştırılabilir ve adlandırılabilir Bu set teşvik alanıdır.

Testbench'teki yanıt değerlendirme süreci, bir dizi uyarıcı oluşturulduktan ve DUT'a uygulandıktan sonra uygulanır. Uyarıcı etki alanına benzer şekilde, bu süreç, belirli bir zamanda DUT pimi üzerindeki işlemlerin bir koleksiyonu olarak da anlaşılabilir. Süreç ayrıca zaman olarak ayrıştırılır , Pin, pin değeri 3 öğe ve kümeyi sonuç alanı olarak adlandırın. Uyarı alanından farklı olarak, sonuç alanındaki pin değeri beklenen sonuç verilerini saklamak için kullanılır.Pin değeri boş olarak da ayarlanabilir, yani beklenen bir sonuç yoktur, bu da test sonucunun manuel olarak belirlendiği anlamına gelir.

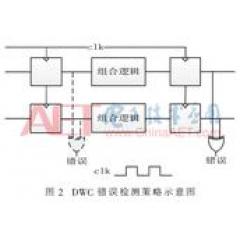

Özetle, bir Testbench, Şekil 2'de gösterildiği gibi uyarma alanlarının ve sonuç alanlarının bir koleksiyonu olarak ayrıştırılabilir.

Test ortamının zaman kontrol doğruluğunu iyileştirmek ve depolama verimliliğini iyileştirmek için, bir zaman noktasındaki uyarma alanı ve sonuç alanı, aşağıdaki gibi tanımlanan zaman kontrol noktası yapılandırma yapısı Tickset'e ayrıştırılır:

Bunlar arasında tickVal, uyarma sinyalinin tetiklendiği anı temsil eder, drvPinNum aynı anda kaç pinin atandığını saklamak için kullanılır, drvTab belirli pim yapılandırma tablosuna bir göstericidir, pim yapılandırma tablosunun yapısı aşağıdaki gibidir:

Bu şekilde, zamandaki bir nokta, drvPinNum uyarma pimleri ve sampPinNum edinme pimlerini içeren bir Tickset yapısıdır ve her pinin adresi ve değeri de dahil edilir.

Bir Testbench, birlikte bir test senaryosu oluşturan birden fazla zaman noktası içerir. Bu nedenle, bir test senaryosu, aşağıdaki biçimde bir vaka yapısı olarak tanımlanabilir:

Vaka yapısı tickNum Ticksets'i içerir ve işaretçi değişkeni tickPoints, belirli bir zaman kontrol noktası yapılandırması Tickset setini temsil eder.

Otomatik fiziksel test ortamının tasarım hedeflerinden biri, test yürütme verimliliğini artırmaktır.Bu nedenle, üretilen tüm test tezgahları, test senaryosu setindeki kullanım senaryolarının kesintisiz yürütülmesini sağlamak için bir test senaryosu seti oluşturmak için tek seferde analiz edilebilir. Caseet'in tanımı aşağıdaki gibidir:

Testbench ayrıştırma yazılımını tasarlayın, tüm Testbench dosyalarını yukarıda belirtilen mutabık kalınan protokole göre biçimlendirin ve ayrıştırın Nihai test senaryosu seti Caseet yürütme platformuna gönderilir ve aktüatör FPGA'nın okuması ve yapılandırması için CPU üzerinden DPRAM'a yazılır.

2.3.2 Aktüatör FPGA tasarımı

Aktüatör FPGA, test edilen FPGA ile test ortamını birbirine bağlayan bir arayüz uyarlama birimidir.Genellikle Testbench verilerinin ve devre sinyallerinin dönüştürme işlevini tamamlar ve tüm otomatikleştirilmiş test ortamında temel bir rol oynar. Dahili ana modülleri ve bilgi aktarım ilişkileri Şekil 3'te gösterilmektedir.

Aktüatör FPGA, DPRAM'daki Testbench uyarma veri mesajını okur, uyarma alanını ve sonuç alanını ayrıştırır ve iki alanın zaman kontrol değerlerini işlem için sayaca aktarır.

Uyaran alan analiz modülü, DPRAM'deki uyarıcı verilerine uygulanacak FPGA pin adresini ve uyarıcı değerini okur ve ardından adres veri dağıtım modülü üzerinden FPGA pin indeksi ve veri mandalını gerçekleştirir ve uyarma tetikleme süresine ulaşıldıktan sonra uyarıcı verilerini belirlenen pinden geçirir. Test edilen FPGA'ya çıktı.

Sonuç etki alanı analiz modülü, DPRAM'de sonuç toplama için gereken pin adresini ve beklenen sonuç değerini okur ve adres veri dağıtım modülü aracılığıyla pin eşlemesi gerçekleştirir Toplama zamanı geldiğinde, adres veri dağıtım modülü, toplama tamponundan karşılık gelen verileri okur. Veri değeri, DPRAM'de beklenen toplama sonucu değeri ile karşılaştırılır ve bu anda sonuç, asıl test sonucu ile birlikte ana kontrol platformuna yüklenmesi için DPRAM'a gönderilir.

Zaman kontrol modülü, aktüatör FPGA'nın kontrol merkezidir.Bir yandan, DPRAM'deki zaman açıklamasını okur, aktüatör FPGA'nın giriş ve çıkışı tetiklemesi gereken zamanı hesaplar ve FPGA sinyalini gerçekleştirmek için sayaç aracılığıyla uyarma ve edinme etkinleştirmesini kontrol eder. Gerçek zamanlı iletim kontrolü; Öte yandan DPRAM'daki test senaryolarının sayısı, test uyarma alanlarının sayısı, sonuç alanlarının sayısı ve her bir alandaki farklı zaman noktalarında pin sinyallerinin sayısı okunarak, test durumlarında farklı test anlarının yönetimi Uyarma alanının zaman ve pim konfigürasyonu ve sonuç alan verileri, pim ve veri tahsisini gerçekleştirmek için uyarma alanı analiz modülü ve sonuç alan analizi modülü için bir temel sağlar.

Ek olarak, aktüatör FPGA ayrıca bir giriş pimi grubu, bir çıkış pimi grubu ve veri yönetimi için adres alma ve dağıtım modülü ile işbirliği yapmak için kullanılan ana kontrol platformunun test edilen FPGA arayüz modelleme yazılımı tarafından yapılandırılan bir giriş pimi grubu içerir.

2.4 Yazılım ve donanım dağıtımı

Otomatik dinamik test ortamı iki bölümden oluşur: üst bilgisayar ana kontrol platformu ve alt bilgisayar yürütme platformu Ana kontrol platformu özel donanım tasarımı olmadan PC üzerinde çalışır; yürütme platformu esas olarak 3 bölümden oluşur: X86CPU, DPRAM ve aktüatör FPGA. Bunların arasında X86CPU, DPRAM ile iletişim kurar. Aktüatör FPGA tarafından veri iletişiminin tasarımı, geleneksel DPRAM iletişim yöntemini benimser.

Yazılım açısından, ana bilgisayar ana kontrol platformu, Testbench'i Caseset test senaryo seti formatına ayrıştırmak için Testbench analiz yazılımını kullanır; test edilen FPGA arayüz modelleme yazılımını devreye alır ve aktüatör FPGA ile test edilen FPGA'nın uygulanmasını aktüatör FPGA entegre geliştirme ortamı ISE ile birlikte gerçekleştirir. Bağlantı pinlerinin konfigürasyonu; test yürütme sonucu verilerini yumuşak bir şekilde almak ve görüntülemek için izleme ve raporlama yoluyla test raporları oluşturarak; alt düzey bilgisayar yürütme platformu X86CPU, test komutlarını ve test veri dağıtımını ve gerçek zamanlı dönüşü yürütmek için gerçek zamanlı işletim sistemi VxWorks 5.5'i çalıştırır.

3 Deneyler ve uygulamalar

Yukarıdaki tasarım yöntemlerine dayanarak, Testbench ayrıştırıcı yazılımı, FPGA arabirim modelleme yazılımı gibi çekirdek yazılımlar dahil olmak üzere FPGA simülasyon kullanım durumu fiziksel test ortamı prototipini geliştirin ve tasarlayın ve Testbench dosyasını Caseet toplama formatına ayrıştırın; verilerini tasarlamak için aktüatör FPGA olarak XC7VX690T'yi kullanın Ve sinyal dönüştürme mantığı ve harici bir kablolama kartı aracılığıyla test edilen FPGA yongasıyla çapraz bağlantı. Platform, belirli bir uydu navigasyon iletişimi FPGA yazılım testinde kullanıldı ve "simülasyon + sistem" test yöntemi ile karşılaştırıldığında, test verimliliği önemli ölçüde iyileştirildi.

4. Sonuç

Bu makale keşif amaçlı olarak, simülasyon testi ve mevcut fiziksel testin eksikliklerini telafi etmek için FPGA yazılım testinde kullanılan bir simülasyon test platformuna dayalı fiziksel otomatik bir test ortamı önermektedir. Tasarım çerçevesi, fiziksel otomatik test ortamının bir prototipiyle doğrulanır. Sonuçlar göstermektedir ki Test ortamı, yüksek test kapsamı ve yüksek test verimliliği gibi avantajlara sahiptir.Ardından sonraki projelerde optimize edilebilir ve FPGA test mühendisliği uygulaması için ana araç olarak kullanılabilir.

Referanslar

Gao Hu, Liu Yuan, Liu Ziyi.DO-254 standardında doğrulama ve doğrulama sürecinin analizi Havacılık Standardizasyonu ve Kalitesi, 2014 (2): 10-13.

Liu Ziyi, Liu Chang, Zheng Haziran.Yazılım test teknolojisine dayalı FPGA testi üzerine araştırma Elektronik Teknoloji Uygulaması, 2011, 37 (5): 28-30.

Zhou Shan, Yang Yawen, Wang Jinbo. Havacılıkta Yüksek Güvenilirlik FPGA Test Teknolojisi Araştırması. Bilgisayar Teknolojisi ve Geliştirme, 2017, 27 (3): 1-5.

Fei Yanan, Zhou Hui, Zhu Weijie.FPGA Yazılım Otomasyon Doğrulama Platformunun Tasarımı ve Uygulaması Bilgisayar Ölçümü ve Kontrolü, 2016, 24 (5): 139-142.

LEMON R, COULTER B, ARCHIBALD S, ve diğerleri Büyük ölçekli test sistemlerinde bir süreklilik / yalıtım otomatik test istasyonu kullanarak arabirim testi adaptörü geliştirme ve bakımı Autotestcon, 2009 IEEE, 2009: 107-112.

JUSTIN J, LINDSTROM L, JAIN A. ATE test yazılımı yeteneklerini basitleştirmek ve geliştirmek için bir eklenti modelinin kullanılması Autotestcon, 2012 IEEE, 2012: 105-107.

Wang Peng, Liu Wanhe, Liu Rui, vb. SystemVerilog'a dayalı yeniden kullanılabilir bir test platformunun uygulanması Elektronik Teknolojinin Uygulanması, 2015, 41 (2): 61-64.

Gao Hu, Zheng Jun, Zhao Gang. FPGA kart düzeyinde otomatik simülasyon test ortamının çerçeve tasarımı. Mikroelektronik ve Bilgisayar, 2017, 34 (12): 94-98.

Sun Xiurui. FPGA tasarım doğrulamasında yazılım ve donanım birlikte simülasyon test yöntemi. Journal of Nantong University (Natural Science Edition), 2016, 15 (3): 41-44, 66.

Wang Xiaogeng. Dijital SoC tasarımının ve VHDL'ye dayalı doğrulamanın tam otomatik gerçekleştirilmesi Xi'an: Xidian Üniversitesi, 2016.

Yi Min, Su Shujing, Ji Wei, vb FPGA'ya dayalı yüksek hızlı zaman alternatifli örnekleme sistemi Elektronik Teknoloji Uygulaması, 2015, 41 (1): 71-74.

Qian Yiwen, Jing Weiping, Jiang Bin. UVM'ye dayalı CPU kart çip doğrulama platformu. Mikroelektronik ve Bilgisayar, 2016, 33 (6): 37-40.

Wang Jianzhong, Yang Lu. Yüksek hızlı gerçek zamanlı sistem veri toplama ve iletimi Computer Science, 2016, 43 (S2): 604-606.

Lu Bo, Zhang Yong, Huang Kan, vb FPGA'ya dayalı dört portlu RAM tasarımı ve uygulaması Instrumentation Technology and Sensors, 2017 (1): 34-37.

yazar bilgileri:

Gao Hu, Feng Erqiang, Zhao Çetesi

(Çin Havacılık Teknolojisi Araştırma Enstitüsü, Pekin 100083)

-

- Siber şiddet ve akıl hastalığı nedeniyle, bağımsız bir oyun geliştiricisi geçen hafta kendini yakarak öldü

-

- Yürüyen at halk hikayeleri, Siçuan operası, nakış ... Somut olmayan kültürel miras, çocukların Çin kültürünü devam ettirmesine izin vermek için kampüse girer.

-

- Rekabet yoluyla araştırmayı teşvik etmek için Formula E'deki otomobil şirketlerinin ne gibi yeni yolları var?

-

- Küçük ve yeni filmler için hassas bir pazarlama yaklaşımı olan "Üzücüden Daha Sad Bir Hikaye" 700 milyonu kırdı