FPGA'ya Göre Ayarlanabilir Kanal Sayısı ile Yüksek Hassasiyetli Alım Sisteminin Modüler Tasarımı

Akustik kamera, mekansal video bilgisini ses alanı ölçüm bilgisiyle birleştiren ve görsel olarak görüntüleyen bir teknolojidir. Esas olarak üç bölümden oluşur: sensör dizisi, veri toplama sistemi ve veri işleme sistemi.Stratejik askeri endüstride, endüstriyel gürültü azaltma, tahribatsız testler ve diğer alanlarda yaygın olarak kullanılmaktadır. . Şu anda, Almanya'nın CAE'sinden Bionic 112 Array serisi akustik kamera 112 mikrofon dizisi elemanına, 24 bit çözünürlüğe ve 0,2 m'den daha büyük uzak alan ses kaynaklarının iki boyutlu görüntülemesini sağlayabilen 48 kHz örnekleme hızına sahiptir; Danimarka BK da geliştirdi PULSE Reflex serisi 30 elementli portatif akustik kameralar. Yurtiçinde, 32 kanallı optimize edilmiş kavisli diziye dayanan yüksek teknolojisi, 300 kHz ~ 12 kHz ses kaynaklarının konumlandırılmasını ve görüntülenmesini gerçekleştiren ve PXI veri yolu üzerinden veri iletimini tamamlayan yüksek performanslı KeyVES-U serisini piyasaya sürdü.

Akustik kameralar, edinim sisteminin kendi gürültüsüne karşı çok hassastır ve çok sayıda mikrofon tarafından alınan akustik sinyalleri eşzamanlı olarak almaları ve büyük bir bant genişliği altında veri iletimini gerçekleştirmeleri gerekir.Bu nedenle, yüksek performanslı bir akustik kamera, edinim sisteminin örnekleme doğruluğuna ve maliyetine çok duyarlıdır. Gürültü tabanı ve kanal sayısı gibi performans göstergeleri daha yüksek gereksinimleri ortaya koymaktadır. Bu yazıda, bu sorunu çözmek için, farklı akustik kameraların ihtiyaç duyduğu farklı kanal sayısı sorununu çözen, farklı mikrofon elemanlarından gelen sinyaller için veri toplama ihtiyaçlarını karşılayan ve modülün özelliklerini tartışan kontrol tabanlı bir veri toplama modülü tasarlanmıştır. Genel tasarım süreci ve genişletilebilirlik analiz edilir ve edinim modülünün performans göstergeleri gerçek testlerle verilir.

1 donanım tasarımı

1.1 Genel mimari tasarım

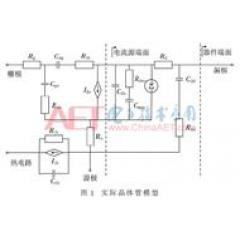

Yarı iletken teknolojisinin gelişmesiyle birlikte, FPGA performansı ve kapasitesi yıldan yıla artmaktadır, ancak fiyatı ve güç tüketimi düşmeye devam etmektedir. Giderek daha fazla gömülü cihaz geliştirme, FPGA'yı optimum çözüm olarak benimsemektedir. Bu sefer tasarlanan edinim sistemi, Şekil 1'de gösterildiği gibi esas olarak FPGA, edinim modülü grubu ve Gigabit Ethernet iletişiminden oluşur.

Ana bilgisayar tarafından Gigabit Ethernet üzerinden gönderilen komut çerçevesi formatı Tablo 1'de gösterilmektedir ve veri aktarımının çerçeve formatı Şekil 2'de gösterilmektedir.

1.2 Edinim modülü tasarımı

1.2.1 Cihaz seçimi

Edinim modülündeki ADC yongasının seçimi, dönüştürme tipini, aralığını, çözünürlüğünü, örnekleme oranını, kanal sayısını, dinamik aralığını, giriş ve çıkış arayüzlerini ve diğer parametreleri dikkate almalıdır Tablo 2, mühendislikteki birkaç yaygın ADC yongasının performans göstergelerini listeler. Bu tasarım için ADI tarafından tanıtılan AD7768 yongası seçildi.

Mikrofonun çıkış voltaj sinyali genellikle ADC çipinin aralığından çok daha küçük olan milivolt seviyesinde olduğundan, edinim modülünün girişini yapmak için giriş voltajı sinyalini yükseltmek ve PGA çipini tüm alım sisteminin giriş aşaması olarak seçmek gerekir. Empedans 1 G'dan büyüktür ve farklı mikrofon türlerinin sinyal amplifikasyon gereksinimleri, PGA'nın kazanç katsayısı değiştirilerek esnek bir şekilde eşleştirilebilir. Tablo 3, birkaç yaygın PGA yonga performans göstergesini listelemektedir TI tarafından sunulan PGA4311 yongası seçilmiştir ve PGA'nın voltaj sinyali çıkışı, AD7768 yongasının diferansiyel giriş arabirimine uyması için LTC6363 yongası aracılığıyla tek uçludan farklılığa dönüştürülmüştür.

1.2.2 Ölçeklenebilirlik analizi

Edinim modülünün donanım yapısı Şekil 3'te gösterilmektedir ve FPGA tarafından tüketilen toplam G / Ç kaynağı sayısı 16'dır. Şekil 2'den, tek bir edinim modülünün her ağ paketinin 42 B sabit başlık, 4 B çerçeve başlığı, 4 B paket sayısı ve 4 B CRC kontrolünü işgal ettiği görülebilir Tek bir modül, bir örnekte, ana bilgisayar tarafından gerekli olan 32 B veriye sahiptir. Bir datagram, M edinim modülleri tarafından eş zamanlı olarak N kez örneklenen verileri içerir, ardından bir paket göndermek için T zamanı:

Donanıma bir edinim modülü ekleyerek ve denklem (2) ve (3) 'e göre tek bir iletim için AD örnekleme oranını fs ve edinme noktalarının sayısını N ayarlayarak, ayarlanabilir kanal sayısı gerçekleştirilebilir. Örneğin, fs 125 kHz olarak ayarlanmışsa, 128 kanal eşzamanlı olarak toplanırsa (M = 16) ve bir datagram 8 toplanan veri içeriyorsa (N = 8), gönderme süresi T = 33,2 s elde edilebilir ve N kez arabelleğe alma süresi 64'tür. s, kanal genişletme koşullarını karşılayan 256 G / Ç tüketir.

2 Yazılım tasarımı ve uygulaması

Program akış şeması Şekil 4'te gösterilmektedir. Program, ana bilgisayar ile FPGA arasındaki Gigabit Ethernet iletişimini, FPGA'nın ana bilgisayar talimatlarına yanıtını ve doğrulamasını ve toplanan verilerin yüksek hızlı önbelleği ve gerçek zamanlı yüklemesini uygular.

2.1 Talimat doğrulama modülü tasarımı

FPGA, Ethernet saat sinyalinin yükselen kenarı ile senkronize ederek veri yolunu sürekli olarak yargılar.Bu modülün mantık simülasyonu dalga formu Şekil 5'te gösterilmektedir ve fonksiyonlar aşağıdaki gibidir:

(1) Ana bilgisayarın global başlatma talimatını tanıyın ve global etkinleştirme sinyalini (en_glob) "1" e ayarlayın, ardından global durdurma talimatı alındığında, global etkinleştirme sinyalini temizleyin;

(2) Ana bilgisayarın PGA yapılandırma talimatını tanımlayın, PGA'nın yapılandırma etkinleştirme sinyalini (en_pga_w) "1" olarak ayarlayın ve yapılandırma bilgilerini "pga_data" kaydına kaydedin ve PGA yapılandırması tamamlandıktan sonra etkinleştirme sinyalini "0" olarak ayarlayın ";

(3) Ana bilgisayarın ADC kayıt yapılandırma talimatını tanıyın, ADC yapılandırma etkinleştirme sinyalini (en_adc_w) "1" ayarlayın ve yapılandırma bilgilerini "adc_addr_data" yazmacına kaydedin ve ADC yapılandırması tamamlandıktan sonra etkinleştirme sinyalini temizleyin.

2.2 PGA kontrol modülü

PGA4311 yongası, SPI arabirimi aracılığıyla FPGA yongasıyla veri etkileşimini gerçekleştirir. Basamaklı PGA yongasını yapılandırırken, ilk PGA için kazanç katsayısını iki kez arka arkaya yapılandırmanız gerekir.PGA kanal kaydı tarafından veri L (1 ~ 255 ondalık) girişi ile gerçek kazanç katsayısı K arasındaki ilişki denklem (4) 'te gösterilmiştir. Gösterilen:

PGA kontrol modülü tarafından uygulanan işlevler aşağıdaki gibidir:

(1) Edinim sistemi, üst bilgisayar tarafından verilen genel etkinleştirme komutunu aldığında, alt bilgisayarın varsayılan yapılandırma işlevini gerçekleştirmek için tüm kanallara onaltılık sayı "C0" yazar;

(2) Sistem, ana bilgisayar tarafından gönderilen çevrimiçi modifikasyon komutunu tanıdığında, belirtilen parametreleri PGA yongasına yazar ve bekleme komutu durumuna geri döner.

Şekil 6'daki mantık simülasyon diyagramında gösterildiği gibi, ilk olarak global etkinleştirmeden sonra, 8 kanalın kazanç katsayılarının varsayılan konfigürasyonu iki SPI iletişimi yoluyla tamamlanır ve ardından her bir kanalın çevrim içi kazanç kayıtlarını değiştirme işlemleri iki kez gerçekleştirilir.

2.3 ADC kontrol modülü

AD7768 yongasının veri çıkış formu Şekil 7'de gösterilmektedir, burada "DRDY" sinyalinin frekansı ADC'nin örnekleme oranını temsil eder ve FPGA her "DCLK" nın düşen kenarına göre "DOUT" u okur.

Şekil 8, sistem 125 kHz örnekleme hızında çalışırken tek bir edinim modülünün ADC kanalı 7'nin verilerini okuyan FPGA'nın gerçek mantık dalga biçimi diyagramıdır. "AD_Data_Valid" sinyali FIFO'nun yazma saati sinyali olarak kullanılır. Ek olarak, "ad_go" arka seviye Ethernet'tir. İletim, iletimin darbesini etkinleştirir.

2.4 Gigabit Ethernet kontrol modülü

Gigabit Ethernet kontrol modülünün ana işlevleri aşağıdaki gibidir:

(1) ARP protokolü, ana bilgisayarın MAC adresini ve IP adresini alır ve önbelleğe alır;

(2) UDP protokolü, komut geri beslemesini ve veri aktarım işlevlerini gerçekleştirir;

(3) ICMP protokolü aracılığıyla ağ bağlantısının gerçek zamanlı olarak açılıp açılmadığını gözlemleyin.

Ana bilgisayar, ağ paket yakalama testi için edinim sistemine 18 B "AA" gönderir ARP yanıtı ve komut yanıt fonksiyonları Şekil 9'da gösterilir; ana bilgisayar, DOS sistemini kullanır ve ICMP protokolünü test etmek için ping komutunu girer. Sonuçlar Şekil 10'da gösterilir. Gösterildi.

3 performans göstergesi

3.1 Dönüşüm doğruluğu

DC voltajını girin ve AD örnekleme oranını 125 kHz olacak şekilde yapılandırın, PGA kazancı 0 dB'dir ve edinim sistemi tarafından karşılık gelen voltaj değeri V çıkışının hesaplanması formül (5) 'de gösterilmiştir:

Bunlar arasında VD, AD7768'in çıkış tamamlayıcı formudur, Vref 4.096 V referans voltajıdır. Edinim modülünün 8 kanalının ölçüm sonuçlarının ortalama değeri, USB-4431 edinim kartı tarafından ölçülen sonuçlarla karşılaştırılır ve edinim modülünün dönüştürme hatası Tablo 4'te gösterilir.

Formül (4) 'e göre, PGA kazancını 20 dB ve 31.5 dB olarak ayarlayın ve edinim modülüne karşılık gelen dönüştürme sonuçları Tablo 5'te gösterilmektedir.

3.2 Kendinden gürültü ve dinamik aralık

Alma modülünün girişini analog toprağa kısa devre yapın, PGA kazancını 0 dB olarak yapılandırın, farklı çalışma modlarında ve farklı örnekleme oranlarında edinim modülü tarafından ortalama gürültü tabanı Vrms çıkışını ölçün ve denklem (6) 'ya göre dinamik aralığı DR'yi hesaplayın:

Test sonuçları Tablo 6'da gösterilmektedir.

Üst bilgisayar, toplama modülünün arka plan gürültüsü ve USB-4431 edinme kartının arka plan gürültüsü üzerinde güç spektrumu analizi gerçekleştirir ve karşılaştırma sonucu Şekil 11'de gösterilir.

3.3 Üst bilgisayar dalga biçimi ekranı

Alım modülünün kanal 0 ve kanal 7, sinyal kaynağı üzerinden 5 kHz frekanslı, 90 ° faz farklı ve tepeden tepeye 7 V'luk bir sinüs dalgası giriyor ve örnekleme hızı 125 kHz olarak yapılandırılıyor ve ana bilgisayar, gigabit ağ portu üzerinden gerçek zamanlı olarak alıyor Veri toplayın ve dalga formu görüntüleme sonucu Şekil 12'de gösterilmektedir. Bunlar arasında, kanal 0 edinim verileri kesikli bir çizgi ile temsil edilir ve kanal 7 edinim verileri, düz bir çizgi ile temsil edilir.

4. Sonuç

Bu makale, akustik kameraların geliştirme gereksinimlerini analiz eder, mühendislikte yaygın olarak kullanılan IC yongalarını karşılaştırır, düşük gürültü ve genişletilebilir kanal sayısı perspektifinden FPGA tarafından kontrol edilen bir veri toplama sistemini inceler ve tasarlar ve modülerleştirir ve modülleri ayrıntılı olarak detaylandırır. Tasarım sürecinde modül genişletme koşulları ve performans test göstergeleri verilir. Mevcut bitmiş ürün edinme kartı USB-44311 ile karşılaştırıldığında, bu sefer tasarlanan edinim modülü daha yüksek dönüştürme doğruluğuna, daha düşük kendi kendine gürültüye, daha geniş dinamik aralığa ve kolay genişlemeye sahiptir, bu da birçok geliştirme maliyetinden tasarruf sağlar ve akustik kameralarda edinim sisteminin gereksinimlerini karşılar. Geliştirme gereksinimleri.

Referanslar

Qian Shie Akustik Kamera-Topluluğumuzu Sessizleştirin Yabancı Elektronik Ölçüm Teknolojisi, 2009, 28 (2): 5-8.

BUXTON R T, LENDRUM P E, CROOKS K R, vd.İnsan rahatsızlığının ekolojik etkisini izlemek için kamera tuzakları ve akustik kayıt cihazlarının soyulması. Global Ekoloji ve Koruma, 2018, 16: e00493.

Shao Lin, Yang Diange, Li Bing, vd.Dürbün görüş ve ses dizisine dayalı akustik kameranın geliştirilmesi. Chinese Journal of Scientific Instrument, 2009, 30 (4): 823-827.

CAE Yazılım ve Sistem.Akustik kamera biyonik M-112 dizisi. (2010-xx-xx) .https: //www.cae-systems.de/produkt-e/akustische-kamera-schallquellen-lokalisieren/bionic-m-112 .html.

DE BREE H, TIJS E, BASTEN T. Yakın alan, uzak alan ve soğurucu yüzeylerde gerçek zamanlı ses alanı görselleştirme Akustik 2008, Paris, Fransa, 2008.

Yüksek teknoloji KeyVES-U yüksek performanslı dizisi. (2016-xx-xx). Http://www.keygotech.com/cn/product/acoustic

He Di. FPGA tabanlı ses kaynağı yerelleştirme sistemi yazılımı ve donanım tasarımı Harbin: Harbin Institute of Technology, 2017.

Ren Yong, Hu Fangming, Li Zixue Mikrofon dizisine dayalı ses kaynağı konumlandırma sisteminin FPGA uygulaması Elektronik Bilim ve Teknoloji, 2011, 24 (4): 72-74.

Hu Demeng, He Peiyu, Zhang Yong, vb. Gerçek zamanlı yüksek hassasiyetli mikrofon dizisi veri toplama sistemi Sinyal işleme, 2013, 29 (10): 1362-1367.

Yi Zhiqiang, Han Bin, Jiang Hong, vd.Çok kanallı eşzamanlı gerçek zamanlı yüksek hızlı veri toplama sisteminin FPGA tabanlı tasarımı.Elektronik Teknoloji Uygulaması, 2019, 45 (6): 70-74.

Zhao Shulei, Liu Jingmeng, Zhang Hui, vd.FpGA'ya dayalı bir havadan veri toplama sisteminin tasarımı.Elektronik Teknoloji Uygulaması, 2018, 44 (12): 123-126.

Zhou Hao, Wang Haoquan, Ren Shilei.FpGA ve NAND Flash'a dayalı taşınabilir bir sinyal toplama sisteminin tasarımı.Elektronik Teknoloji Uygulaması, 2018, 44 (9): 82-86.

Zhang Zhijian, Zhou Fengxing, Lu Shaowu. AD7760'a dayalı yüksek hızlı veri toplama sistemi. Enstrümantasyon Teknolojisi ve Sensörler, 2015 (1): 24-26.

yazar bilgileri:

Tian Haowen, Guo Shixu, Zhu Mengqi, Zhao Peng

(Ölçüm Mühendisliği Okulu, Çin Jiliang Üniversitesi, Hangzhou 310018, Çin)

-

- Otobüse binerken lütfen şu üç noktayı unutmayın: gerçek isim kaydı, yeşil kod erişimi ve tarama kodu