Yüksek Güvenilirlik, Yüksek Hız ve Programlanabilir Asenkron FIFO Tasarımı

Modern büyük ölçekli ASIC tasarımında, genellikle farklı saat alanlarında veri aktarım sorunlarına neden olacak çok saatli sistem kontrol yöntemleri kullanılır. Farklı saat alanlarında veri iletiminin arabelleğe alınmasını gerçekleştirmek için asenkron FIFO (İlk Giren İlk Çıkar) kullanmak daha iyi bir çözümdür. Bunun nedeni, eşzamansız FIFO'nun verileri yalnızca işaretçinin artan sırasına göre yazması ve harici okuma ve yazma adres satırlarına ihtiyaç duymadan verileri aynı sırayla okumasıdır, kullanımı çok basittir, böylece farklı saat alanlarında veri iletiminin zamanlamasını yapabilir. Gereksinimler daha gevşek hale geldi ve aralarındaki aktarım verimliliği de iyileştirildi. Bu nedenle, asenkron FIFO, ağ iletişimi ve dijital bilgi işleme gibi alanlarda geniş bir uygulama alanına sahiptir. Yüksek performanslı asenkron FIFO araştırması, büyük ölçekli entegre devre tasarımı alanında araştırma sıcak noktalarından biri haline geldi ve birçok araştırma sonucu elde edildi.

Örneğin, literatürde, eşzamanlı işaretçileri karşılaştırma yöntemi, metastabilite olasılığını azaltmak için benimsenmiştir.Bu, karşılaştırma sırasında iki işaretleyicinin eşzamanlı olmasını sağlar.Ancak, büyük kapasiteli bir FIFO tasarlarken, okuma ve yazma işaretçileri Çok fazla bit ile senkronizasyon modülü, tasarım maliyetini büyük ölçüde artıracak ve iş verimliliğini azaltacak çok sayıda kayıt kullanacaktır. Dahası, yazıda bahsedilen tasarım şeması, işlem sırasında okuma ve yazma işaretçilerinin göreceli konumunu belirlemek için bir adres biti ekledi Bu sadece çok fazla mantık kaynağı gerektirmekle kalmadı, aynı zamanda FIFO kontrol sisteminin taşınabilirliğini de azalttı. Literatür, Gray kodunun ilk iki basamağını yargılayarak ve ardından dolu veya boş olup olmadığına karar vererek depolama aralığını bölme yönteminden bahsetmektedir, ancak bu yargı aralığı bölme yöntemi donanım biçiminde uygulandığı için iyi değildir. Yerli bir FPGA'nın yonga tasarım gereksinimlerini karşılamak için bu tasarım, yüksek güvenilirlik sağlama öncülüğünde asenkron FIFO'nun programlanabilirliğini daha da geliştirir ve programlanabilen Gray koduna dayalı bir asenkron FIFO önerir ve Eşzamansız işaretçi karşılaştırma yöntemini birleştirerek, devrenin çalışma hızını ve verimliliğini artıran ve son olarak yüksek güvenilirlik, yüksek hız ve programlanabilirliğe sahip yüksek performanslı bir eşzamansız FIFO devre yapısı tasarlayan yeni bir boş-dolu yargı standardı önerilmiştir. .

1 Önerilen asenkron FIFO sistem yapısı

Önerilen asenkron FIFO tasarım fikri, geleneksel FIFO modülüne dayalı olarak devre yapısının iyileştirilmesi ve optimizasyonu ve durum yargı temelinde güvenilirlik, programlanabilirlik ve hızda bir atılım elde etmektir. Geleneksel FIFO temel olarak okuma, yazma ve boş veya tam değerlendirme işlevlerine sahiptir.Harici bir okuma ve yazma adres satırı gerektirmez, bu nedenle kullanımı çok basittir, bu nedenle sıradan bellek gibi değil, yalnızca sıralı olarak veri yazabilir ve verileri sıralı olarak okuyabilir. Adres satırı, belirli bir adresi okumaya veya yazmaya karar verebilir. Bu tasarımda, boşa yakın bir dolu uyarı işlevi eklenmiştir.Kullanıcılar, uyarı eşiğini ayarlamak için FIFO'yu programlayabilir ve FIFO'nun programlanabilirliğini artıran FIFO'nun durumunu belirtmek için neredeyse boş ve dolmak üzere gösterge bitleri ekleyebilir. FIFO modülünün sistem yapısı şeması Şekil 1'deki gibi gösterilmiştir.

FIFO'nun tamamı dört modüle bölünebilir: depolama modülü, işaretçi oluşturma modülü, işaretçi karşılaştırma modülü ve bayrak oluşturma modülü. r_clk okuma saatidir; w_clk yazma saatidir; data_in yazma verisidir; data_out okunan veridir; ale_num neredeyse boş uyarı eşiğidir; alf_num neredeyse dolmak üzere uyarı eşiğidir; r_ptr okuma işaretidir; w_ptr yazma işaretidir; al_empty neredeyse boştur İşaret; al_full neredeyse dolu bir işarettir; boş boş bir işarettir; dolu dolu bir işarettir; alr_ptr neredeyse boş bir göstericidir; alw_ptr neredeyse dolu bir göstericidir.

Çift bağlantı noktalı SRAM, tamamen bağımsız iki okuma ve yazma bağlantı noktasına sahiptir.Kullanırken, veri_içine yazmak için bir bağlantı noktası ve veri_çıkışı okumak için diğer bağlantı noktasını seçebilirsiniz, böylece okuma işlemi ve yazma işlemi birbirinden bağımsız olur, bu da FIFO işlevini uygulamak için daha uygundur. Şekil 1'de görülebileceği gibi, bir FIFO tamamen bağımsız iki saat alanına bölünebilir, okuma saati alanı ve yazma saati alanı. Yazma işaretçisi modülü w_clk'ye göre w_ptr üretir ve alw_ptr oluşturmak için w_ptr üzerinde alf_num'u üst üste koyar.Bir yandan, w_ptr veri_in yazmak için depolama modülünü kontrol eder ve yazılan veriler r_ptr tarafından okunur.Diğer yandan, w_ptr ve alw_ptr işaretçi karşılaştırma modülüne girer ve okur Gösterici tarafından oluşturulan r_ptr alr_ptr ile karşılaştırılır ve karşılaştırmanın sonucu değerlendirme için bayrak oluşturma modülüne girilir ve boş, dolu, neredeyse boş ve neredeyse dolu bayrakları oluşturulur.FIFO boşsa, e_ptr'yi durdurun ve doluysa, w_ptr'yi durdurun.

Yukarıdaki sistem tasarımında, sistem işaretçilerinin birbirleriyle karşılaştırılması sürecinde verilerin güvenilirliğinin ve boş veya tam olarak karar verme sürecinde sistemin doğruluğunun sistem performansının iyileştirilmesini kısıtladığını görmek zor değildir. Bu nedenle, ikinci ve üçüncü bölümlerde, sırasıyla sistem işaretçisi karşılaştırmasının ve boş-dolu değerlendirmesinin tasarım şemaları ayrıntılı olarak açıklanacaktır.

2 Sistem işaretçisi karşılaştırması için tasarım şeması

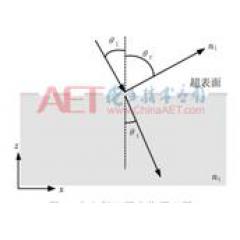

Veri iletimi sürecinde, alıcı kayıt değiştirilmiş verileri aldığında, veri değişikliği saat tetikleme kenarında meydana gelirse, alınan verinin kararsız bir durumuna yol açacaktır ki bu bir yarı kararlı durum olarak adlandırılır. Yarı kararlı duruma girerken, birimin çıktı seviyesini tahmin etmek imkansızdır ve çıktının belirli bir doğru seviyede ne zaman stabilize olacağını tahmin edemez. Bu kararlı dönem boyunca, bazı ara seviye çıktı olacaktır veya salınımlı bir durumda olabilir ve bu yararsız çıktı seviyesi sinyal kanalından aşağıya doğru kademelendirilebilir. Metastable durumunun meydana gelmesi, FIFO'da hatalara neden olacaktır ve okuma ve yazma saatleri tarafından örneklenen adres işaretçisi gerçek değerden farklı olacaktır, bu da yazma veya okuma adres hatasına neden olacaktır. Metastabilite tamamen ortadan kaldırılamaz ve yalnızca oluşma olasılığını en aza indirmenin yollarını bulabiliriz. Geleneksel FIFO devresinde, metastabilite problemini çözmek için benimsenen yöntem, işaretçi senkronizasyon modülünün kullanılmasıdır ve senkronize edilmiş işaretçiler arasında karşılaştırma için metastabilite problemi yoktur. İşaretçi senkronizasyon modülü genellikle Şekil 2'de gösterilen yapıyı kullanır. Clk1 ve clk2'nin eşzamansız saatler olduğunu varsayarsak, veri1'in değişimi B2'nin tetikleme kenarında meydana geldiğinde, veri2 yarı kararlı bir duruma sahip olabilir, ancak bu zamanda, B3 bir öncekini yarı kararlı durum olmadan yakalar ve gönderir. Veriler için, bir sonraki clk2 saati tetikleme kenarı geldiğinde, veri2 muhtemelen stabilize olmuş ve belirli bir 0 veya 1 değeri olacaktır. Bu durumda, B3 belirli bir değeri yakalar. Tabii ki, veri2 bir saat döngüsünde kararlı olmayabilir, ancak verilerin3 yarı kararlı durumunun olasılığı büyük ölçüde azalır.

Karşılaştırmalı senkronizasyon işaretçileri kullanma yöntemi oldukça güvenilir olmasına rağmen, FIFO'nun veri derinliği büyük olduğunda, işaretçiler genellikle birçok bit içerir, bu da her bitin senkronizasyonunu gerektirir, bu da kullanılan yazmaç sayısını büyük ölçüde artırır ve artırır Tasarım maliyeti.

Bu durum için Gray kod işaretçileri kullanmayı düşünün. Gri kod, iki bitişik kod öğesi arasında yalnızca bir bit tarafından dönüştürülür (çoğu durumda, ikili kodda, birçok kod öğesi aynı anda değişir). Bu, gösterge değiştiğinde yarı kararlılığı önleyecektir. Yazma adresi ve okuma adresi iletilmeden önce, verilerin kararlılığını iyileştirmek için, sayım için ikili kodun yerine Gray kod kullanılır. Bu durumda, işaretçi eşzamanlama modülünü kullanmak ve eşzamansız işaretçileri karşılaştırma yöntemini benimsemek, iki eşzamansız işaretleyiciyi doğrudan karşılaştırmak ve ardından karşılaştırmadan sonra elde edilen bayrak bitini istenen saat etki alanıyla eşzamanlamak gerekli değildir. Bu tasarımdaki işaretçi üretme modülünün şematik diyagramı Şekil 3'te gösterilmiştir.

İkili işaretçi oluşturma modülünün temel prensibi bir ikili toplama sayacıdır.Saatin yükselen kenarı her geldiğinde, bir önceki çıktı değerine bir ekler, böylece kademeli olarak biriken bir ikili işaretçi üretilebilir. Bu ikili işaretçi, yarım toplayıcıya girer. Neredeyse boş-doluluk karşılaştırması için bir ikili işaretçi oluşturmak için neredeyse boş-dolu uyarı eşiğine ekleyin Son olarak, her iki işaretçi de Gray kod oluşturma modülü tarafından Gri kod işaretçisi çıktısına dönüştürülecektir. Gri kod, yarı kararlı durum olasılığını azaltmak, mantık ek yükünü azaltmak ve tasarım maliyetini düşürmek için tasarımda kullanılır; işaretçi türü genişletilir ve FIFO'nun programlanabilirliğini iyileştirmek için neredeyse boş-doluluk uyarı eşiği ve neredeyse boş-dolu işaretçi eklenir. .

3 Boş veya tam karar için tasarım planı

FIFO'nun işlevi aynı anda okuma ve yazma ihtiyacı duyduğundan, aslında, FIFO'nun kapasitesi SRAM bellek dizisinin gerçek kapasitesine eşit değildir, ancak okuma işaretçisinin ve yazma işaretçisinin göreceli hızına bağlıdır. FIFO modülünün doğru kullanımı için ilk durum, yazma işaretçisinin okuma işaretçisinden önce olması gerekir, böylece okunan içeriğin yazılan veriler olmasını sağlayabilir.Bir okuma ve yazma süresinden sonra, okuma işaretçisi yazma işaretçisini yakalar ve okumaya neden olursa Yazma işaretçisi aynıdır, bu, içinde depolanan verilerin boş okunduğu ve ardından yanlış verilerin okunacağı anlamına gelir; yazma işaretçisi okuma işaretçisini yakalarsa, bu, hafızanın dolu olduğu ve devam ederse verilerin okunmayacağı anlamına gelir. Veriler yeniden yazılır. Yukarıdaki iki durumdan kaçınılmalıdır, bu nedenle boş veya dolu durumun nasıl değerlendirileceği FIFO'nun doğruluğu ve güvenilirliği ile ilgilidir.

Geleneksel yaklaşım, okuma ve yazma işaretçisinin göreceli konumunu belirtmek için bir adres biti eklemektir.Bu yöntem bir adres biti eklediğinden, FIFO adres bitlerinin sayısı, FIFO denetleyicisinin taşınabilirliğini azaltan SRAM adres bitlerinin sayısından farklıdır. Ve eklenen adres biti aslında gereksiz mantık ek yükünü artırır. Tasarımda bahsedilen FIFO'nun neredeyse boş dolu bir uyarı bayrağı eklediğini dikkate alarak, yakın uyarı bayrağı boş bir dolu bayrak oluşturmak için kullanılabilir. Devlet kararı ilkesi Şekil 4'te gösterilmektedir.

Neredeyse boş uyarı bayrağı bitinin oluşturulmasının ilkesi, uyarı eşiği olarak okuma ve yazma işaretçisine bir ikili sayı eklemektir, bu nedenle dört farklı işaretçi, yani okuma işaretçisi, yazma işaretçisi ve neredeyse boş okuma-yazma işaretçisi vardır. Bu dört işaretçi, istenen sonucu elde etmek için birbiriyle karşılaştırılabilir. FIFO kullanma sürecinde, boşa yakın dolu okuma işaretçisinin yazma işaretçisine eşit olması, okuma işaretçisinin hızının yazma işaretçisinin hızından daha hızlı olduğu anlamına gelir. İşaretçiler eşitse, FIFO okumasının boş olduğu yargılanabilir; boşa yakın dolu yazma işaretçisi okuma işaretçisine eşitse, bu yazma işaretçisinin hızlı olduğu anlamına gelir ve FIFO'nun neredeyse dolu olduğunu göstermelidir.Sadece dolu olma riski vardır. . Bu boş veya dolu değerlendirme yöntemi uyarı bayrağı bitini kullanır ve FIFO denetleyicisinin mantık kullanım oranını ve taşınabilirliğini geliştiren ek işaret bitleri eklemesine gerek yoktur.Ayrıca, çalışma hızını artıran yön bitleri üzerinde hesaplamalar gerektirmez.

4 Simülasyon doğrulama

Bu tasarım, UMC 28 nm standart CMOS sürecini temel alır ve devre tasarımı için tamamen özelleştirilmiş bir yöntem kullanır. Devre simülasyon doğrulaması, Hspice yazılımı kullanılarak gerçekleştirildi. Simülasyon sonuçları, önerilen asenkron FIFO'nun maksimum 666,6 MHz çalışma frekansına ve 1 V standart voltajda 7,1 mW güç tüketimine sahip olduğunu göstermektedir. Somut simülasyon sonucu Şekil 5'te gösterildiği gibi gösterilmektedir.

Neredeyse boş ve boş bayrak bitlerini doğrularken, kullanılan okuma saati döngüsü 1,5 ns (666,6 MHz), yazma saati döngüsü 2,5 ns (400 MHz), boşa yakın uyarı eşiği 17 olarak ayarlanıyor ve 9 bitlik bir ikili adres paylaşılıyor. , Gray kodu kanununa göre değişiklikler. Simülasyon sonucu, Şekil 5 (a) 'da gösterilmektedir. Şekilde, r_ptr, okuma işaretçisi sinyalidir, w_ptr, her ikisi de 3 basamaklı onaltılık bir sayı biçiminde ifade edilen yazma işaretçisi sinyalidir; boş, boş bir okuma sinyalidir (yüksek etkili); al_empty, neredeyse boş bir sinyaldir (düşük etkili). Boş okuma sinyalinin, okuma ve yazma işaretçileri eşit olduğunda geçerli olduğu ve FIFO'nun boş olmak üzere olduğu konusunda uyarmak için, boşa yakın sinyalin önceden 17 okuma döngüsü olduğu görülebilir.

Dolu ve dolu işaretleri doğrularken, okuma saati döngüsü 2,5 ns (400 MHz), yazma saati döngüsü 1,5 ns (666,6 MHz), boşa yakın uyarı eşiği 15 olarak ayarlandı ve 9 bitlik ikili adres paylaşıldı. , Gray kodu kanununa göre değişiklikler. Simülasyon sonucu Şekil 5 (b) 'de gösterilmiştir. Şekilde, w_ptr, yazma işaretçisi sinyalidir ve r_ptr, her ikisi de 3 basamaklı onaltılık bir sayı biçiminde ifade edilen okuma işaretçisi sinyalidir; tam, tam bir yazma sinyalidir (yüksek etkili); al_full, neredeyse tam bir sinyaldir (düşük etkili). Tam yazma sinyalinin, okuma ve yazma işaretçileri eşit olduğunda geçerli olduğu ve neredeyse dolu olan sinyalin 15 yazma döngüleri önceden FIFO'nun boş olmak üzere olduğu konusunda uyardığı görülebilir.

5. Sonuç

Geleneksel FIFO yapısının temelinde, devre yapısını ve durum değerlendirme temelini iyileştirip optimize ederek, yüksek performanslı bir asenkron FIFO devre yapısı önerilmektedir. UMC 28 nm standart CMOS sürecine dayalı devre tasarımı, simülasyon ve doğrulama. Simülasyon sonuçları, önerilen asenkron FIFO yapısının yüksek güvenilirlik, yüksek hız ve programlanabilirlik avantajlarına sahip olduğunu ve yerli FPGA yonga araştırma ve geliştirmesinin sistem gereksinimlerini karşılayabileceğini göstermektedir.

Referanslar

Jin Dachao, Leng Jianwei. Asenkron saat alanı sinyal senkronizasyonunun gerçekleştirilmesi.Tianjin University of Technology Dergisi, 2017, 33 (3): 40-44.

Liu Jie, Sai Jingbo DDR2 SDRAM ping-pong çift arabelleklemeye dayalı yüksek hızlı veri alıcı-verici sisteminin tasarımı Elektronik Cihazlar, 2015, 38 (3): 650-654.

Zhuang Hongyi. USB2.0 iletişim protokolünü gerçekleştirmek için FX2 ve FPGA tabanlı bir yöntem. Elektronik Ölçüm Teknolojisi, 2017, 40 (4): 78-81.

Feng Guofu, Ma Yuqi, Chen Ming, vb. Gemi ağları için bir "Beidou" asenkron FIFO çok kanallı modeli Mikroelektronik ve Bilgisayar, 2017, 34 (2): 1-5.

Wu Xiuying, Huang Songren. Kayan noktalı DSP'de asenkron FIFO'nun araştırılması ve tasarımı. Electronic World, 2018, 1 (69): 145-146.

Ni Lu, Zou Xueyu. LZW'nin asenkron FIFO giriş tampon tasarımı Elektronik Ölçüm Teknolojisi, 2015, 38 (4): 19-23.

Si Lanshan, Wu Haihong, Wang Yong, ve diğerleri.Büyük kapasiteli bir asenkron FIFO'nun tasarımı ve uygulaması. Microelectronics, 2013, 43 (3): 405-408.

Li Sai, Jiang Lin. OTN'de asenkron FIFO'nun tasarımı ve uygulaması. Optik İletişim Araştırması, 2015, 191 (5): 55-58.

Wang Qishuang, Huang Zhenchun, Pu Haifeng FPGA'ya dayalı asenkron FIFO'nun tasarımı ve performansı.Projeksiyonlar, Roketler, Roketler ve Rehberlik Dergisi, 2014, 34 (6): 185-189.

Xiao Jingxian, Dai Yawen FPGA'ya dayalı asenkron FIFO tampon tasarımı Elektronik Ölçüm Teknolojisi, 2009, 32 (11): 92-94.

yazar bilgileri:

Niu Bo, Zhao Hongliang

(Fizik Fakültesi, Liaoning Üniversitesi, Shenyang 110036, Liaoning)

-

- Büyük ağaçları yok etmek dişleri doldurmak gibidir. Bulmalı, delmeli, ilaçlamalı ve bir adım mühürlemelisiniz.

-

- "Çekirdek" ten "Bulut" a "AET Orijinal" Ligong Teknolojisi yeni bir stratejiye dayanır ve ardından yola çıkar

-

- Yan Qiang'ın okuması: Çin Süper Ligi'nin iki takımı Doğu Asya'da ilk dörde ulaştı ve gelecekteki gelişme beklenebilir.