Yeniden Yapılandırılabilir Blok Şifreleme için Çoklu İletim Hattı İşleme Mimarisinin Araştırılması ve Tasarımı

Ağ iletişim teknolojisinin gelişmesiyle birlikte, çipler askeri, ekonomi ve toplumda giderek daha önemli bir rol oynamaktadır. Blok şifreleme, önemli bir şifreleme algoritmasıdır ve verimli uygulanması, sistemin performansını doğrudan etkiler. Yeniden yapılandırılabilir dizi şifreleme işlemcisi, farklı şifreleme algoritmaları için optimize edilmiştir ve ASIC özel işlemcilerle karşılaştırıldığında yüksek esnekliğe sahiptir. Son yıllarda, blok şifreler için yeniden yapılandırılabilir işlem mimarileri üzerine giderek daha fazla araştırma yapılmıştır. Bu nedenle, blok şifrelerin paralellik ve boru hattı özelliklerinin tam olarak nasıl geliştirileceği ve yüksek performanslı, yeniden yapılandırılabilir bir blok şifreleme işleme mimarisinin nasıl tasarlanacağı, kriptografik uygulama teknolojisindeki önemli araştırma konularından biri haline gelmiştir.

Yurtiçi ve yurtdışındaki araştırmacılar, yeniden yapılandırılabilir blok şifrelerin verimli bir şekilde gerçekleştirilmesi üzerinde çalıştılar. Literatür, çok bankalı belleğe sahip yeni bir CGRA mimarisi önermektedir.Veriler birden çok bankada depolanmaktadır.Paralel erişim kapasitesi geliştirilmiş olmasına rağmen, bu makalenin ilgilenmesi gereken kaba taneli bit genişliğine uymadığından paralel gereksinimleri tam olarak karşılayamamaktadır. . Literatür, blok algoritmasının şifreleme performansını artıran, aritmetik birimdeki 5 seviyeli ve boru hattı yapısını tasarlayan ve uygulayan, yeniden yapılandırılabilir bir kümeleme blok şifreleme işleme mimarisi RCBCP önerir. Bununla birlikte, karmaşık yeniden yapılandırılabilir bilgi işlem birimi, kritik yolu büyütür ve bu da sistemin performansını belirli bir ölçüde sınırlar. Literatürde önerilen Cryptoraptor dizi yapısı işlemcisi, 80 PE işleme birimini entegre ederek CBC modunda DES algoritmasının verim oranını 6.4 Gb / s ve 2.67 Gb / s'ye ulaştırarak büyük kaynaklar tüketir.

Blok şifrelerin paralellik ve boru hattı özelliklerinden tam olarak yararlanmak için, bu makale ilk olarak Yeniden Yapılandırılabilir Çok Başlamalı Ardışık Düzen İşleme Mimarisi (RMPA) önermektedir. Bu mimariyi tasarlamanın amacı, atıl kaynakları azaltmak, böylece yeniden yapılandırılabilir hesaplama işlemcisinin kaynak kullanımını ve hesaplama verimliliğini artırmaktır. Ek olarak, yeniden yapılandırılabilir dizi sisteminin yüksek paralellik özelliklerini karşılamak için, bu makale aynı zamanda karşılık gelen bir çoklu aktarım veri yönetimi mekanizması önerir. Verimli veri yönetimi, yeniden yapılandırılabilir dizinin işlem performansını önemli ölçüde artırır.

1 RMPA ile yeniden yapılandırılabilir çoklu aktarım boru hattı işleme mimarisi

Yeniden yapılandırılabilir blok şifrelemeli çoklu aktarımlı boru hattı işleme mimarisi, RMPA, boru hattı teknolojisi ile birlikte ana bileşen unsur olarak PEs dizisine dayanır. Boru hattı yapısı, genellikle verimli hesaplamalarda kullanılan bir işleme yapısıdır. Blok şifrelerin temel işlemlerini analiz ederek ve bunları bir boru hattı yapısıyla işleyerek, birden çok veri boru hattında paralel olarak farklı işlemleri başlatabilir. Mimarinin temel fikri, çeşitli taneciklikteki kriptografik algoritmaları işlemek için 32 bitlik kaba taneli n × n-PEs dizisi kullanmak ve algoritmanın derinlemesine ardışık düzenini ve orta derecede paralel özelliklerini geliştirmektir.

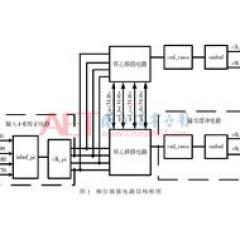

1.1 RMPA genel mimari tasarımı

Genel RMPA mimarisi Şekil 1'de gösterilmektedir ve bu yapı üç seviyeye ayrılabilir: RU (Yeniden Yapılandırılabilir Birim) işlevsel birim seviyesi, RE (Yeniden Yapılandırılabilir Öğe) dizisi seviyesi ve RMPA mimari seviyesi. RU işlevsel birimi, kriptografik işlem işlevini sağlayan anahtar bileşendir. Blok şifreleme algoritması işlem biriminin ayrıntılı analizine dayanarak, RU işlevsel birimi esas olarak aşağıdaki 7 işlemi gerçekleştirir: S-box, GF (2n) çarpma, kaydırma, modüler çarpma, Bit permütasyonu, mantık ve modüler toplama / çıkarma. Her RU, blok şifresinin çeşitli bit genişliklerini karşılayabilen kelime düzeyinde bir işlem gerçekleştirebilir ve her RE bir kayıt dosyası (Kayıt dosyası) ve bir yapılandırma kaydı (Yapılandırma Kaydı) ile eklenir, kayıt dosyası geçici verileri depolamak için kullanılır Ve ara sonuçlar. Yapılandırma kaydı, farklı bağlamları yapılandırarak sistemin işleme performansını iyileştirebilir. PE dizisi, Çapraz çubuk hiyerarşik ara bağlantı yapısı aracılığıyla n × n RE'lerden oluşur. RMPA mimarisi temel olarak bir ana kontrolör (Ana Kontrolör), bir konfigürasyon içerik kontrolörü (İçerik Kontrolörü), bir RE dizisi (Dizi), bir ana hafıza (Ana Hafıza), bir Banka hafızası (Bank Hafızası) ve bir anahtar hafızadan (Anahtar Hafıza) oluşur. Ana kontrolör tüm sistemi kontrol etmekten sorumludur. Ana bellek, yapılandırma bilgilerini ve verileri depolar ve verileri gerektiği şekilde yapılandırma modülüne veya Banka belleğine girer. Banka hafızası, işlenecek verileri ve işlenen verileri depolar ve bank hafızasına RE dizisi ve DMA kontrolörü tarafından erişilebilir ve DMA kontrolörü, ana hafıza ile bank hafızası arasındaki veri alışverişinden sorumludur. Anahtar bellek, algoritma tarafından oluşturulan alt anahtarı depolamak için kullanılır. Bu yapı, dinamik mod konfigürasyon bağlamını kullanır, her RE'nin içinde kendi konfigürasyon kaydı vardır ve konfigürasyon bağlam belleğine doğrudan bağlanabilir. Yapılandırma denetleyicisi, yerel yapılandırma belleğinden doğru bağlamı seçer ve ardından bunu her RE'nin yapılandırma yazmacına yazar.

1.2 Çoklu veri yolu ara bağlantı ağ yapısı

Bus, 2D-Mesh ve Crossbar ara bağlantı yapıları çoğunlukla dizideki işlem birimlerinin satırları ve sütunları arasında kullanılır. Aksine, otobüs ve 2D-Mesh'in maliyeti daha düşük olmasına rağmen, esneklik açısından Crossbar'dan uzaktırlar. Paralel işlemeyi daha verimli hale getirmek ve ara bağlantı ağının karmaşıklığını azaltmak için bu belge, Çapraz çubuk ağı temelinde bir çoklu veri yolu ara bağlantı ağ yapısını benimser.

Şekil 2'de gösterildiği gibi, Banka belleği ve dizi arasında bir çoklu veri yolu ara bağlantı ağ yapısı benimsenir. Aynı sütundaki RE'lerin bir veri yoluna bağlanması gerekir ve herhangi bir sütunun veri yolu herhangi bir kümeye bağlanabilir. Bu ara bağlantı ağı, her PE'nin herhangi bir kümeye erişebilmesini ve herhangi bir kümedeki verilerin girilebilmesini sağlayabilir. Fonksiyonel birimde; her katmanın verileri katmanlar arasında iletilebilir ve işlenen veriler Banka hafızasına veya anahtar hafızaya çıkarılabilir. Bu ara bağlantı ağı yapısı, mimarinin CBC geri bildirim modunda kriptografik işlemleri esnek bir şekilde desteklemesini sağlar.

2 RMPA mimarisi çoklu başlatma mekanizması

RMPA mimarisinin çoklu aktarım mekanizmasının ilkesi, belleğin birden çok veri setini aynı anda diziye iletmesini sağlamak ve böylece sistemin işleme performansını etkili bir şekilde iyileştirmektir. Bu koşulu karşılayabilmek için, sadece bir veri çoklu aktarım yapısının tasarlanması değil, aynı zamanda veriyi depolayan banka için belirli gereksinimlerin olması gerekir. Çoklu aktarım yapısı, esas olarak bir veri dağıtım modülü ve bir veri indeksi listesinden oluşan Şekil 3'te gösterilmektedir. Veri dağıtım modülünün işlevi, yeniden yapılandırılabilir dizideki verilerin boru hattı gerçekleştirilmesini sağlamaktır; veri indeksi listesi, veri paketlerinin bütünlüğünü sağlamak için veri paketlerini ayırt eder.

2.1 RAM depolama yapısı

Çoklu aktarım araştırmalarına dayanarak, veri paketi depolama kaynaklarının dinamik tahsisinin nasıl gerçekleştirileceğini ve böylece donanım kaynaklarının israfını ve iş hacmindeki artışı nasıl azaltacağınızı düşünün. RAM, önemli bir banka kompozisyon yapısı olarak, esas olarak verilerin tamponlanmasını gerçekleştirmek için kullanılır.FIFO yapısının veri giriş ve çıkış işleminden farklı olarak, RAM, verilerin yazılması ve okunması için adrese güvenir ve veri okuma sırasının yazma sırası ile ilgisi yoktur. Bu nedenle, Şekil 4'te gösterilen çok portlu RAM yapısı oluşturulur.

Çok çıkışlı RAM yapısı, veri depolamanın temelini oluşturmak için kullanılır ve çıkış verilerinin kaynağı adres aracılığıyla seçilir. RAM adresi sürekli olduğundan, veri depolama sırasında verilerin sürekli depolanması sağlanabilir ve farklı veri paketleri adreslerle ayırt edilebilir, bu da veri paketlerinin enjeksiyonunu daha esnek hale getirir. Farklı uzunluklardaki veri paketlerinin paralel enjeksiyonunu ve bir sonraki veri paketinin dinamik yüklemesini sağlamak için, veri aktarım modülünün yapısı aşağıda ayrıntılı olarak incelenecektir.

2.2 Veri aktarım modülü yapısı ve dizin listesi

Veri aktarım modülü, yeniden konfigüre edilebilir dizinin boru hattı gerçekleştirilmesini sağlamak için temel teşkil etmektedir Önceki bölümde veri depolama modülü üzerinde yapılan araştırmaya göre, veri depolama modülü, çok çıkışlı bir RAM yapısı ile gerçekleştirilmektedir. Aynı zamanda, farklı veri paketlerinin uzunluğu farklı olduğu için, veri aktarım modülünün verileri bağımsız olarak paralel olarak işleme özelliğine sahip olması gerekir, böylece veri paketi uzunluğundaki farkın neden olduğu boru hattı kesintisinin oluşumunu azaltır.

Veri depolama modülünde, farklı veri paketleri, veri paketinin başlangıç adresi ve veri paketinin uzunluğu ile ayırt edilir. Veri aktarım modülünde, veri okumayı desteklemesi gereken başlangıç adresi ve uzunluğu dinamik olarak yapılandırılabilir. Bu nedenle, Şekil 5'te gösterilen veri aktarım modülünün temel yapısı oluşturulur.

Başlangıç kaydı, veri paketinin başlangıç adresini (temel adres) saklamak için kullanılır ve yapılandırılabilir sayaç, mevcut veri paketindeki verilerin ofset adresini oluşturmak için kullanılır.Ana adres ve ofset adresi, gönderilen akımı almak için toplayıcı tarafından eklenebilir Yeniden yapılandırılabilir dizinin veri adresi. Konfigürasyon kontrol modülü, başlangıç yazmacı ve konfigüre edilebilir yazmacı konfigürasyonunu gerçekleştirmek üzere, mevcut veri paketinin başlangıç adresini ve uzunluğunu elde etmek için paket başlığını okumak ve paket başlığını analiz etmek için kullanılır. Aynı zamanda, konfigürasyon kontrol modülü, veri depolama modülünün okuma imkanını da üretecek ve ilgili verileri veri depolama modülünden okumak ve yeniden konfigüre edilebilir dizide karşılık gelen konuma göndermek için veri adresiyle işbirliği yapacaktır.

Veri paketlerinin bütünlüğünü ve veri depolama modülünde depolanan veri paketlerinin düzgünlüğünü sağlamak için bu belge, görev eşlemesine dayalı bir veri paketi indeks mekanizması oluşturur ve uygulama için çoklu iletim yapısına paylaşılan bir veri paketi indeksi listesi ekler. Veri paketinin indeksi. Veri paketlerini ayırt etmek için, bu makale görev numarası ve veri paketi numarasına dayalı olarak bir veri indeksi listesi oluşturur Biçim tanımı Şekil 6'da gösterilmiştir.

Depolamayı kolaylaştırmak için bu makale paket indeks listesini 32 bit olarak tanımlar. 28'inci ila 31'inci bit, farklı görevleri ayırt etmek için kullanılan görev numarasını temsil eder.Toplam 4 bit, 16 adede kadar görevi destekleyebilir; 26'ncı ila 27'nci bit ayrılmış alanlardır; 20'nci ila 25'inci bitler, veri paketlerinin paket numaralarıdır. Aynı görevdeki farklı veri paketlerini ayırt etmek için kullanılır, toplam 6 bit, böylece tek bir görev maksimum 64 veri paketini destekleyebilir; ağ veri paketleri için uzunluk 64 ~ 1518 B aralığındadır, bu nedenle 1518 B tek olarak tanımlanır Bir veri paketinin maksimum uzunluğu için, tek bir veri paketinin uzunluğunu belirtmek için 9 bit kullanılabilir ve maksimum destek 2.048 B veridir; Bu makale veri aktarım modülünü tasarlamak için çok kanallı bir paralel yapı kullandığından, veri depolama modülü en az birden çok grubu barındırabilmelidir Veri paketinin uzunluğu, dolayısıyla bu makale, uygulama gereksinimlerini karşılamak için başlangıç adres uzunluğunu 11 bit olarak tanımlar.

2.3 Veri çoklu aktarım arayüz devre tasarımı

Veri girişi arayüz devresinin yapısı Şekil 7'de gösterilmektedir. Ana bilgisayar, şifrelenecek ve şifresi çözülecek uygulamayı farklı görevlere ayırır ve her görevdeki verileri farklı uzunluklardaki veri paketlerine böler. Veri paketi indeks listesi, veri paketi indeks listesi formatına göre oluşturulur ve veri paketi, veri depolama modülünde karşılık gelen adreste depolanır. Uygulama belirlendiğinde, her bir veri paketinin başlangıç adresi belirlenir.Depolama kaynaklarının tüketimini mümkün olduğunca azaltmak için veri paketi, veri kapsama göre veri depolama modülünde saklanır.Bir veri paketi tamamlandığında, Kapladığı depolama kaynakları serbest bırakılır ve ilgili depolama kaynakları üzerinde depolamanın üzerine yazılabilir. Bu süreç esas olarak üst bilgisayar tarafından gerçekleştirilir ve verilerin çatışmasız okunması ve yazılması, veri paketi işlem sürecinin planlanmasıyla gerçekleştirilir.

Giriş veri arayüzünün iş akışı aşağıdaki gibidir:

(1) Veri aktarım modülü, veri paketi dizin listesinden veri paketi dizinini okur, veri paketi dizinindeki veri paketinin başlangıç adresini ve uzunluğunu analiz eder, veri paketinin başlangıç adresini başlangıç kaydına yazar ve yapılandırır. Sayacın taşma değeri paket uzunluğuna ayarlanır;

(2) Veri gönderme modülü, veri paketinin okuma adresini ve okuma özelliğini üretir ve karşılık gelen sinyali veri depolama modülüne gönderir;

(3) Adres ve okuma etkinliğine göre, veri depolama modülü karşılık gelen verileri büyük taneli yeniden yapılandırılabilir dizinin karşılık gelen konumuna getirir ve çıkarır Aynı zamanda, yapılandırma kontrol modülü karşılık gelen yazma etkinleştirmesini üretir;

(4) Veri aktarım modülündeki konfigüre edilebilir sayaç taştığında, bir taşma sinyali üretilir ve konfigürasyon kontrol modülüne iletilir Konfigürasyon kontrol modülü, veri paketi indeksini sırayla veri paketi indeks listesinden okur ve işleme devam eder.

Girdi veri arayüzünün iş akışı, girdi veri arayüzünün veri paketi analizini, veri okumayı ve iletimi doğru bir şekilde uygulayabilmesini ve kaba taneli yeniden yapılandırılabilir dizide boru hattının sürekli ve doğru çalışmasını garanti eder.

3 Uygulama performansı karşılaştırması

Bu tasarım, RTL seviyesinde blok şifreleme algoritmasını tanımlamak için Verilog donanım tanımlama dilini kullanır, tasarımı simüle etmek için Quartus9.0 yazılım aracını kullanır ve donanım kaynak maliyetini elde etmek için 65 nm CMOS işlemi standart hücre kitaplığı mantık sentezini seçer. Doğrulama ortamı, donanım tasarım kodunu geçit düzeyinde bir ağ listesine dönüştürebilen ve belirli bir işlem altında standart bir birime eşlenebilen Synopsys'in DC (Tasarım Derleyicisi) mantık sentez aracını kullanır. Çalışmanın kararlılığını sağlamak için, RMPA'nın çalışma frekansı 350 MHz'e ayarlanmıştır Kapsamlı simülasyon sonuçlarına göre, RMPA'nın performansını daha kapsamlı bir şekilde değerlendirmek için, bu makale analiz için tipik blok şifreleme algoritması AES'i seçmektedir. RMPA ve diğer yeniden yapılandırılabilir yapılar arasındaki performans karşılaştırması Tablo 1'de gösterilmektedir. Bunlar arasında, RCBCP ve Cryptonite adanmış komut şifreleme işlemcileridir ve Celator, RCPA ve S-RCCPA yeniden yapılandırılabilir dizi şifreleme işlem yapılarıdır. Her işlem yapısında kullanılan süreçlerdeki büyük farklılıklar nedeniyle, her yapının alanı ve verimi dönüştürülür ve 65 nm CMOS sürecine göre karşılaştırılır.

Sonuçlar, RMPA çoklu iletim yapısının AES blok şifreleme algoritmasını verimli bir şekilde işleyebildiğini ve çıktı oranının diğer özel talimat işlemcilerinden önemli ölçüde daha yüksek olduğunu göstermektedir. Celator ve BCORE gibi diğer yeniden yapılandırılabilir dizi yapılarıyla karşılaştırıldığında, bu yapı, blok şifreleme algoritmalarının iş hacmine göre hala bir avantaja sahiptir.

4. Sonuç

Yeniden yapılandırılabilir dizilerde blok şifrelerinin ardışık düzeninden ve paralel özelliklerinden tam olarak yararlanmak için bu makale, blok şifreleri için yeniden yapılandırılabilir bir çok iletimli boru hattı işleme mimarisi, RMPA önerir. RMPA'nın 65 nm CMOS süreci altında mantıksal sentezi ve fonksiyonel simülasyonu yapılarak, AES algoritmasının bu mimari altında şifreleme performansı incelenmiş, tekli iletim / çoklu iletim verim oranları sırasıyla 0,9 Gb / sn ve 3,19 Gb / sn'ye ulaşmıştır. Diğer kriptografik işlemcilerle karşılaştırıldığında, bu mimari yüksek bir verim oranına, belirli bir performans avantajına ve daha iyi bir uygulama olasılığına sahiptir. Bir sonraki adım, gereksinimlere göre çoklu veri toplama mekanizmasını incelemek ve mimari sistemi analiz etmek ve karşılaştırmak ve geliştirmek için çeşitli blok şifreleme algoritmaları kullanmak olacaktır.

Referanslar

Jin Chenhui, Zheng Haoran, Zhang Shaowu ve diğerleri. Cryptography. Beijing: Higher Education Press, 2009.

Dai Leyu, Li Wei, Xu Jinfu ve diğerleri Görev odaklı çok çekirdekli kriptografik işlemci veri dağıtım mekanizması Bilgisayar Mühendisliği ve Tasarımı, 2015, 36 (1): 98-102.

CONG J, HUANG H, MA C, et al.CGRA'nın tamamen ardışık düzenlenmiş ve dinamik olarak birleştirilebilir mimarisi. 2014 IEEE 22nd Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2014.

KIM Y, LEE J, SHRIVASTAVA A, ve diğerleri.Kaba taneli yeniden yapılandırılabilir mimari için yüksek verimli veri haritalama. Entegre Devrelerin ve Sistemlerin Bilgisayar Destekli Tasarımında IEEE İşlemleri, 2011, 30 (11): 1599-1609.

Tao Meng, Zibin Dai Blok şifreleme işlemcisinin yeniden yapılandırılabilir kümeleme mimarisi.Elektronik ve Bilgi Dergisi, 2009, 31 (2): 453-456.

SAYILAR G, CHIOU D. Kriptografik işlemci: yüksek verimli yeniden yapılandırılabilir kriptografik işlemci 2014 IEEE / ACM Uluslararası Bilgisayar Destekli Tasarım Konferansı Bildirileri, 2015: 155-161.

Li Junwei, Dai Zibin, Nan Longmei ve diğerleri.Çok motorlu kriptografik SoC için paralel işleme teknolojisinin araştırılması ve tasarımı. Bilgisayar Mühendisliği ve Tasarımı, 2014 (7): 2312-2316.

BUCHTY R, HEINTZE N, OLIVA D. Cryptonite - yüksek bant genişliği uygulamaları için programlanabilir bir kripto işlemci mimarisi.Uluslararası Bilgisayar Sistemleri Mimarisi Konferansı, 2004.

FRONTE D, PEREZ A, PAYRAT E. Celator: çok algoritmalı bir kriptografik yardımcı işlemci. Uluslararası Yeniden Yapılandırılabilir Hesaplama ve FPGA Konferansı, IEEE, 2008.

Yang Xiaohui, Dai Zibin, Zhang Yongfu.Yeniden yapılandırılabilir blok şifre işleme yapı modelinin araştırılması ve tasarımı Bilgisayar Araştırma ve Geliştirme, 2009, 46 (6): 962-967.

Chen Tao, Luo Xingguo, Li Xiaonan ve diğerleri. Akış işleme çerçevesine dayalı yeniden yapılandırılabilir kümelenmiş blok şifreleme işleme yapısı modeli. Elektronik ve Bilgi Dergisi, 2014 (12): 237-244.

yazar bilgileri:

Xue Yuqian, Dai Zibin

(Bilgi Mühendisliği Üniversitesi, Zhengzhou 450001, Henan)

-

- İstatistik Bürosu: Ocak ayından Mart ayına kadar, ulusal gayrimenkul geliştirme yatırımı, yıllık% 7,7 düşüşle 216,3 milyar yuan oldu