SFDR> 63 dB 12 bit 6 GS / s yüksek hızlı dijitalden analoğa dönüştürücü, InP HBT tabanlı

Yüksek hızlı ve yüksek doğrusallık geniş bant dijitalden analoğa dönüştürücü DAC (Dijitalden Analoğa Dönüştürücü), modern geniş bant iletişim entegre devrelerinin önemli bir bileşenidir. 12 bit veya daha yüksek çözünürlük gerektiren ve gigahertz'in üzerinde bir örnekleme oranına sahip bir DAC için tercih edilen yapı, mevcut yönlendirme yapısıdır. Akım yönlendirmeli DAC'lerde tipik bir problem, sinyal frekansı arttığında, harmonik distorsiyonun da hızla artmasıdır.Çıkış empedansı dijital ile değişir ve asenkronize anahtarlamanın oluşturduğu aksaklıklar, SFDR'yi sınırlayan ana faktörlerdir. Anahtarlama sinyalini senkronize etmek ve dijital değişim sırasında çıkışı dengelemek için sıfır-dönüş çıkış teknolojisini kullanmak, ancak bu yine de sınırlıdır.Devre karmaşıklığındaki artış nedeniyle, anahtarlama sırasının sapması kaçınılmaz hale gelir ve sıfır dönüş teknolojisinin de küçük dirençli yükler için sağlanması zordur. Büyük genlik. Literatür, hataları rastgele dengeleyen ve böylece dinamik performansı geliştiren dinamik bir rasgele dengeli akım kaynağı seçme algoritması önermektedir. Literatür, DAC'nin dijital dönüşümü sırasında DAC çıkışını kısa devre yapmak için yüke paralel olarak bağlanan bir anahtar olan bir izleme zayıflatma tekniği önermektedir. Literatür, sıfıra dönüşü olmayan bir DAC'yi sıfıra dönüşlü bir DAC'ye dönüştürmek için bir deglitch (Deglitch) devresi kullanır, frekans bandını ikinci ve üçüncü Nyquist alanlarına genişletir ve dinamik aralığın iyileştirilmesini sağlar, ancak bu yöntem ilk Nyquist alanını azaltacaktır. Sinyal genliği ve dinamik performans ve daha sık seviye geçişine neden olur.

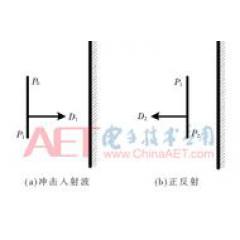

Bu makalenin DAC üzerine odak noktası esas olarak ilk Nyquist alanındadır. Kusur ve zayıflama problemlerinden kaçınmak için, DAC'den sonra bir örnekle ve tut devresi ekleyerek performansı artırmanın bir yolu olan çapak giderme elde etmek için bir örnekle ve tut devresi (THA) kullanabilirsiniz. Deglitch devresinde çapak giderme ilkesi Şekil 1'de gösterilmektedir. En iyi örnekleme anahtarı zamanlamasını seçerek Deglitch devresi, DAC'nin kararlı çıkış süresi boyunca DAC çıkışını izleyebilir ve analog çıkışı ortadan kaldırmak için DAC anahtarlama süresi boyunca örneklenen analog sinyal değerini koruyabilir. aksaklık.

Sahte Serbest Dinamik Aralık (SFDR), DAC çıkış sinüzoidal sinyalinin spektral saflığını ölçmek için kullanılır ve yüksek hızlı DAC çipleri için en kritik teknik göstergelerden biridir. Tüm Nyquist etki alanında iyi dinamik performans elde etmek için, bu makale Deglitch devresine sahip yüksek hızlı, yüksek çözünürlüklü, yüksek dinamik performanslı dijitalden analoğa dönüştürücü sunar.

1 Devre tasarımı

1.1 DAC genel mimarisi

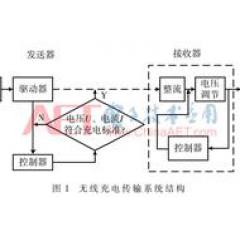

Şekil 2, DAC'nin genel yapısının bir blok diyagramıdır. Giriş veri sinyali ilk olarak bir LVDS (Düşük Voltaj Diferansiyel Sinyalleme) alıcısı tarafından dahili bir seviyeye dönüştürülür. Ardından 4: 1MUX (Multiplexer) girin ve bunu yüksek hızlı bir seri veriye dönüştürün. Saat çeyrek frekans sinyalinin faz ayarlama modülü (Seçici), farklı verilerin doğru örneklenmesini sağlamak için örnekleme penceresini ayarlamak için kullanılır. Segmentli bir akım dümen yapısının kullanılması, hız, devre ölçeği ve alan gibi parametrelerden taviz verebilir. 4 ila 15 termometre kod çözücü, en önemli 4 bit (MSB) için kullanılır, daha düşük 8 bit (LSB), gecikme tamponu aracılığıyla aynı gecikmeden sonra sonraki devreye girer ve 23 çift flip-flop, veri bitlerini yeniden hizalar ve veri işlemeyi gerçekleştirir HBT akım anahtarına uyum sağlamak için seviye kayması ve son olarak tüm sayılar yeniden ayarlanır ve mevcut kaynak anahtarı dizisine girilir. DAC'nin analog çıkışını yeniden örneklemek için yüksek doğrusallıkta bir Deglitch anahtarı DAC'nin analog çıkış ucuna yerleştirilir ve böylece devrenin dinamik performansını etkili bir şekilde iyileştirir.

1.2 DAC çekirdek devre gerçekleştirme

Mevcut dümen, yüksek hızlı DAC için en yaygın kullanılan yapıdır.Bu yapının gerçekleştirilmesi ikili ağırlıklandırma veya birim ağırlıklandırmaya sahiptir. Segmentli yapı, ikili kod ve sıcaklık kodunun avantajlarını birleştirebilir. Bölümleme noktası seçimi, esas olarak performans ve devre ölçeği arasında bir uzlaşmadır. "8 + 4" segmentasyonu kullanın, yani, düşük sekiz bit ikili kod kullanır ve yüksek dört bit termometre kodunu kullanır. HBT işleminde transistörün boyutunu değiştirerek farklı ağırlıklarda akımlar elde etmek zordur.Bu tasarımda düşük sıralı ikili ağırlıklandırma R-2R direnç merdiveni ile gerçekleştirilir.Direnç ağında sadece iki direnç vardır, R ve 2R eşleşmesi kolay. Bir sahte direnç eklemek, direnç etrafındaki elektromanyetik ortamı simetrik hale getirir. Şekil 3, DAC çekirdek devresinin uygulama blok diyagramını göstermektedir.

Diferansiyel çıkışlı bir güncel yönlendirme DAC'si için, ikinci harmonik genellikle iptal edilir ve üçüncü harmonik ana husustur.SFDR ile DAC'nin yüksek ve düşük frekanslardaki çıkış empedansı arasındaki ilişki şu şekilde ifade edilebilir:

SFDR esas olarak düşük frekanslardaki dirençten etkilenir ve sınırlı çıkış empedansı, çıkış akımının bir kısmını böler. Çıkış empedansını arttırmak için, akım anahtarı, diyot şeklinde bağlanmış iki transistörü üst üste bindirirken, bir kademeli yapı benimser. Yüksek frekanslarda, çıkış empedansı esas olarak kapasitans tarafından belirlenir.Parazitik kapasitans topraklaması nedeniyle, akım kaynağının çıkış empedansı yüksek frekanslarda azalacaktır.HBT işleminde, akım anahtarının açık ve kapalı durumdaki çıkış empedansı farklıdır, dolayısıyla çıkış Empedans, anahtarın durumuna göre değişir, bu da çıkış harmonik distorsiyonuna neden olur.Harmonik distorsiyonun büyüklüğü, çıkış empedansının açık ve kapalı durumu arasındaki empedans farkına bağlıdır.Bu nedenle, basitçe çıkış empedansını arttırmak SFDR'yi yüksek frekanslarda arttıramaz. Parazitik etkiyi azaltmak ve sinyalle birlikte değiştirmek için akım anahtarı her zaman açıktır. Literatür, her anahtar çıkış düğümünün çıkış empedansını dengelemek için bir çift küçük akım kaynağının eklendiği ve SFDR'nin güç tüketimi pahasına iyileştirildiği, normal olarak açık bir akım kaynağı yöntemi önermektedir.Bu makale, bu yöntemi mevcut kaynak yapısını iyileştirmek için kullanır.

Tüm Nyquist etki alanında iyi dinamik özellikler elde etmek için, parazitik kapasitansı azaltmak için akım kaynağı ve anahtar için küçük boyutlu transistörler kullanılır ve kas kod değiştirmeyi önlemek için akım anahtarının toplayıcısı arasına bir direnç R0 yerleştirilir. Tamamen kapalı, böylece açık ve kapalı durumlardaki çıkış empedansı arasındaki fark azaltılır. Şekil 4, iyileştirilmiş akım kaynak yapısından önce ve sonra SFDR'yi düşük ve yüksek frekanslarda karşılaştırmaktadır.SFDR'nin yüksek frekanslarda önemli ölçüde geliştirildiği ancak iyileşmenin düşük frekanslarda sınırlı olduğu, önceki teorik analizle uyumlu olduğu görülmektedir. Ek olarak, akım anahtar ünitesinin ön geriliminde, bitişik diferansiyel çiftler arasındaki paraziti azaltmak için direnç izolasyonu kullanılır. Son olarak benimsenen mevcut anahtar birimi Şekil 5'te gösterilmektedir.

1.3 Deglitch anahtarı

Yüksek hızlı DAC'nin dinamik performansı, esas olarak dijital ve analog sinyal yollarındaki zamanlama sapması ve DAC akım kaynağı anahtarındaki anahtar asimetrisi tarafından üretilen doğrusal olmayan arıza enerjisinden etkilenir. Zamanlama sapmasına yönelik yüksek gereksinimleri dengelemek için, DAC çıkışını yeniden örneklemek için birinci seviye bir örnekleme ve tutma devresi kullanılabilirken, sinyal çıkışını sürmek ve çip dışı test ekipmanını bağlamak için yüksek doğrusallık 50 çıkış tamponu kullanılır.

Bu makalede kullanılan çift anahtarlı THA'nın tek taraflı devre şeması Şekil 6'da gösterilmektedir. Örnekleme modunda, devre kontrol terminali Parça yüksek potansiyeldedir, Tutma düşük potansiyeldedir, Q3 ve Q9 açılır, örnekleme tüpü Q7 giriş sinyalini örnekler ve akım tutma kapasitörü CH'yi şarj eder. Tutma süresi boyunca, Q1 ve Q8 açılır ve giriş sinyali ile Q7 arasındaki yol bağlantısı kesilir, bu da tutma modunda besleme etkisini etkili bir şekilde bastırır. Devreye bir geri besleme aşaması da eklenir Tutma modunda, Q4, Q6 ve RL, tutma kapasitöründeki CH tutma voltajını Q7 anahtarının temel aşamasına geri beslemek için bir geri besleme dalı oluşturur ve örnekleme anahtarı Q7'nin girişindeki diferansiyel mod voltajını Anahtarlama sabittir ve iki diferansiyel terminali tutma moduna geçerken aynı voltaj dönüşümünden geçer, böylece geleneksel yapının temel hatası ve doğrusal olmayan distorsiyonu önlenir.

Şekil 7, ana işlevi sonraki devreyi izole etmek ve sürmek olan 50 çıkış tamponunun basitleştirilmiş bir devre diyagramıdır. Q3 ve Q4 transistörlerinin piyasaya sürülmesi, Q1 ve Q2'nin kollektör-verici voltajı Vce'yi sabit tutabilir, doğrusallığı artırabilir ve bozulmayı azaltabilir. Çıkış tamponu sadece sinyalin Nyquist alanında daha az zayıflamaya sahip olmasını sağlamalıdır.Çıktı tamponunun bant genişliği çok büyükse, sinyalin yüksek frekans hata harmonikleri düşük zayıflamayla çıkış ucuna iletilecek ve bu da SFDR'nin bozulmasına neden olacaktır. C0 kapasitörünün ve R0 direncinin eklenmesi, çıkış aşamasının giriş düğümüne, bant genişliğini azaltma etkisine sahip bir kutup ekler ve yüksek frekanslı harmoniklerin veya dağınık bileşenlerin Deglitch devresinin çıkışına iletimini bastırabilir, böylece devrenin doğrusallığını etkili bir şekilde iyileştirir.

Deglitch devresi, saat seçim devresi CMS tarafından kontrol edilebilir.CMS terminali topraklandığında, Deglitch tam Yol durumunda çalışır ve devre doğrudan moddadır ve doğrudan D / A çıkışını verir.

2 Simülasyon sonuçları

Devre, Nanjing Elektronik Cihazlar Enstitüsü'nün 0.7 m InP HBT sürecini kullanır. Devre 3,3 V / 5 V karışık güç kaynağı kullanır. Tüm çipin güç tüketimi 3,15 W ve Deglitch modülünün güç tüketimi 1,22 W'tır. Şekil 8, çip düzenidir.

Şekil 9, simülasyon sonuçlarından hesaplanan diferansiyel doğrusal olmama (DNL) ve integral doğrusal olmama durumunu (INL) göstermektedir. DNL 0,75LSB'ye ve INL 0,5LSB'ye ulaştı. Şekil 10, çıkış sinyali frekansı 2.97 GHz olduğunda simülasyon sonucunun frekans spektrumunu göstermektedir. Spektrogramdan, DA tarafından SFDR çıktısının 54.77 dB olduğu ve Deglitch yeniden örneklemeden sonra SFDR çıktısının 63.48 dB olduğu görülebilir, bu da SFDR'nin büyük ölçüde iyileştirildiğini gösterir.

DAC örnekleme hızı 6 GS / s'dir ve sinyal frekansı 120 MHz'den Nyquist frekansına yükseltilir Simülasyon sonucu, Şekil 11'de gösterildiği gibi DAC'nin Nyquist alanındaki SFDR'yi gösterir. DAC çıkış sinyalinin SFDR'si 120 MHz'lik düşük frekansta 71.11 dB'dir ve en kötü SFDR, yüksek frekansta 53.96 dB'dir. Deglitch devresi tarafından yeniden örneklendikten sonra çıkış, düşük frekanstan Nyquist frekans alanına 63 dB'den daha büyük SFDR'yi karşılayabilir. Yüksek frekanslı sinyaller verirken aksaklıklar genellikle ciddi olduğundan, yüksek frekanslı sinyaller için SFDR önemli ölçüde geliştirilir, ancak düşük frekanslarda fazla değildir. Degltch devresinin performans sınırlamasıyla sınırlı, düşük frekanslarda çıktı sonucu D / A'nın çıktı sonucundan daha düşük olacaktır.

Tablo 1, son yıllarda yurt dışında incelenen DAC yongalarının performans göstergelerini göstermektedir. Bu makalede tasarlanan DAC'nin, yüksek frekanslarda iyi dinamik performansı korurken yüksek hassasiyet ve yüksek örnekleme oranı elde ettiği görülebilir.

3 Sonuç

6 GS / s örnekleme hızına ve 12 bit hassasiyete sahip bir DAC yongası, 0.7 m InP HBT işlemi kullanılarak tasarlanmıştır. Bu DAC, çipin yüksek frekanslarda dinamik performansını önemli ölçüde artıran DAC analog çıkışını yeniden örneklemek için Deglitch devresini kullanır. Simülasyon sonuçları, SFDR'nin, 0,75LSB'lik bir DNL ve 0,5LSB'lik bir INL ile tüm Nyquist alanında 63 dB'den daha büyük olduğunu göstermektedir. Bu, DAC yüksek örnekleme hızı ve yüksek bant genişliği için yüksek kaliteli test cihazlarının uygulama gereksinimlerini karşılar.

Referanslar

PAL N, NANDI P, BISWAS R, vd. Diferansiyel akım yönlendirmeli DAC için yerleşim tabanlı doğrusal olmayan azaltma tekniği. Çok Büyük Ölçekli Entegrasyon (VLSI) Sistemlerinde IEEE İşlemleri, 2016, 24 (1): 233-242.

BEHZAD R. Mevcut yönlendirici DAC. IEEE Solid-State Circuits Magazine, 2018, 10 (1): 11-15.

TSENG W H, FAN C W, WU J T.A 12b 1,25 GS / s DAC, 90 nm CMOS'ta > 500 MHz'e kadar 70 dB SFDR IEEE Uluslararası Katı Hal Devreleri Konferansı, ISSCC 2011, Teknik Raporların Özeti, 2011.

PIRKKALANIEMI J, WALTARI M, KOSUNEN M, et al. Mevcut yönlendirmeli DAC'ler için akım modu deglitcher. 28. Avrupa Katı Hal Devreleri Konferansı Bildirileri, 2002.

Chen Chengying, Wang tercüme etti. Dinamik rastgele eşitlemeye dayalı mevcut dümen dijitalden analoğa dönüştürücü tasarımı. Elektronik Teknoloji Uygulaması, 2019, 45 (11): 27-31.

BUGEJA A R, SONG B S.A kendinden kesmeli 14b 100M Sample / s CMOS DAC.IEEE Uluslararası Katı Hal Devreleri Konferansı.IEEE, 2000.

OYAMA B, CHING D, THAI K ve diğerleri.InP HBT / Si CMOS Tabanlı 13-b 1.33-Gsps dijitalden analoğa dönüştürücü ile > 70-dB SFDR.IEEE Katı Hal Devreleri Dergisi, 2013, 48 (10): 2265-2272.

Wang Shuai, Huang Haisheng, Li Xin, vb. 10 bitlik 200MS / s segmentli akım dümen DAC tasarımı Elektronik teknoloji uygulaması, 2017 (4): 55-57.

LIN C H, GOES F, WESTRA J R, ve diğerleri. IM3 ile 12b 2.9GS / s DAC < < 65nm CMOS'ta 1GHz'in ötesinde -60dBc. IEEE Uluslararası Katı Hal Devreleri Konferansı Teknik Makalelerin özeti.

CHOE M J, LEE K J, SEO M, et al. DC-10GHz RF dijitalden analoğa dönüştürücü. Bileşik Yarıiletken Entegre Devre Sempozyumu. IEEE, 2011.

SANDE FVD, LUGIL N, DEMARSIN F, ve diğerleri 165 GHz f T BiCMOS işleminde bir yonga üzerinde 7.2 GSa / s, 14 Bit veya 12 GSa / s, 12 Bit sinyal üreteci. IEEE Journal of Solid-State Circuits, 2012, 47 (4): 1003-1012.

MCMAHILL D R, HURTA D S, BRANDT B, ve diğerleri 4.6 Gsps 14 bit DAC ile 160 kanallı bir QAM modülatörü. IEEE Journal of Solid-State Circuits, 2014, 49 (12): 2878-2890.

DUNCAN L, DUPAIX B, MCCUE J J, ve diğerleri. 10-bit DC-20-GHz çoklu-sıfıra dönüşlü DAC ile > 48-dB SFDR.IEEE Katı Hal Devreleri Dergisi, 2017, 52 (12): 3262-3275.

Euvis..http: //www.euvis.com.

yazar bilgileri:

Wang Ming 1, 2, Zhang Youtao 1, 2, 3, Ye Qingguo 2, Luo Ning 2, Li Xiaopeng 1, 2

(1. Nanjing Elektronik Cihazlar Enstitüsü, Nanjing 210016, Jiangsu; 2. Nanjing Guobo Electronics Co., Ltd., Nanjing 210016, Jiangsu;

3. Temel Mikrodalga ve Milimetre Dalga Monolitik Entegrasyonu ve Modüler Devreler Laboratuvarı, Nanjing 210016, Çin)

-

- İstatistik Bürosu: Ocak ayından Mart ayına kadar, ulusal gayrimenkul geliştirme yatırımı, yıllık% 7,7 düşüşle 216,3 milyar yuan oldu