1 GHz 6 GHz Geniş Bant ve Yüksek Doğrusallığa Sahip Faz Enterpolasyon Devresinin Tasarımı ve Uygulanması

Bazı yüksek hızlı çok kanallı seri alıcı-verici sistemlerinde, veri aktarım işlemi sırasında yalnızca veri sinyali iletilir ve veri sinyali ile senkronize edilen saat sinyali iletilmez.Saat veri kurtarma devresinin (CDR), veriden saati çıkarmak için alıcı uçta kullanılması gerekir ve Verilerin doğru örneklenmesini sağlamak için verileri yeniden planlamak. Bu nedenle, saat veri kurtarma devresinin performansı, yüksek hızlı seri veri iletişim sisteminin performansını doğrudan etkileyecektir. Günümüzde yaygın olarak kullanılan CDR sistemi çoğunlukla bir faz farkı cihazına dayalı dijital-analog hibrit bir yapı benimsemektedir.Küçük alan, iyi sağlamlık ve işlem geçişi kolaylığı gibi avantajları ileri teknoloji altında daha avantajlıdır. Bu nedenle, faz interpolatörünün performansı, saat fazı ayarlamasının gerçekleştirilmesinde hayati bir rol oynar.

Geleneksel enterpolasyon devresi iki diferansiyel çiftten ve yük direnci RL'den oluşur.MUX, herhangi bir açıda enterpolasyon elde etmek için giriş sinyalini seçmek için ikisinden birini seçer.Yapı basit olmasına ve alan tasarrufu sağlasa da, MUX sinyal strobe girişi, enterpolasyonu doğrudan etkileyen aksaklıklar getirecektir. Cihazın. Bu yazıda önerilen faz enterpolasyon şeması 4 diferansiyel çift, 4 set dijitalden analoğa dönüştürücü ve ortak yük direnci RL'den oluşan çekirdek enterpolasyon devresini kullanır.Giriş sinyalinde çıkış sinyali arızasını azaltan ve faz enterpolatörünü etkili bir şekilde iyileştiren ani bir değişiklik yoktur. Doğrusallık.

1 Devre yapısı

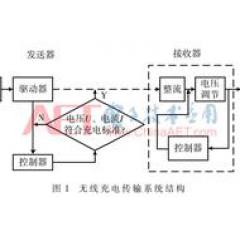

Faz enterpolasyon devresi, giriş 4 fazlı düzeltme devresi, çekirdek enterpolasyon devresi ve çıkış tampon devresinden oluşur ve yapısal blok diyagramı Şekil 1'de gösterilir. Giriş 4 fazlı saat, giriş tampon devresi tarafından yeniden şekillendirilir ve yükseltilir ve yeniden faz düzeltmesi, sabit orantılı analog enterpolasyon devresi tarafından gerçekleştirilir ve 4 fazlı saat, çekirdek enterpolasyon devresine girmek için oluşturulur.Burada, iki çekirdekli enterpolasyon devresi aynı anda 4 fazlı kareleme saati üretebilir. Aynı akım kontrol termometre kodları setiyle çıkışı farklı fazları ayarlayın, CML seviyesini seviye dönüştürme devresi aracılığıyla CMOS seviyesine dönüştürün ve 4 fazlı saat görev döngüsünü ayarlamak için çıkış arabellek aşaması ve çapraz bağlı invertör aracılığıyla sürücüyü artırın % 50 görev döngüsüne sahip 4 fazlı bir dört evreli saat alın

2 modül devre tasarımı

2.1 Giriş 4 fazlı düzeltme devresi

Ortak modun etkisini ve 4 fazlı saat sinyali çıktısının faz kilitli döngü tarafından genliğini ortadan kaldırmak için, giriş tampon devresi, bir AC bağlantı kondansatörü ve bir direnç bölücü aracılığıyla giriş 4 fazlı saat sinyalinin ortak modu için kendi kendine inşa edilir ve sinyal, bir diferansiyel amplifikatör tarafından güçlendirilir. Faz enterpolasyon devresi, her çeyrekte 32 eşit parçaya bölündüğünden, iyi enterpolasyon doğrusallığı sağlamak için, giriş saatinin 90 ° faz farkı sağlaması ve saat kenarını pürüzsüz hale getirmek için RC zaman sabitini artırması gerekir. Bu nedenle, 4 fazlı bir kareleme saati oluşturmak için yeniden faz düzeltmesi için sabit ağırlıklı bir analog interpolasyon devresi kullanılır Devre Şekil 2'de gösterilmektedir.

2.2 Çekirdek enterpolasyon devresi

Çekirdek enterpolasyon devresi, 90 ° farkla 4 fazlı saatler üretmek için kullanılan iki özdeş enterpolasyon devresinden oluşur.Çekirdek enterpolasyon ünitesinin devre yapısı Şekil 3'te gösterilmiştir. 4 diferansiyel çift, 4 set dijitalden analoğa dönüştürücü ve ortak Yük direnci RL, 90 ° farkla 4 fazlı giriş saatlerinden oluşur ve bir çift diferansiyel saat ara değeri hesaplanır ve çıkarılır. Faz kilitli döngü tarafından 8 fazlı saat sinyali çıkışı 4 diferansiyel çifte girilir (0-1, 2-3, 4-5, 6-7) ve dijital filtre çıkışları tamamlayıcı termometre kod kontrol DAC kılavuzlarını iki diferansiyel saat sınırına yönlendirir. Geçen akımın büyüklüğü, diferansiyel giriş saatinin faz ağırlık dağılımını tamamlar ve son faz saatini oluşturmak için enterpolasyon yapmak için RL yük direnci üzerinde hareket eder.

Faz kilitli döngü tarafından üretilen 8 fazlı saat, diferansiyel sinyaller biçiminde 4 diferansiyel çifte girilir ve bir saat döngüsü 8 çeyreğe bölünür ve saat fazı, Şekil 4'te gösterildiği gibi saat yönünün tersine artar. İki sınır diferansiyel saat çıkışı için tamamlayıcı termometre kodlarıyla herhangi bir saat fazı çıkışı oluşturmak için dijital bir filtre kullanılır. Bir sınır diferansiyel saatinin DAC kontrol kodu arttığında, diğer sınır saatinin DAC kontrol kodu karşılık gelen değeri azaltır, böylece ağırlık toplamı değişmeden kalır (ondalık 128), böylece enterpolasyon çıkış saatinin fazı sınırı aşmaz. Tablo 1, farklı çeyrek saatleri ve bunlara karşılık gelen giriş diferansiyel çiftlerini açıklamaktadır. 33 ° çıkış fazını örnek olarak alırsak, diferansiyel çifti 0-10 ° ve 180 ° saatlere, diferansiyel çifti 2-3 ise 90 ° ve 270 ° saatlere bağlıdır. Dijital filtre çıkışı DAC1'in kontrol kodu 0001100000'dir (ondalık olarak 96'ya karşılık gelir), DAC2'nin kontrol kodu 0000100000'dir (ondalık olarak 32'ye karşılık gelir) ve DAC3 ve DAC4 aynı anda kapanır ve enterpolatör çıkışının saat fazı 33 ° 'dir. Giriş saati, Tablo 1'de gösterildiği gibi olabilir. İkinci ünitenin ve birinci ünitenin giriş sinyalini 90 ° ara, ardından çıkış saat fazı 123 ° olup 4 fazlı diferansiyel saat çıkışını gerçekleştirir.

2.3 Çıkış tampon devresi

Faz enterpolasyon devresi tarafından üretilen sinyal ilk olarak bir birinci aşama tampon devresinden geçer, bir AC bağlantı kapasitöründen, bir direnç bölücüsünden ve bir diferansiyel amplifikasyon işleminden geçer ve ardından iki aşamalı sinyal amplifikasyonu ve sinyal koşullandırma, şekilde gösterildiği gibi CML seviyesini CMOS raydan raya seviyesine dönüştürür. 5 gösterilmektedir. Çıkış tamponu devresi, çıkış saat görev döngüsünü% 50'de tutmak ve kararlı bir giriş dörtlü saat sinyali sağlamak için iki aşamalı çapraz bağlı invertörler aracılığıyla sinyal yükselme ve düşme süresini ayarlar.

3 Fiziksel gerçekleştirme ve simülasyon sonuçları

40 nm CMOS sürecine dayalı olarak yerleşim, Candence ortamında tamamlanır. Tasarım yaparken, ortak mod gürültüsünü bastırırken ve sinyaller arasındaki paraziti azaltırken, diferansiyel yapının simetrik yönlendirmesine ve yüksek frekanslı sinyal hattına olabildiğince kısa dikkat edin. Düzen Şekil 6, fazda gösterilmiştir. İnterpolatörün genel devre boyutu 122 m × 255 m'dir.

Doğrusallık, faz interpolatörünün önemli bir teknik göstergesidir.Faz interpolatörünün sunacağı titreşimi belirler.Genel olarak iki gösterge ile ölçülür: İntegral Doğrusal Olmayanlık (INL) ve Diferansiyel Doğrusal Olmayanlık (DNL) . İnterpolatör devresini bir bütün olarak simüle etmek, faz enterpolatörünün mevcut kontrol kodunu değiştirmek ve 6 GHz'lik bir giriş saatiyle faz enterpolasyonunun monotonluğunu ve doğrusallığını simüle etmek için Candence Spectre aracını kullanın. Şekil 7, faz interpolatörünün doğrusallık eğrisini göstermektedir.Simülasyon sonrası sonuçlardan, interpolatörün çıkış saati fazının tekdüze olarak değiştiği ve periyodun sabit olduğu görülmektedir.İdeal faz eğrisi ile neredeyse tutarlıdır ve doğrusallık çok iyidir.

İnterpolatörün dinamik faz değişim sürecinde çalışma durumunu simüle etmek için, 32 bit DAC akım kontrol kodu oluşturmak için Verilog kodunu yazın, mevcut kontrol kodunu sırayla açıp kapatın, 0 ° 'den sağa hareket ettirin, kolay gözlem için en az 128 kez Faz interpolatörü bir döngüde değişir. Giriş saat frekansı 5 GHz Hesaplamayı kolaylaştırmak için, örnekleme saati 500 MHz'e ayarlanmıştır ve DNL ve INL hesaplamaları başlangıç noktası seçildikten sonra 150 kez gerçekleştirilir. Faz değişimi döneminde, faz 128 kez hareket eder Maksimum DNL 1.4 LSB'yi aşmaz ve maksimum INL 1.5 LSB'yi aşmaz, bu da interpolatörün faz kaymasının her seferinde yaklaşık 1 LSB olduğunu ve biriken faz değişikliklerinin periyodik olarak ortadan kaldırılabileceğini gösterir. Performans daha iyi.

4. Sonuç

Bu makale, 4 diferansiyel çift, 4 set dijitalden analoğa dönüştürücü ve ortak bir yük direnci RL'den oluşan yeni bir faz enterpolasyon devresini sunar Dijital filtre, DAC çıkış akımını kontrol etmek için iki sınır diferansiyel saate tamamlayıcı termometre kodları çıkarır. , Farklı diferansiyel çiftlerin giriş fazı saatlerinin ağırlık dağılımını tamamlayın, 128 fazlı enterpolasyon, yüksek enterpolasyon doğruluğu elde edin ve diferansiyel sinyali şekillendirmek ve optimize etmek için giriş aşaması 4 fazlı düzeltme devresini ve çıkış görev döngüsü ayar devresini kullanın. Devre, 40 nm CMOS teknolojisi kullanılarak gerçekleştirilir. Simülasyon sonuçları, enterpolatörün 1 GHz ila 6 GHz arasındaki çalışma frekanslarında iyi doğrusallığa sahip olduğunu gösterir.Maksimum DNL 1,4 LSB'yi aşmaz ve maksimum INL 1,5 LSB'yi aşmaz. Birçok SerDes devresine başarıyla entegre edilmiştir.

Referanslar

Jiao Yishu, Zhou Yumei, Jiang Jianhua ve diğerleri. Sürekli veri hızı CDR için uygun faz interpolatörünün geliştirilmesi. Entegre Devre Tasarımı ve Geliştirme, 2010, 35 (10): 999-1002.

Sun Yehui, Jiang Lixin. Saat veri kurtarma devresinde faz interpolatörünün analizi ve tasarımı. Chinese Journal of Semiconductors, 2008, 29 (5): 930-935.

YANG R J, CHAO K H, ve diğerleri 155.52 Mbit / s 3.125 Gbit / s sürekli oranlı saat ve veri kurtarma devresi IEEE Journal of Solid-State Circuits, 2006, 41 (6): 1380-1390.

Zeng Zecang, Deng Junyong, Jiang Lin.CDR devresi için faz enterpolasyon seçim devresinin tasarımı. Tümleşik devre tasarımı ve geliştirme, 2008, 33 (8): 721-725.

Hu Shijie, Jia Chen, HUANG K, vd. 65nm CMOS'ta kaynak senkron alıcı için faz interpolatörüne dayalı 10 Gbps'lik bir CDR. 2012 IEEE Uluslararası Devre ve Sistem Sempozyumu İşlemleri, Piscataway, NJ, ABD: IEEE, 2012: 309 -312.

Sun Yehui, Jiang Lixin. Saat ve veri kurtarma için bir faz interpolatörünün analizi ve tasarımı. Journal of Semiconductors, 2008, 29 (5): 930-934.

NICHOLSON A, JENKINS J, CHAIK A V, ve diğerleri. 65nm CMOS için 1.2V 2-bit faz interpolatörü.2012 IEEE International Symposium on Circuits and Systems (ISCAS), 2012: 2039-2042.

Niu Xiaoliang, Wang Zhengchen, Gui Xiaoyan, bir yüksek doğrusallık faz interpolatörü Mikroelektronik, 2016, 46 (4): 442-444.

Zhang Yao, Zhang Hong, Li Liang. Saat veri kurtarma devresinde doğrusal faz enterpolatörü. Xi'an Jiaotong Üniversitesi Dergisi, 2016, 50 (2): 48-54.

yazar bilgileri:

Liu Ying 1, Tian Ze 1, 2, Lu Junsheng 1, 2, Shao Gang 1, 2, Hu Shufan 1, Li Jia 1

(1. Xi'an Havacılık Hesaplama Teknolojisi Enstitüsü, Havacılık Endüstrisi, Xi'an 710068, Shaanxi;

2. Havacılık Teknolojisi Entegre Devre ve Mikrosistem Tasarımı Anahtar Laboratuvarı, Xi'an, Shaanxi 710068)

-

- Yeniden Yapılandırılabilir Blok Şifreleme için Çoklu İletim Hattı İşleme Mimarisinin Araştırılması ve Tasarımı

-

- Yüksek Yörünge SAR Sinyalinin GNSS Alıcısı Performansı Üzerindeki Etkisinin "Akademik Rapor" Değerlendirme Yöntemi